本篇文章是2022年第六届全国大学生集成电路创新创业大赛安谋科技杯三等奖作品分享,参加极术社区的【有奖征集】分享你的2022集创赛作品,秀出作品风采活动。

团队介绍

参赛单位:厦门大学

队伍名称:产教融合队

指导老师:郭子超、周剑扬

参赛队员:谭兴柏、王震、杨浩

总决赛奖项:三等奖

写在前面:

本次比赛的赛题是 “基于ARM处理器的无线SoC设计” ,在安路FPGA和射频板卡FM_SDR上设计无线SoC。我们在实现基本功能(在FPGA上内嵌Cortex_M0内核,FM电台播放,一键自动搜台,手动调台)的基础上,实现了部分拓展功能(全双工对讲、文件系统wav格式录音)。

此次比赛是我们小组研究生入学以来第一次参加比赛,属于新手,一路走来也是摸着石头过河,经验不多,教训不少。借此次机会简单分享一些经验教训,希望能对准备参赛的同学有所帮助。

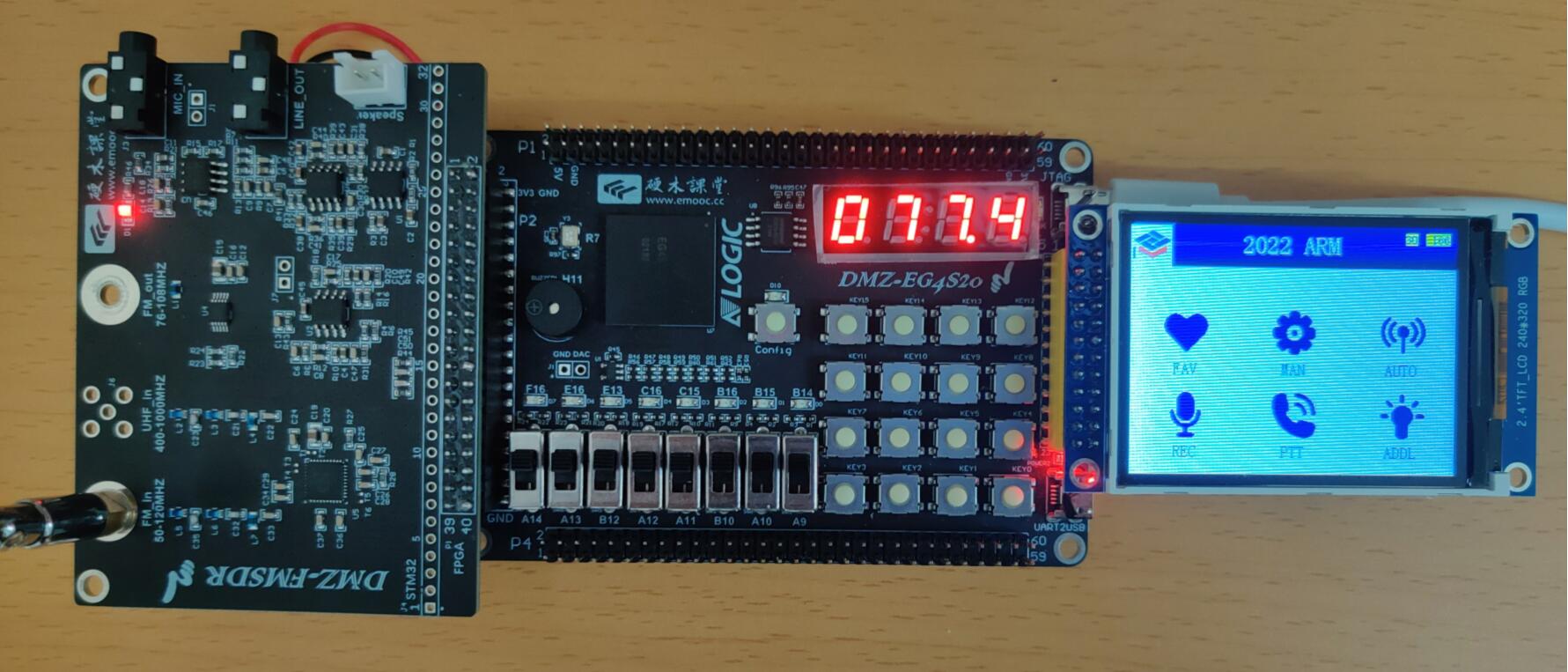

开发环境

系统由安路EG4S20的FPGA开发板、FM_SDR射频模块板,ILI9341液晶屏组成。FPGA开发软件为Anlogic TD 5.0.3,使用Keil5软件编写M0程序,并用DAP_LINK下载器下载软件程序。FPGA开发板搭载了4位数码管、16个矩阵按键、8个红色LED、8个拨码开关,JTAG仿真电路,USB转串口电路,无源蜂鸣器等。

1 作品简介

1.1 系统功能

目前系统有6个功能: 1,喜爱电台显示;2, 手动切换电台频率;3,一键自动搜台;4,LED展示(LED闪烁、流水灯);5,录音功能(电台WAV文件录音);6,全双工对讲

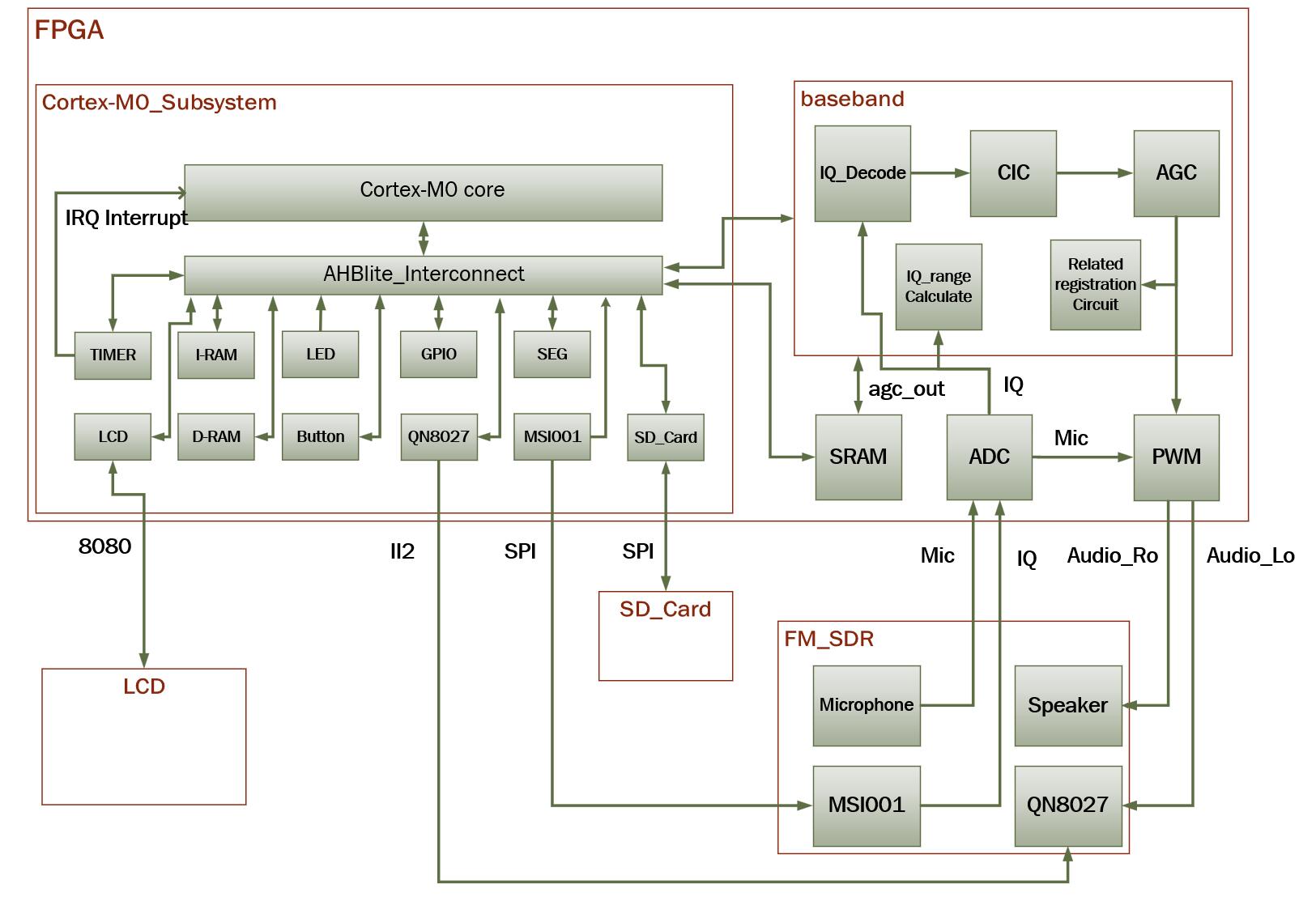

1.2 系统总体设计

在本设计中, 基带信号的解调和处理是实现的难点,也是设计指标能否达到的关键。虽然音频信号只有几十KHz的采样率,但是为了保障数字解调结果能够稳定收敛,必须得用采样率比音频高出好几倍的IQ数据去解算。 于是本设计根据音频采样率和ADC的硬件参数,设计了IQ信号采样率为500KHz。在这个采样率下,如果由处理性能不高的M0处理器执行软件解算的话,将会大大增加CPU的负担造成系统反应慢,甚至来不及解算造成声音卡顿失真。

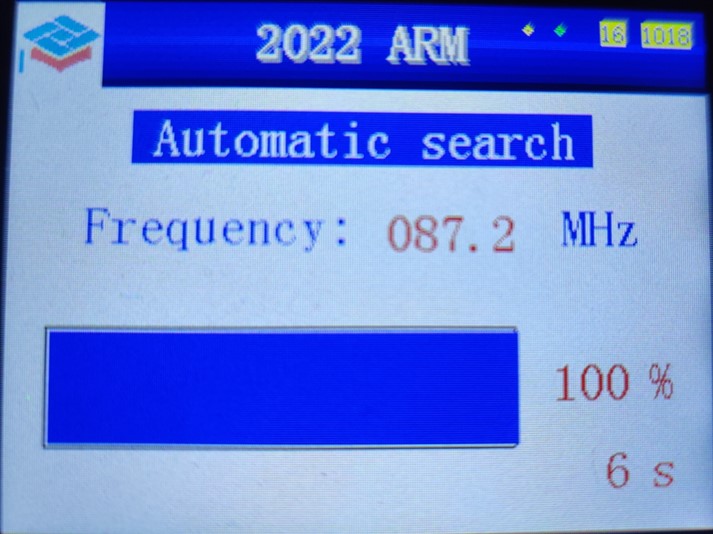

1.3 一键自动搜台设计

通过统计Q信号的平均幅值,以幅值大小作为判断当前频点是否有电台信号的依据,实现自动搜台,耗时6.30s。

1.4 全双工对讲机设计

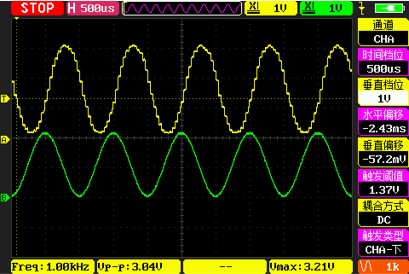

上图是我们使用qn8027发射1khz正弦波和msi001接收解调后的波形。

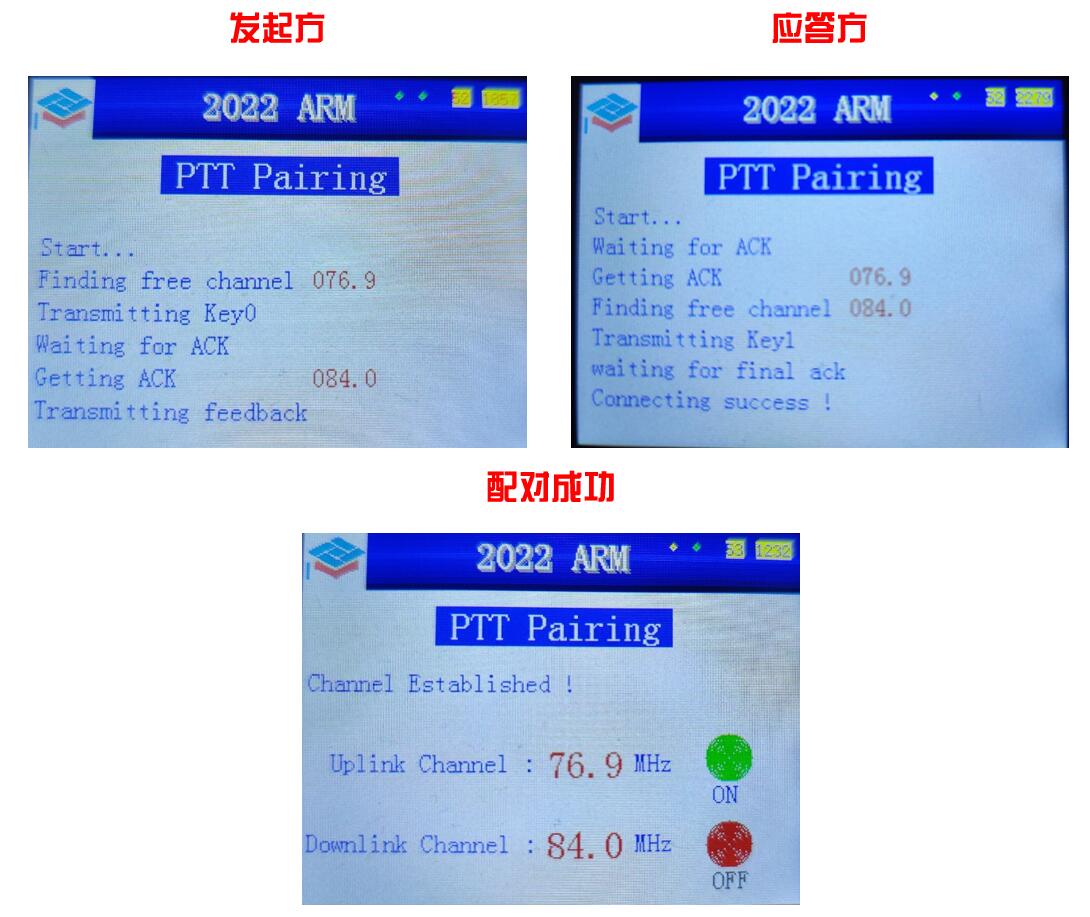

寻找空闲频段的相关匹配电路设计

对讲机配对过程界面

对讲机设计采用全双工通信,通过按键操作自动选择空闲的电台频道,发射1kHz正弦波信号,接收方采用设计的相关配准电路识别检测信号,完成对讲机的对码和进行实时对讲。

1.5 文件系统WAV格式电台录音

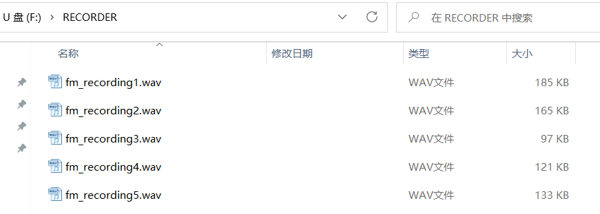

录音部分,我们使用基于SPI协议的SD卡作为音频信号录音存储的设备。设计真双口SRAM采用“乒乓模式”对音频数据进行缓存处理。我们实现了SD卡的WAV文件的读写可以在PC上实现音频数据的存储与回放,真正在整体实现了数据的有效保存与回放,使得数据可以达到最大化的利用,通过文件系统将有效音频数据保存为WAV格式。(详细设计过程见视频讲解)

pc端打开sd卡保存的wav文件

2 经验分享

2.1 内存问题

安路FPGA_EG4S20资源有限,M0内核的ROM和RAM不能设置太大。官方例程里面AHBRAM只能使用bram9k资源,并且td下载完上电不能初始化ROM,需要在keil上面重新下载软件才可以将软核跑起来,这有很大的局限性。因此,我们将其中代码进行了优化,充分使用bram9k和bram32k的资源,最后我们M0的ROM 64K, RAM 16K,勉强满足软件部分的内存消耗(主要内存消耗部分为文件系统、GUI)。(这里分享不了文件,嘤嘤嘤,如果同学们有需要,可以邮箱咨询784614953@qq.com)

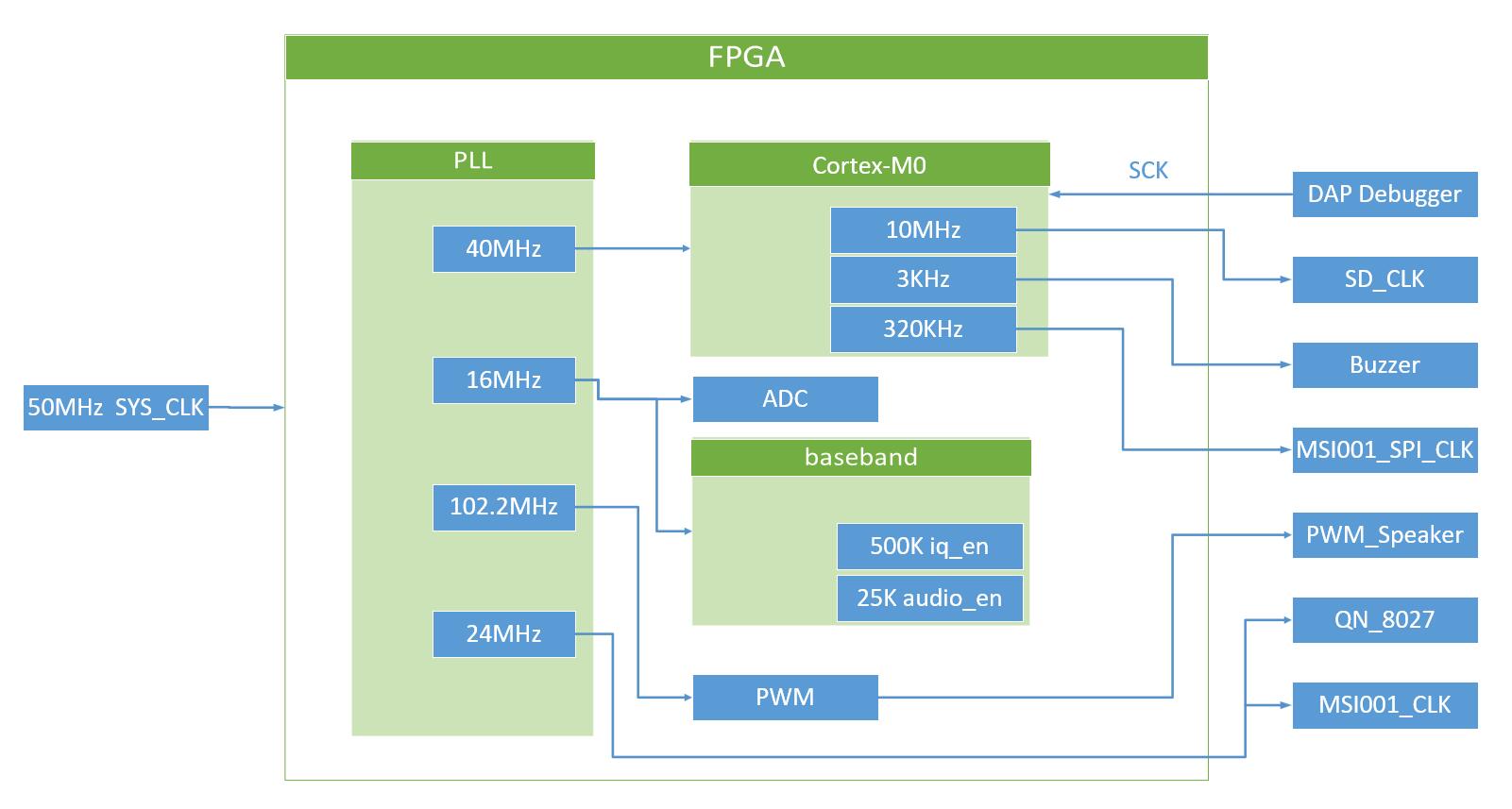

2.2 时序问题

时序设计也是FPGA编程的一个重点,我们在编程的时候往往没有关注的一个点。本次无线SOC设计对时钟要求很高,若时序不满足要求,将会导致实际时钟与设定频率不符,导致解调后声音失真。

2.3 td软件的常见问题

1、ctrl + c偶尔会卡住,需要耐心等待一下;

2、顶层文件编写出错时,若点击保存,则会自动将该文件设为非顶层,找不到bug的小伙伴注意啦;

3、使用chipwatcher工具检测电平时,有些引脚找不到。那是因为引脚被优化了,需要在定义引脚的后面加上“//synthesis keep”;

3 视频讲解和演示

视频讲解:

https://www.bilibili.com/vide...

作品演示:

https://www.bilibili.com/vide...

赶快来提交你的队伍的集创赛作品,让更多人看到你们的成果,更有丰富礼品给到每个队员。点击此处发布作品文章。