原文地址:https://vlsitutorials.com/jtag-architecture-overview/, 后附英文原文。

JTAG 是 Joint Test Action Group 的缩写,指的是开发 IEEE 1149.1 标准的开发小组。

JTAG 一般提供的功能是调试访问(Debug Access,通过 User Data Registers)和边界扫描(Boundary Scan,通过 Boundary Scan Registers)。

- 调试访问用于给调试工具(debugger)提供访问芯片内部的接口(比如访问芯片的寄存器,一些控制比特等等),通过配置这些寄存器或者比特,可以使芯片工作或者修改配置。

- 边界扫描用于在更大的子系统中实现层次化扫描,控制扫描时的主要输入数据,观察测试逻辑的主要输出,以优化提升扫描测试覆盖率。

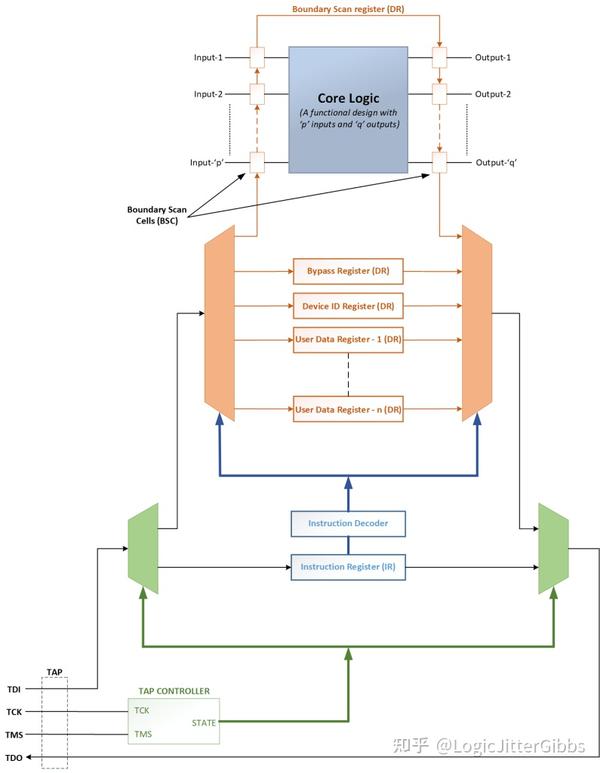

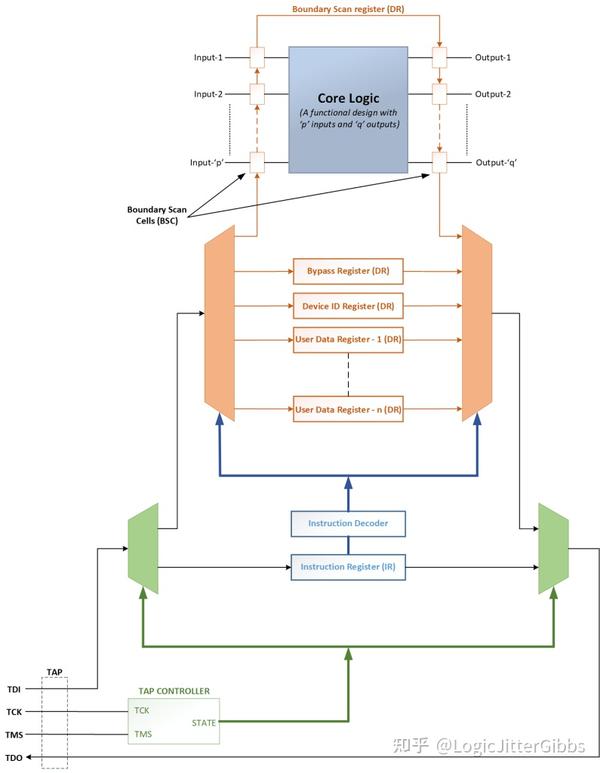

广义上的 JTAG 架构包括以下四个主要组件:

- Test Access Port (TAP) //测试访问接口

- TAP Controller // TAP 控制器

- Registers //寄存器

- Instruction Register //指令寄存器

- Data Registers //数据寄存器

- Bypass Register //旁路寄存器

- Boundary Scan Register //边界扫描寄存器

- Device ID Register (optional) // 可选的设备 ID 寄存器

- User Data Registers (optional) // 可选的用户自定义数据寄存器

- Instruction Decoder //指令译码器

Figure 1: JTAG 结构顶层架构

原文

JTAG is the acronym for Joint Test Action Group, a name for the group of people that developed the IEEE 1149.1 standard. The functionality usually offered by JTAG is Debug Access (through User Data Registers) and Boundary Scan (through Boundary Scan Registers) –

• Debug Access is used by debugger tools to access the internals of a chip (like registers, some control bits), while making its functionality available and modifiable.

• Boundary Scan is used to implement hierarchical scan in larger subsystems, control primary inputs and observe primary outputs for scan test coverage improvement.

Broadly JTAG architecture comprises of four major components

\1. Test Access Port (TAP)

\2. TAP Controller

\3. Registers

3.1. Instruction Register

3.2. Data Registers

3.2.1. Bypass Register

3.2.2. Boundary Scan Register

3.2.3. Device ID Register (optional)

3.2.4. User Data Registers (optional)

Figure 1: A top level view of JTAG Architecture

原文:知乎

作者:LogicJitterGibbs

相关文章推荐

更多FPGA干货请关注FPGA的逻辑技术专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。