INVS默认使用了BPG,但是基于SDC理论下PG(path group)也是天然存在,两者在数据库里边有各自存在的方式,也可以共融共生中,通过其中的异同,看到INVS的一些有趣的处理。

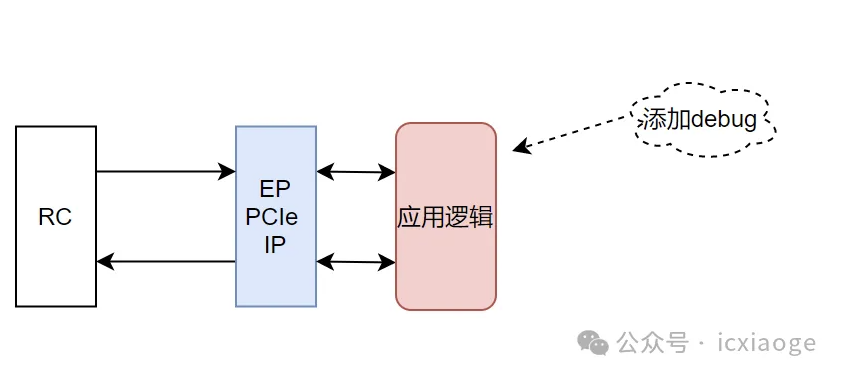

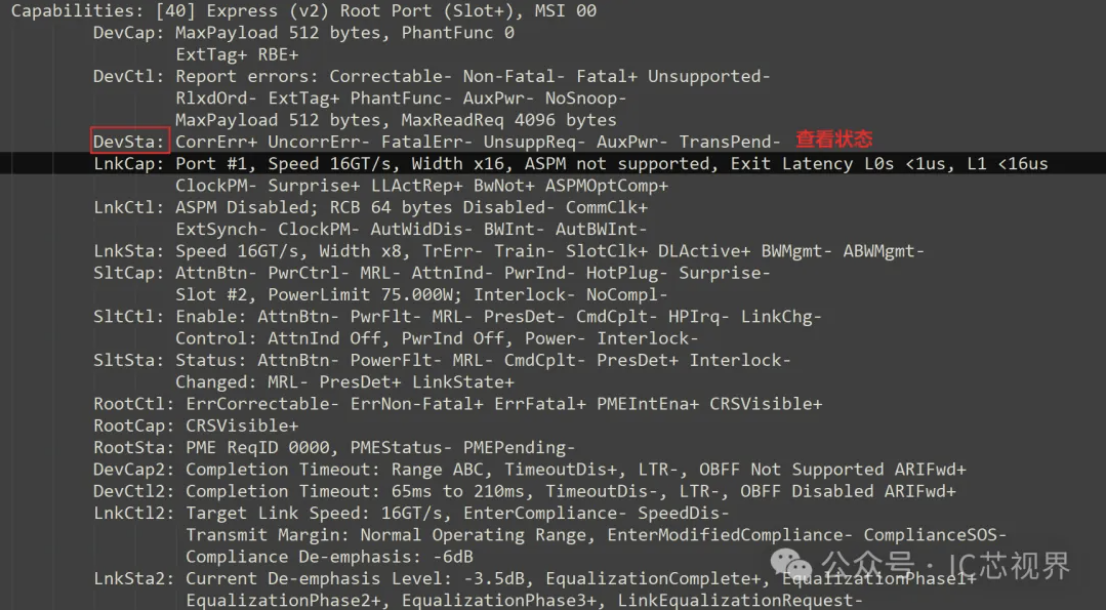

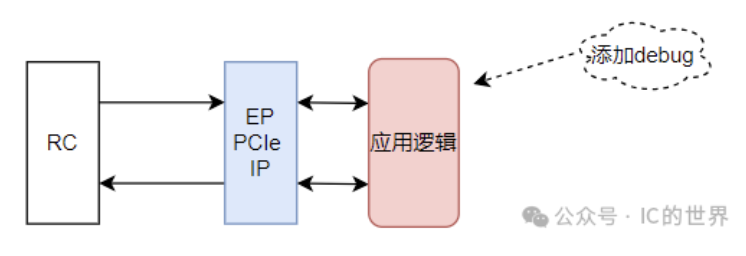

图1:debug设计添加位置图2:ltssm状态切换图pcie_ltssm作为PCIe链路训练状态机的实时状态,能够有效显示当前链路的链路状态。一旦PCIe出现问题,pcie_ltssm最近的数值跳变情况是进行分析的重要依据。本节采用移位寄存器实现了一种简单的锁存机制,能够锁存最近若干个(锁存个数已参数化)的数值。图3 pcie_ltssm_debug...

在所有的后端工具里边,有三个重要的引擎:auto-place,CTS,auto-route三个。这里边的auto-place是决断了整个设计时序的基点。由于,auto-place的动作是在设计的preCTS阶段,所以这里的设计时序就是广义上说的:数据路径(datapath)时序(timing )。当然,就算是到了CTS/route阶段后,也可以继续利用auto-place数据优...

ADPLL、ADLDO为何会出现?后续是否还会出现ADDC-DC、 AD-CLASSD等设计?我认为全数字锁相环和全数字LDO的出现是芯片设计中数字电路设计流程&方法和模拟电路设计流程&方法严重脱节的产物。

传说这个世界上只有代码三种编辑器,Vim , Emacs 和其他编辑器,其中Vim被称作编辑器之神,Emacs被称为神的编辑器,当然,其他编辑器永远只能是其他编辑器。

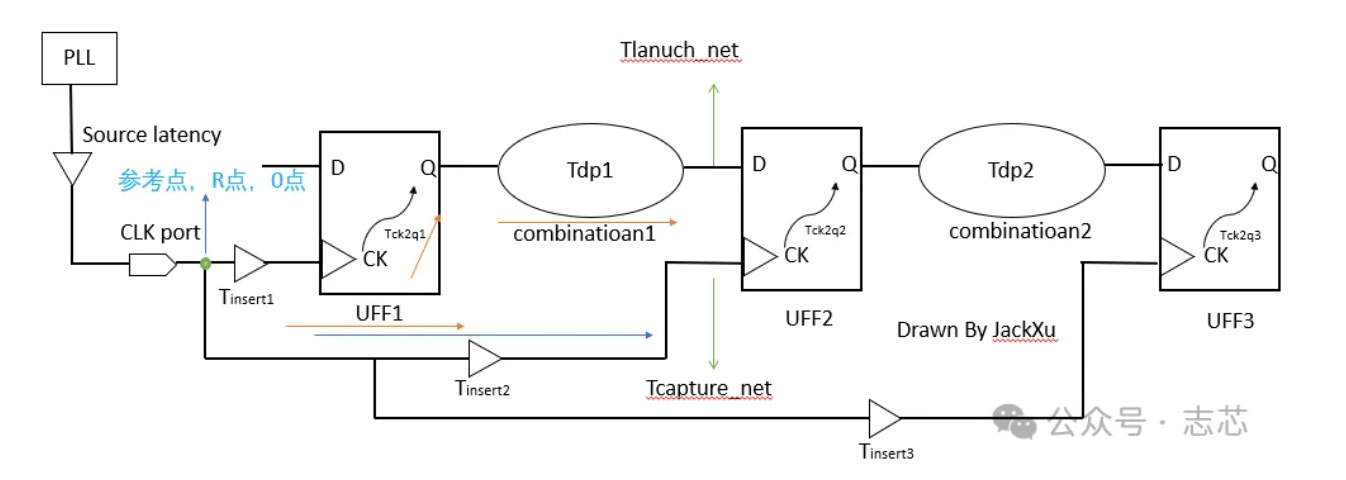

时序分析归根揭底就是时间窗分析,时序修复归根结底就是时间窗修复。如下图所示,是时序路径示意图,以UFF1→UFF2的路径为例;如果该路径既满足建立时间要求又满足保持时间要求,则等价于该路径需满足如下时间窗公式:Thold+ Tsetup < Tck2q1 + Tdp1+Tsetup + (Tlaunch_net - Tcapture_net )- Tclk_skew < Tcyc...

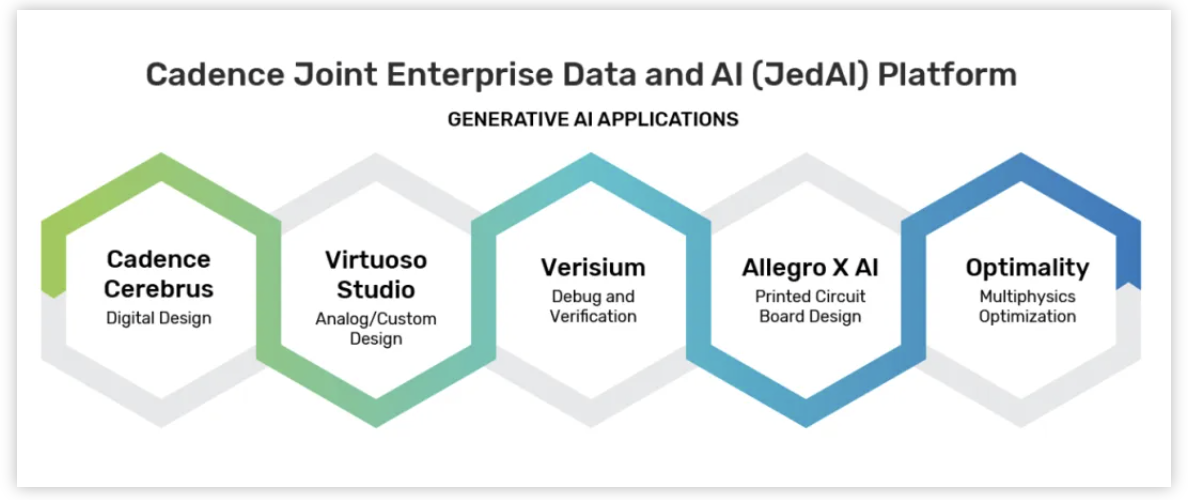

随着这几年AI应用和AI芯片的发展,AI已经成为市场的的热点,各个芯片公司均逐步推出具备特色的AI芯片以对市场进行争夺。当前的AI芯片快速发展,芯片设计复杂性呈现指数级增长。为了快速应对市场需求,并获得很好的PPA,使用AI辅助设计芯片已经成为主流趋势。今天我们盘点一下市场上的AI EDA工具。

当PCIe出现链路不稳定时,如何进行进行问题定位。本文描述的场景:EP PCIe 最高速率为gen4模式,ltssm状态机无法持续稳定在L0状态。

1680年,英国著名科学家牛顿首次提出喷气式汽车方案。至今,汽车经过长达三百年的发展,其动力来源已由最初的蒸汽、汽油变革到电力,性能指标也一步步飞速提升。然而,汽车的智能化进程却远远落后于消费电子。与传统汽车不同的是,智能汽车要求具有联接能力、感知能力、表达能力以及计算能力等四种基础能力,而这需要大...

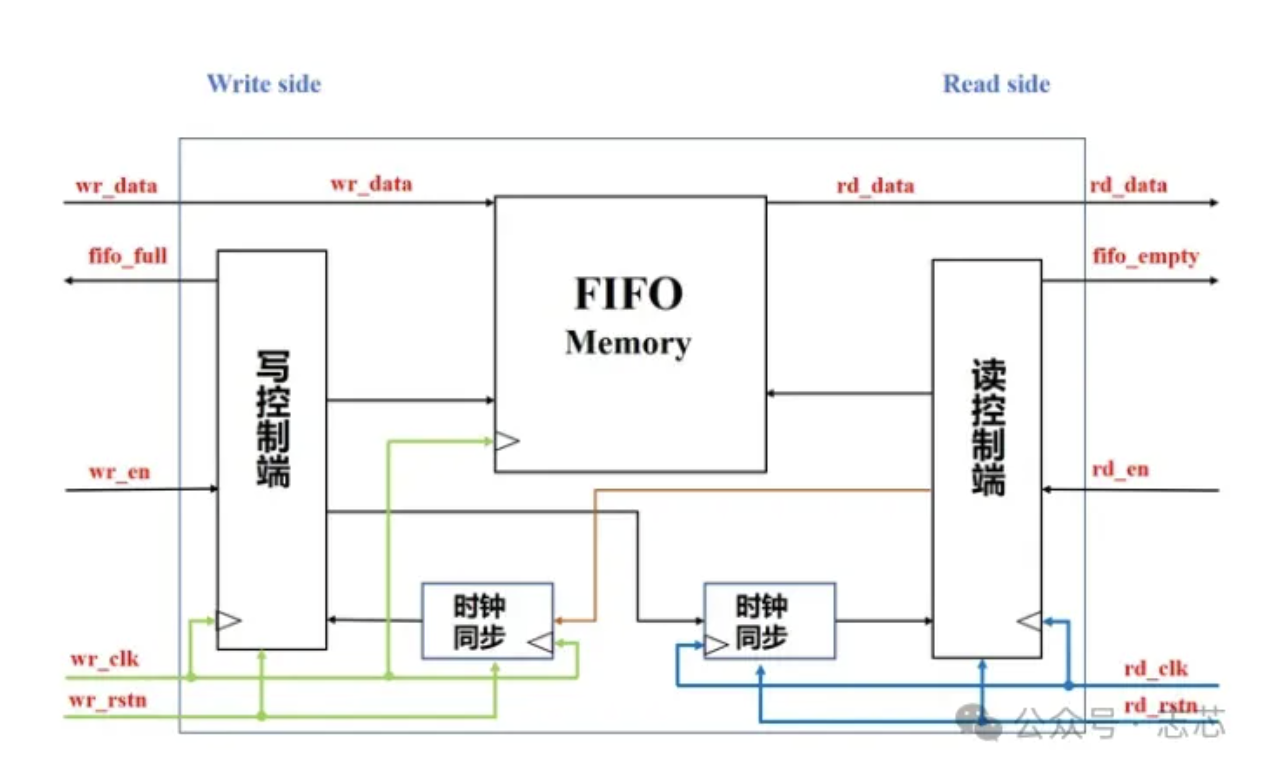

使用异步FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法。在异步FIFO中,读指针在读时钟域,写指针在写时钟域,所以不能单独运用一个计数器去产生空满信号了。因此,须要将写指针同步到读时钟域去产生空信号,将读指针同步到写时钟域去产生满信号。

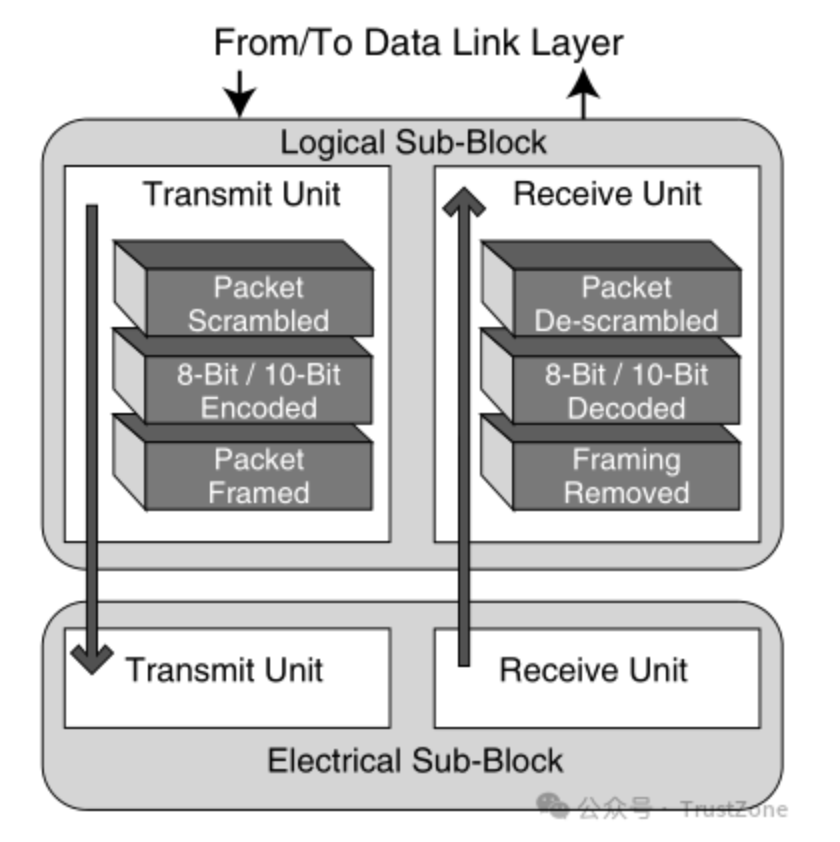

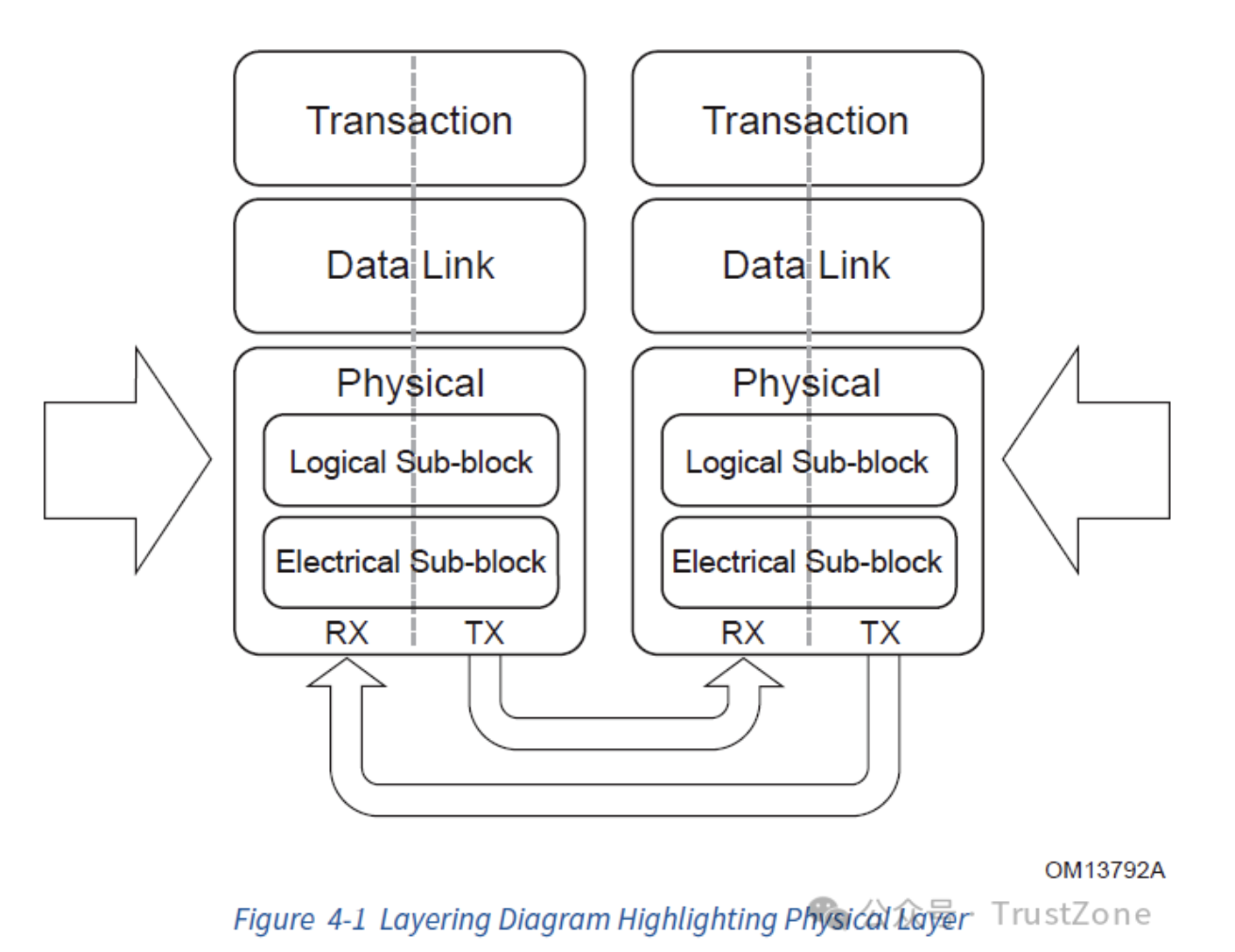

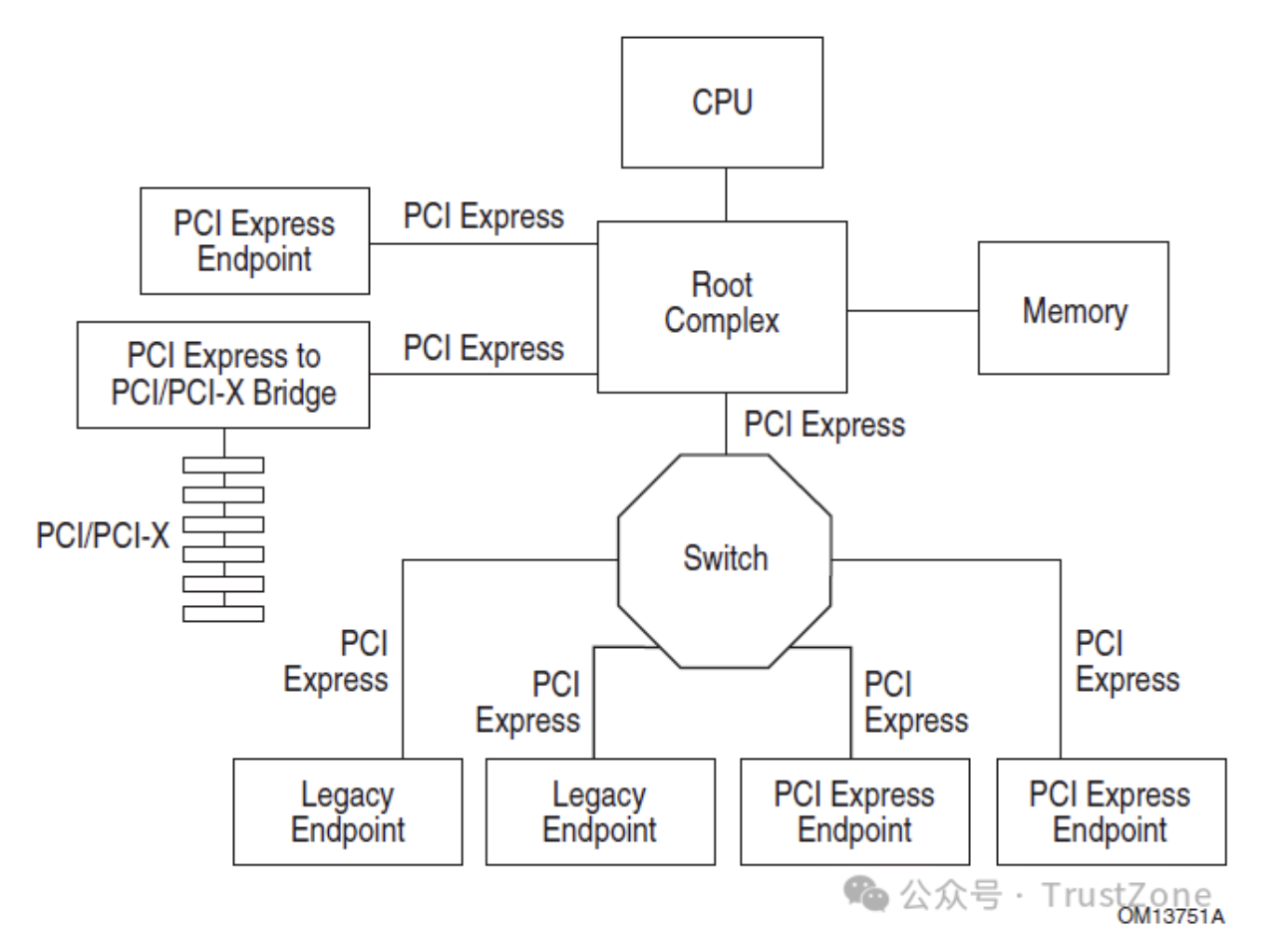

在看完事务层和数据链路层之后,我们来继续我们的协议栈之旅吧!这一篇中,我们会来看看PCIe物理层(Physical Layer)是如何工作的,从而帮助我们更加深入的了解PCIe的数据传输。

不少粉丝问我这个问题,今天我们就来给大家分析下。首先说下结论,IP DV的需求会越来越少,SOC DV则不会,如果有得选尽量选SOC DV。为什么有这个结论,我们下面分析下。

在上一篇中,我们介绍了PCIe设备的配置空间,及其设计的目的,最后我们说到了消息路由的设计。所以,这一篇我们就继续这个话题,来看看PCIe设备之间的通信方式吧。

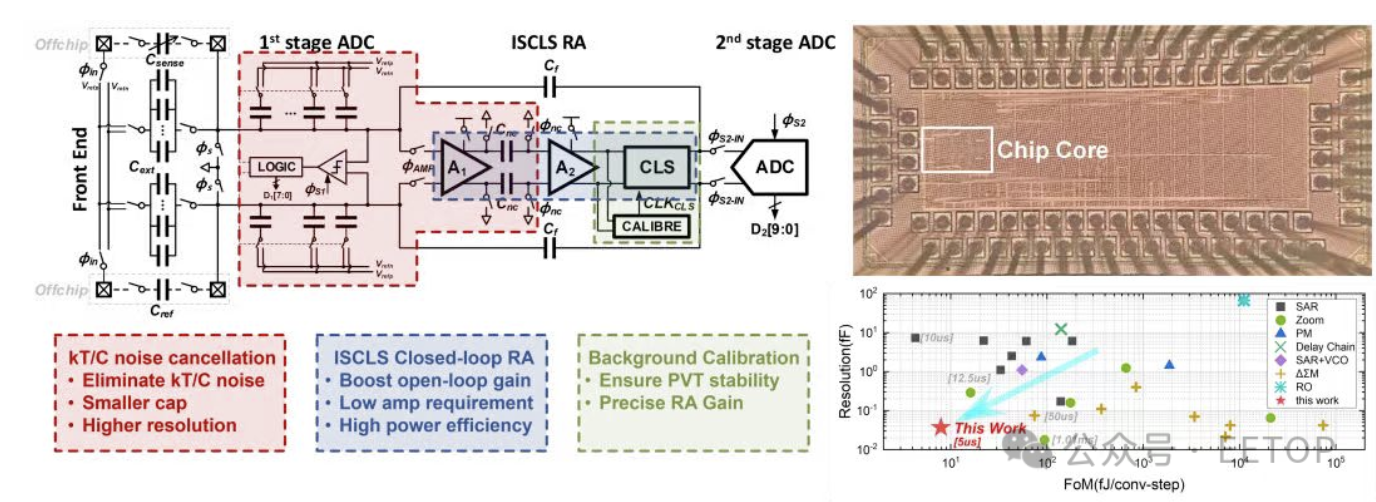

2月18日-22日,国际固态电路会议(ISSCC2024)召开。北京大学黄如院士-叶乐教授团队的论文(Jihang Gao, Linxiao Shen, Heyi Li, Siyuan, Ye, Jie Li, Xinhang Xu, Jiajia Cui, Yunhung Gao, Ru huang, and Le Ye, “A 7.9fJ/Conversion-Step and 37.12aFrms Pipelined-SAR Capacitance-to-Digital Converter with kT/C N...

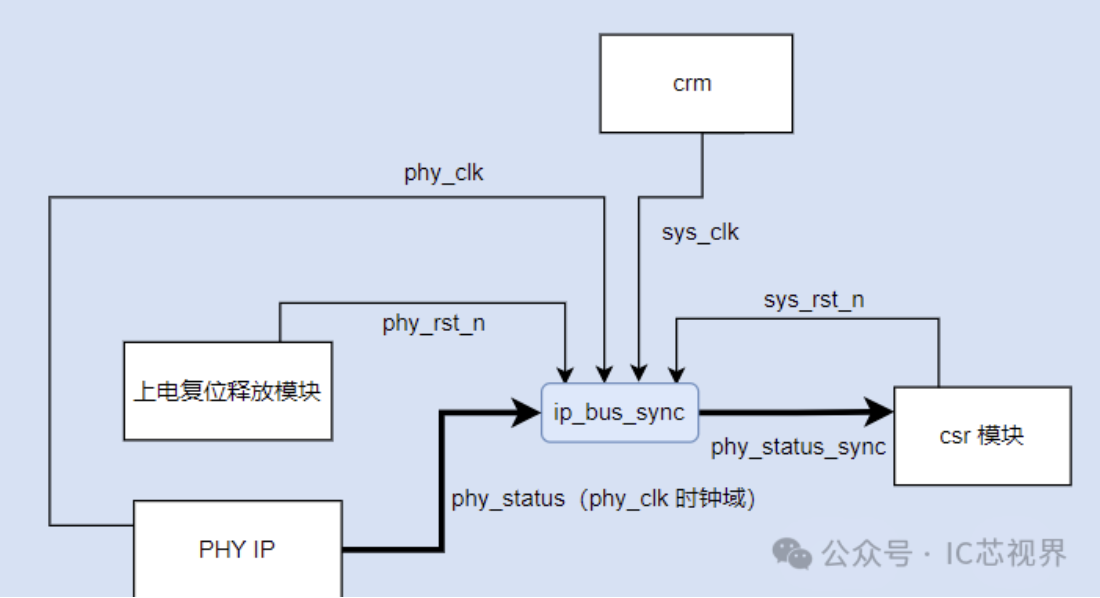

本文将介绍一个跨时钟错误的案例如图所示,phy_status作为一个多bit的phy_clk时钟域的信号,需要输入csr模块作为一个可读状态寄存器,目的是方便debug,而csr模块是sys_clk时钟域,此时phy_status需要进行跨时钟,得到sys_clk时钟域的phy_status_sync送到csr模块。

导言本次更新完虚拟机后,下次更新估计得等到下一次了,应该不会是最近。「更新特点:」1、解决新版本软件启动慢的问题2、一改以往只安装Synopsys软件的问题,本次添加了Mentor,Cadence等公司软件。3、本次首次使用redhat(7.9),yum的源已经换为centos,如果你使用yum update,桌面什么的会全部变为centos。4、桌面给...

PCIe的全称是Peripheral Component Interconnect Express,是一种用于连接外设的总线。

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

在2023年的12月,我注意到一个有趣的现象:猎头推荐的公司的质量明显提高了。这引起了我的好奇,于是我在社交媒体上发起了讨论,询问大家是否知道背后的原因。

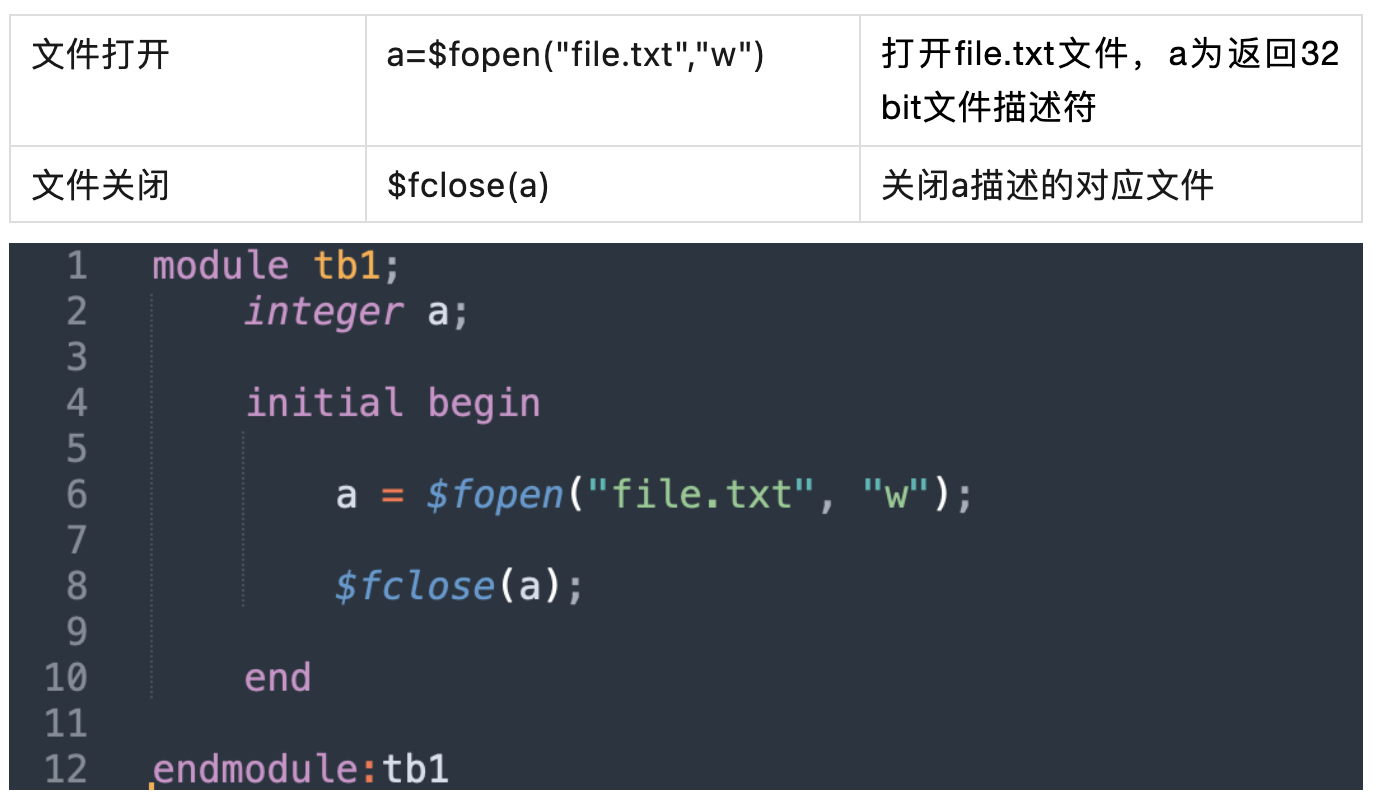

Verilog提供了很多对文件操作的系统任务和函数,例如打开关闭文件、向文件写入值、从文件读出值等等。