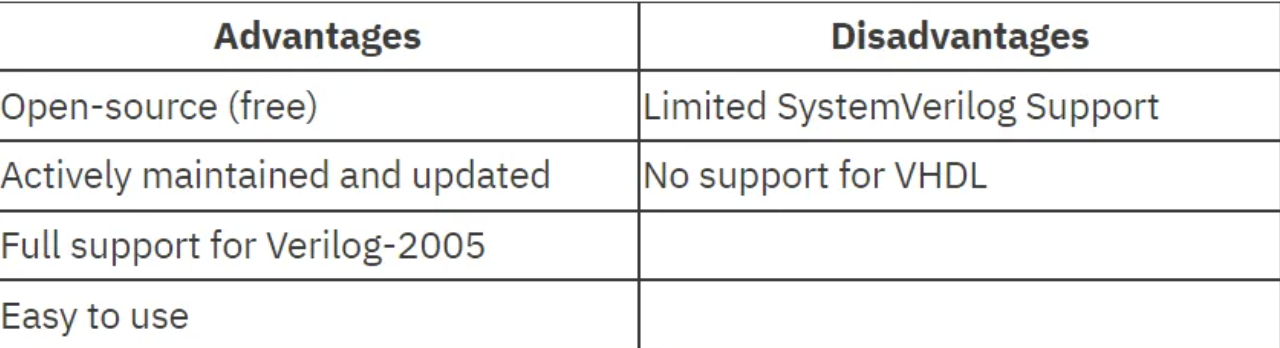

对于那些刚开始使用 HDL(如 VHDL 和 Verilog)进行编程的人来说,运行仿真以更好地了解该语言的工作原理非常重要。我们来看看四个仿真器——Icarus Verilog、GHDL、Vivado 和 Modelsim——并讨论它们的优缺点。

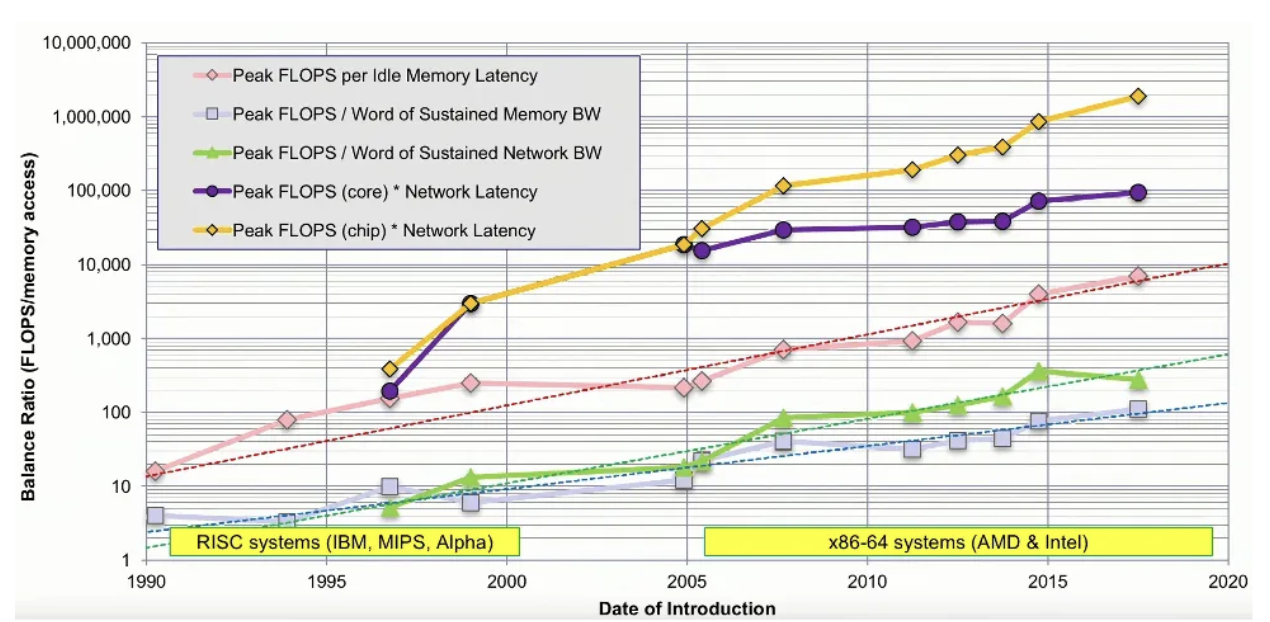

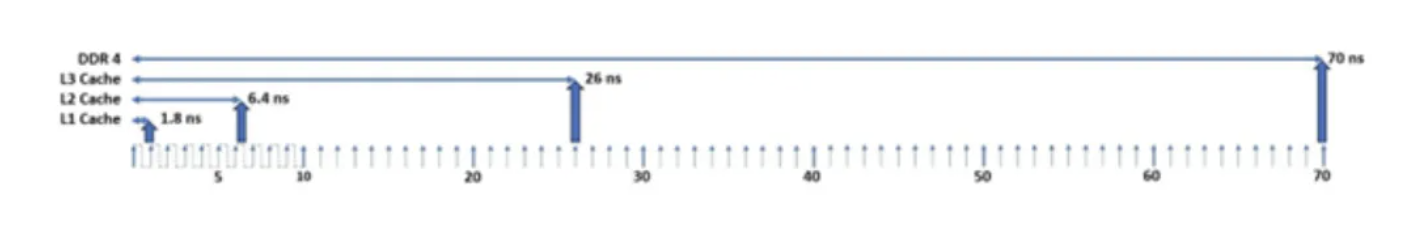

SoC 需要处理的数据量激增,虽然处理核心本身可以处理这些数据,但内存和通信带宽成为瓶颈。现在的问题是可以采取什么措施解决这个问题。

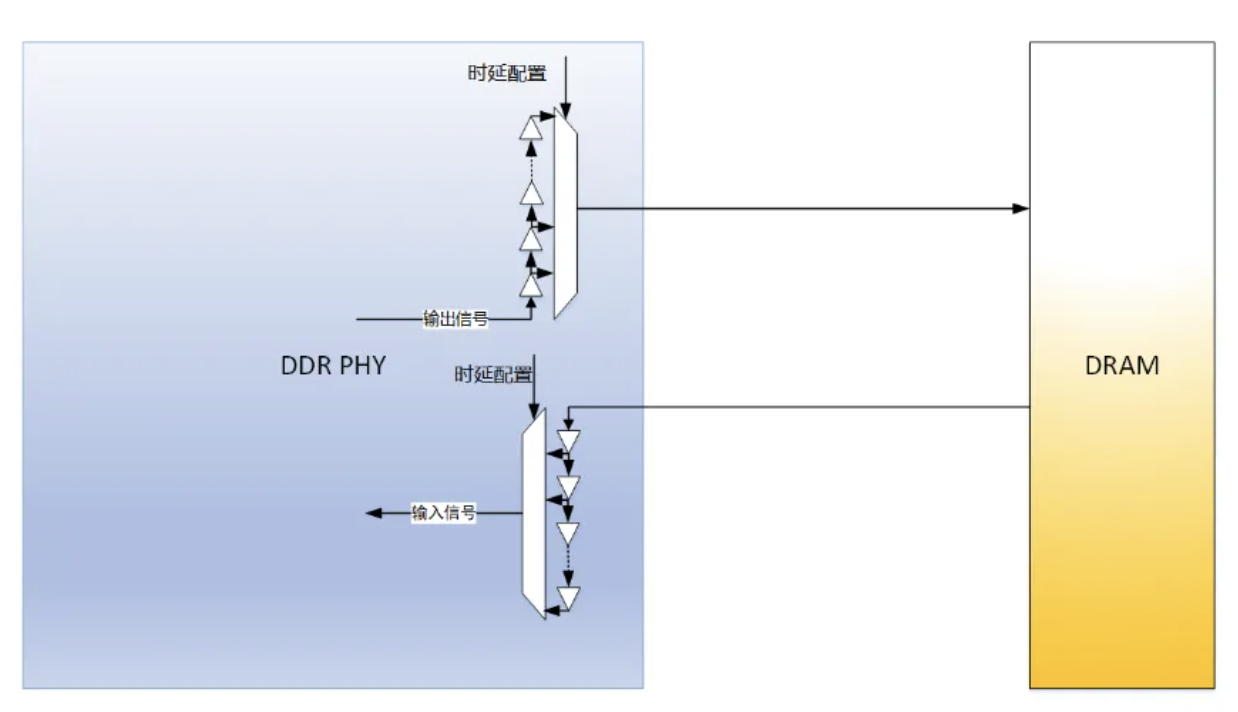

DDR接口速率越来越高,每一代产品都在挑战工艺的极限,对DDR PHY的训练要求也越来越严格。本文从新锐IP企业芯耀辉的角度,谈谈DDR PHY训练所面临的挑战,介绍芯耀辉DDR PHY训练的主要过程和优势,解释了芯耀辉如何解决DDR PHY训练中的问题。

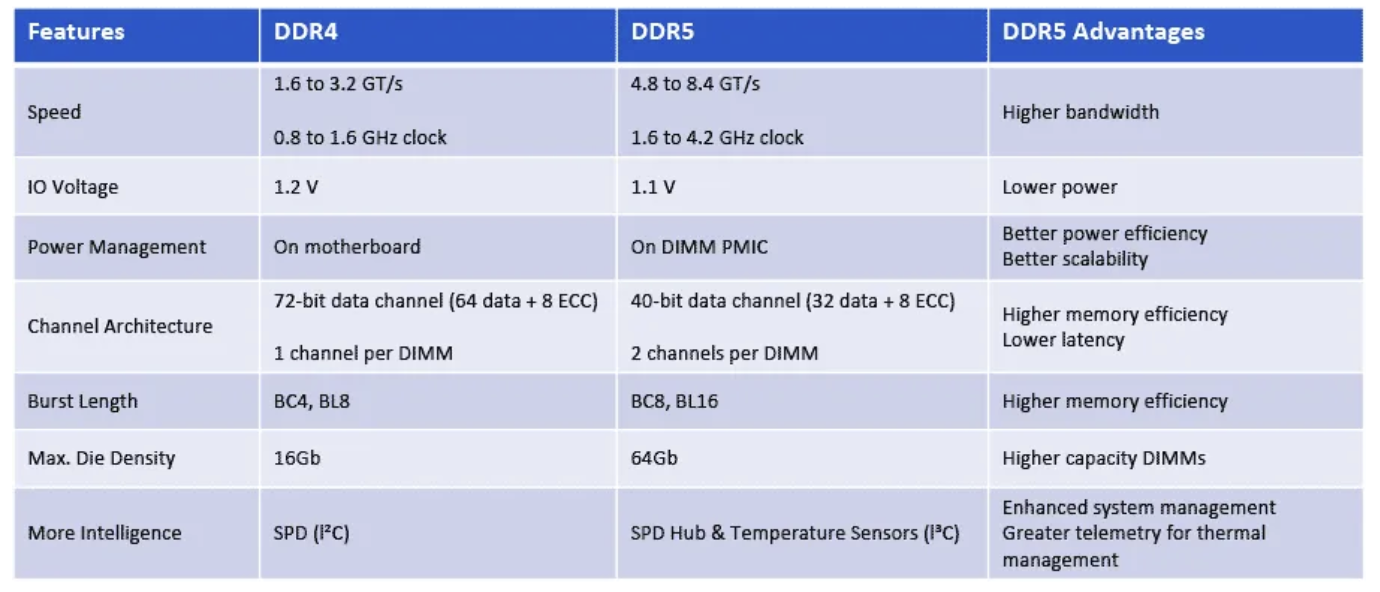

2021 年,JEDEC 宣布发布 JESD79-5 DDR5 SDRAM 标准,标志着行业向 DDR5 dual-inline memory modules(DIMM) 的过渡。DDR5 内存带来了许多关键的性能提升,以及新的设计挑战。计算系统架构师、设计人员和购买人员都想知道 DDR5 与 DDR4 有什么新功能,以及他们如何充分利用新一代内存。

如今,人工智能 (AI) 无处不在,从互联网核心的数据中心到互联网边缘的传感器和手持设备(如智能手机)以及介于两者之间的每个点,例如自主机器人和车辆。

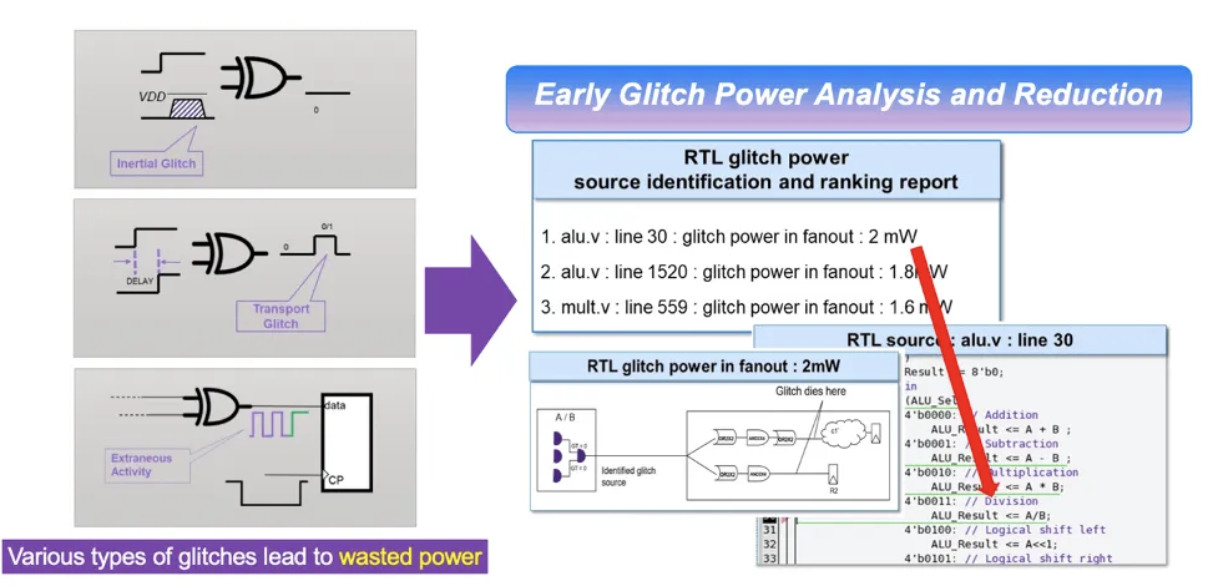

glitch功耗并不是一个新现象。在先进节点上,glitch功耗问题正变得越来越突出,没有一种解决方案适用于所有芯片或设计类型。

在基于RTL的芯片研发流程中,我们对于RTL开发时的功耗优化投入了大量精力,但这只是可以节省的功耗的一小部分。该行业转向更大算力系统的愿望受到热量的限制,因此越来越关注减少每个操作所消耗的能源。

就在几个月前,生成式人工智能还只是对未来可能性的承诺。今天,几乎每个有一丝好奇心的人都尝试过 ChatGPT。大多数人都对它的功能印象深刻,但同时也看到了它的局限性。

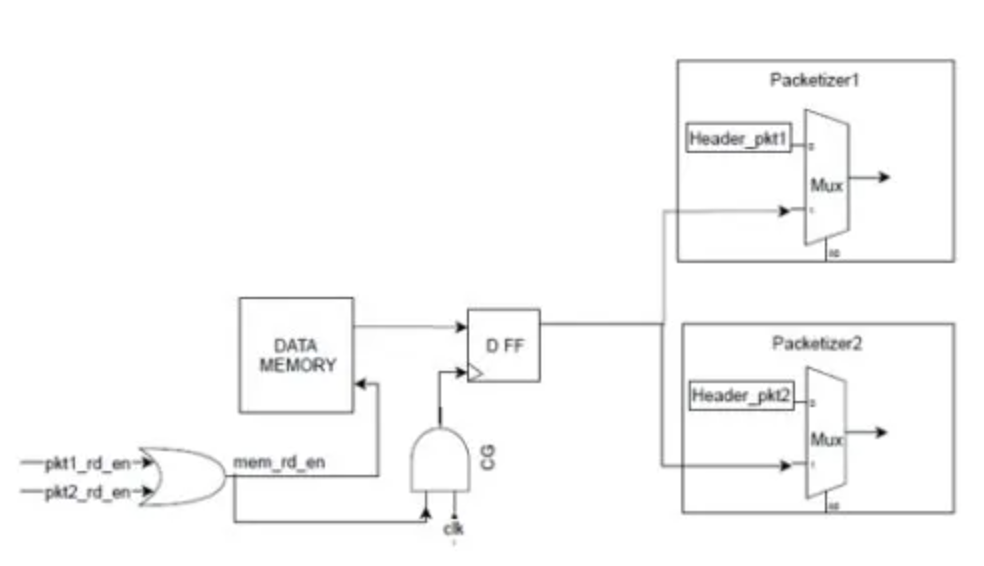

随着各种消费类设备智能化的巨大增长,这些应用正变得更加以数据为中心data-centric和计算密集型computation intensive。从IC设计的角度来看,这增强了早已经存在的power vs area trade-off的挑战。

在这里,引入特性(feature)验证的概念,即根据被测芯片的特性分配验证资源和人力。这样做虽然简化了验证资源分配和验证经理跟踪验证进度的难度,但也带来很大的完备性风险。

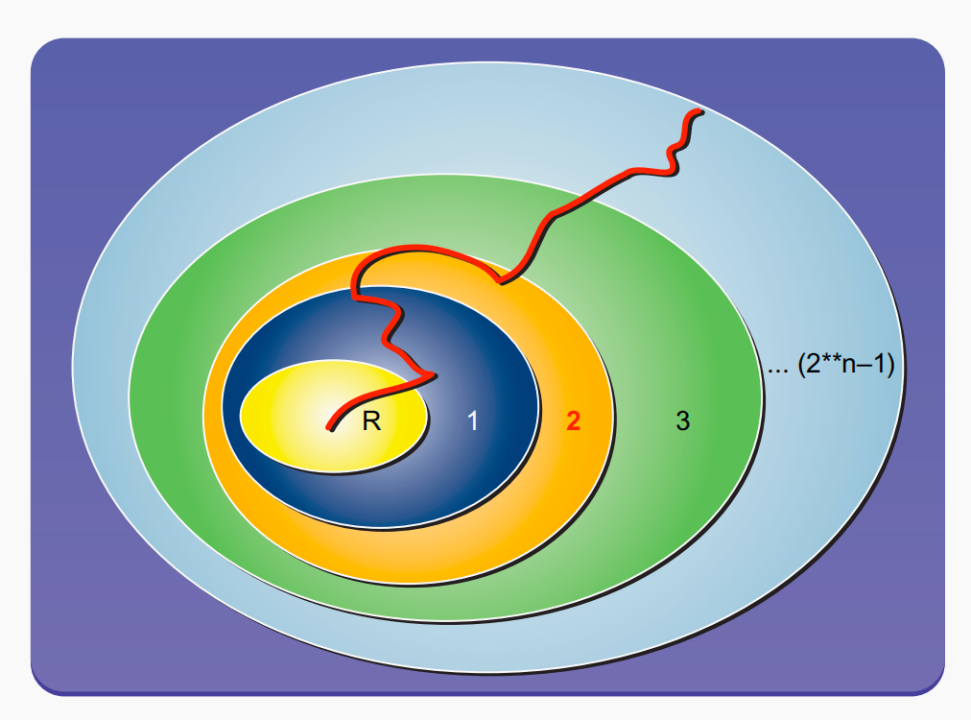

在理想的世界里,我们希望验证芯片的每一种可能的排列组合。 但在大多数情况下,这根本不可能。即使是一个看似简单的模块,也可能有成百上千种可能的输入和输出组合,为所有这些可能性创建验证用例是不切实际的。

多态(Polymorphism),从字面意思上看指的是多种形式,在OOP(面向对象编程)中指的是同一个父类的函数可以体现为不同的行为。

shallow copy只能复制类中的对象句柄,如果我们还想为这个对象句柄实例化,并复制其中的内容呢?

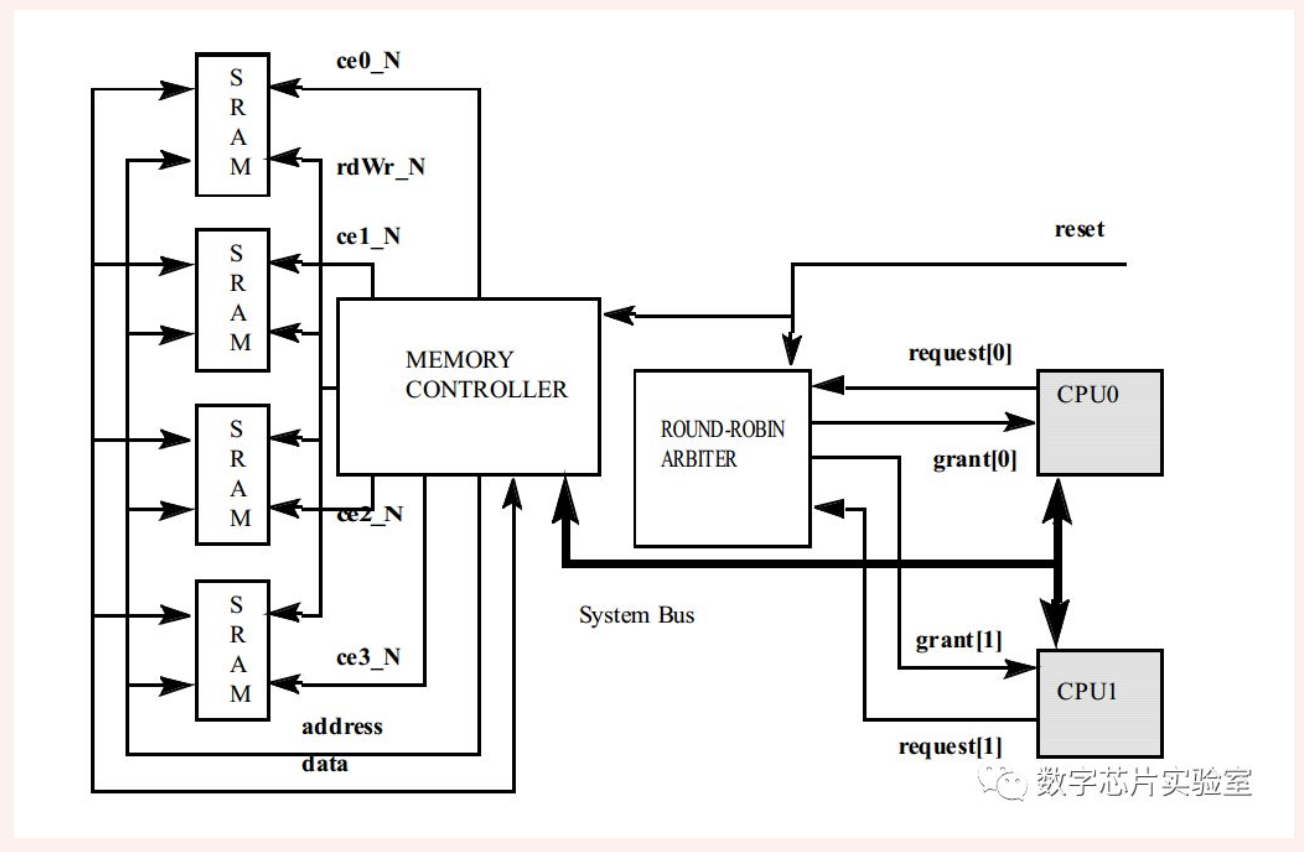

本节介绍一个包含存储器,仲裁器,控制器,系统总线和CPU的设计,所有这些设计文件都在工具安装目录底下:

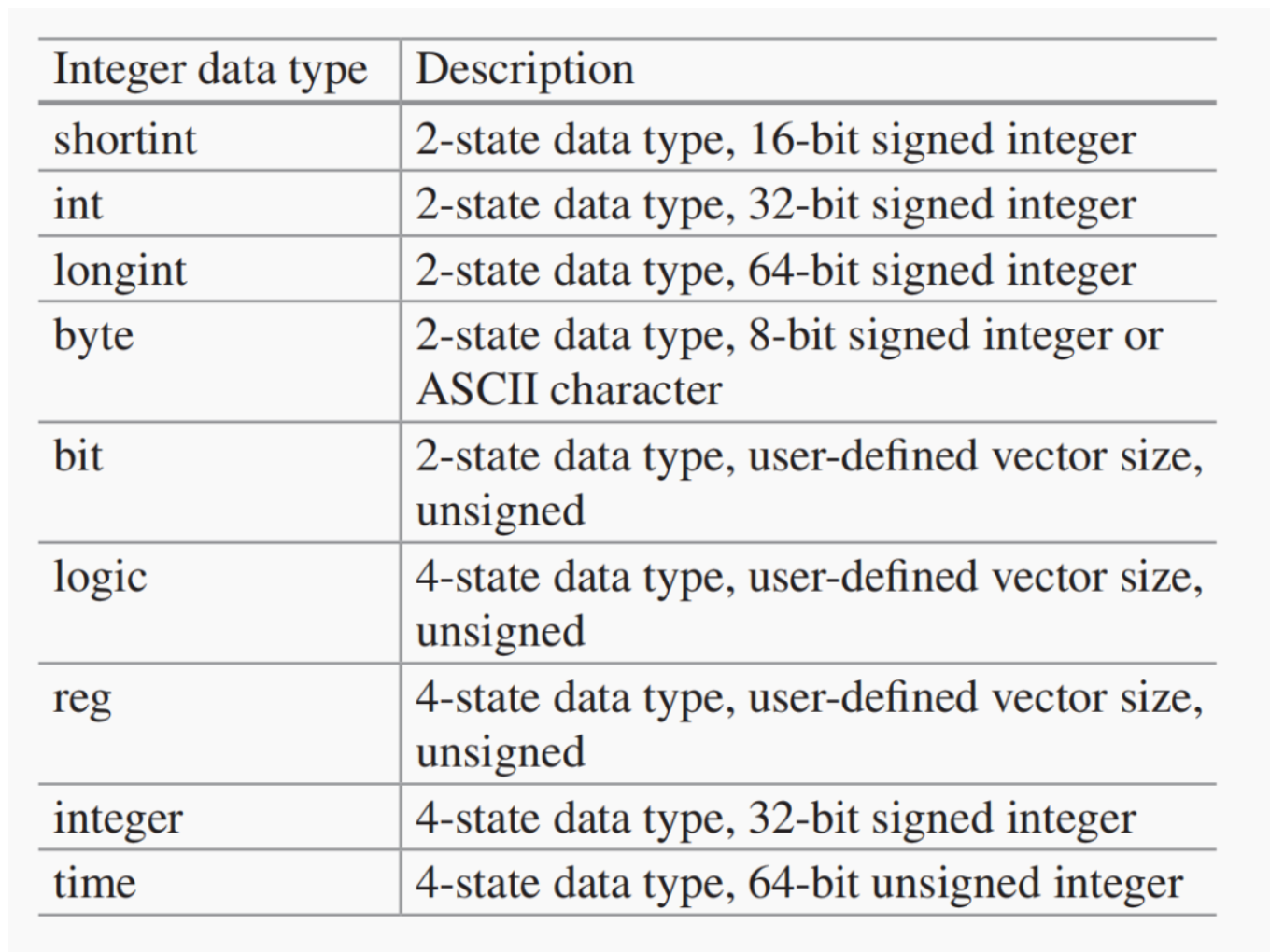

正如我们所知,“bit”是无符号的,而“byte”是有符号的。那么,你认为下面两个声明是等价的吗? {代码...} 答案是不等价,因为: {代码...} 所以,你需要小心混合bit和字byte数据类型的计算。同样,你认为以下两种说法等价吗? {代码...} 答案是等价。我们可以简单理解为bit signed [7:0] 等价为 byte。作者:验证哥布林来源...

Verilog提供了reg和wire数据类型,但是对于功能验证来说远远不够,所以SystemVerilog提供了很多更加丰富的数据类型,下面将一一介绍。

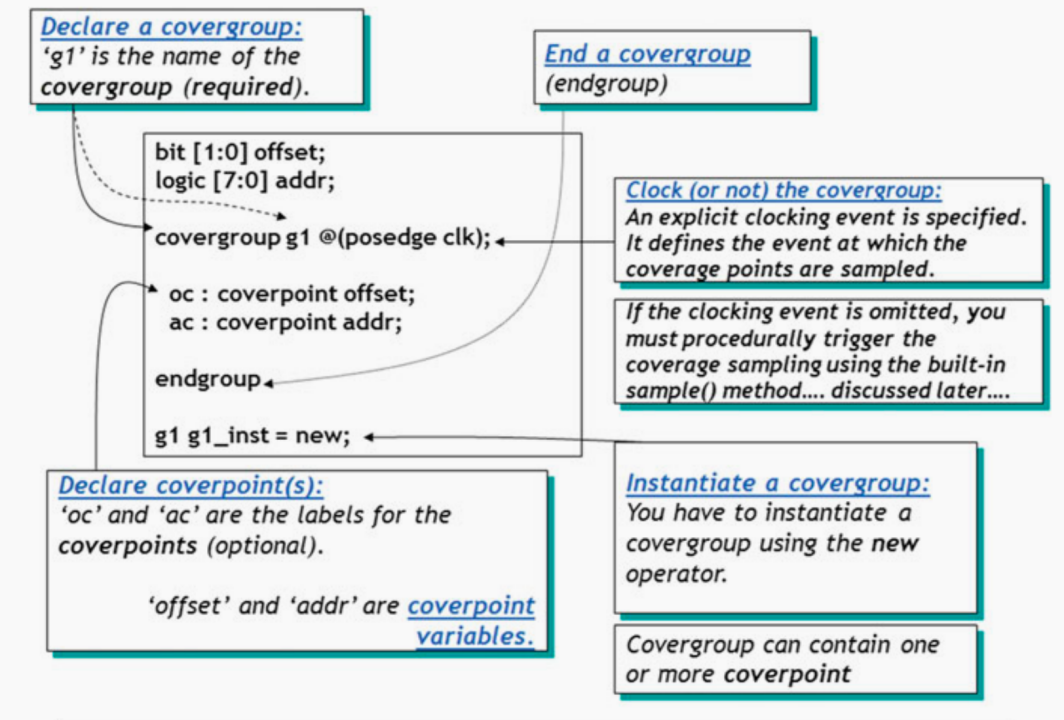

covergroup’可以在“package’”、“module’”、“program’”、“interface’ ”和“class’”中定义。

举个例子,对于具有10个寄存器、10个输入的设计而言,那么状态空间就是2^20。一般实际的设计中的状态空间要比这个多得多。

现代芯片研发流程是一个非常复杂的过程,所以不可避免会分成市场调研->方案架构制定->RTL开发验证->后端物理实现等等。分解其中验证又分为设计冒烟验证->模块验证->集成验证->FPGA测试等。稍微复杂点的IP也没办法由一个人完成验证,一些特性验证或者模块的验证必须要被分解成子特性/子模块。分解之后...

1、Structural hazards,当不同的stage竞争共享资源时,这也是我们为什么需要区分I-cache和D-cache的原因。