大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

小肥羊目前在UCLA师从Abidi研究时钟电路设计,在老头子夜以继日智商碾压下,终于对时钟电路有了一些理解,写下一些认识,与广大硅工探讨,此为第一篇。标题取自William Blake的诗作《Auguries of Innocence》,盖因芯片由沙(硅)制成而自成一世界,片上时钟则可高达GHz范围,人间一瞬在芯片中几已成永恒。以下为正文。

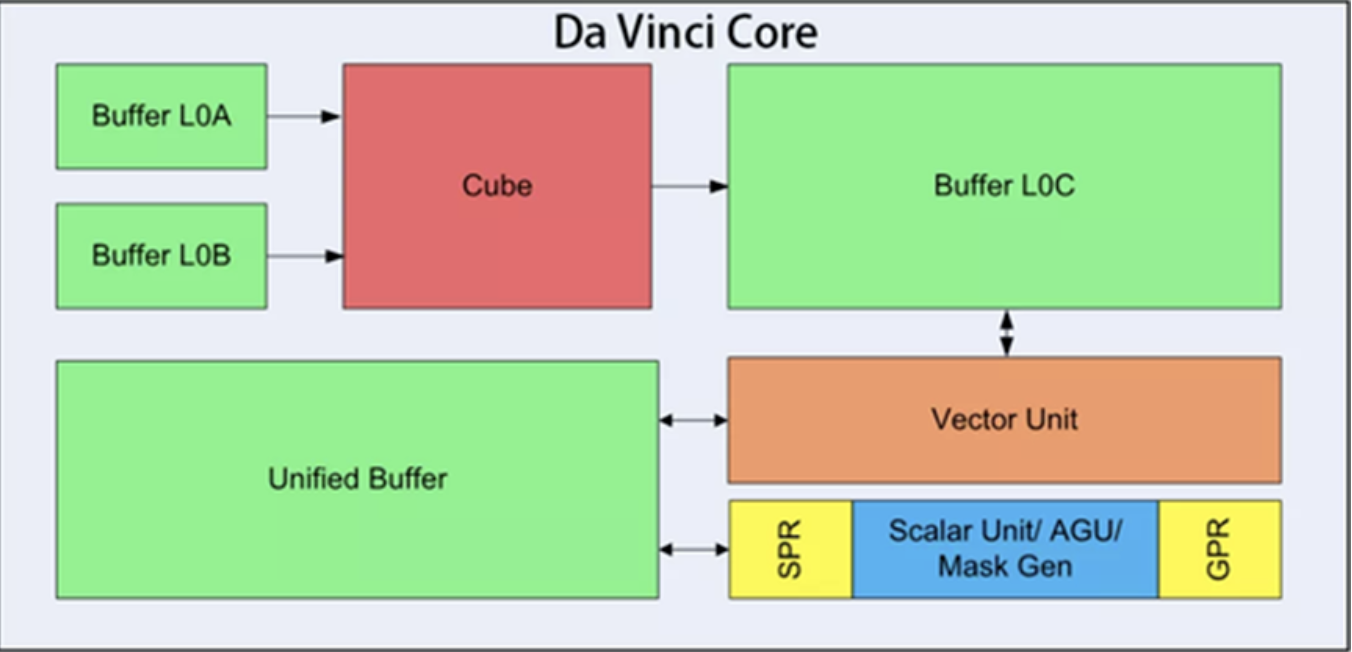

这两年,图形处理和AI(人工智能)加速计算需求的不断涌现,国内AI芯片市场已呈现出百花齐放的发展态势,衍生出多种类型的AI加速产品。近期的全国政协会议也谈到了这个---“人工智能已经成为国家间科技竞争的必争之地。要深入挖掘国产AI芯片算力潜力,加速推动国产操作系统发展,夯实人工智能发展算力底座,助推新质生产...

在最近的 IEEE 国际固态电路会议 ( ISSCC ) 上,三星科学家发表了一篇论文,继续推动 DDR5 性能的进步。

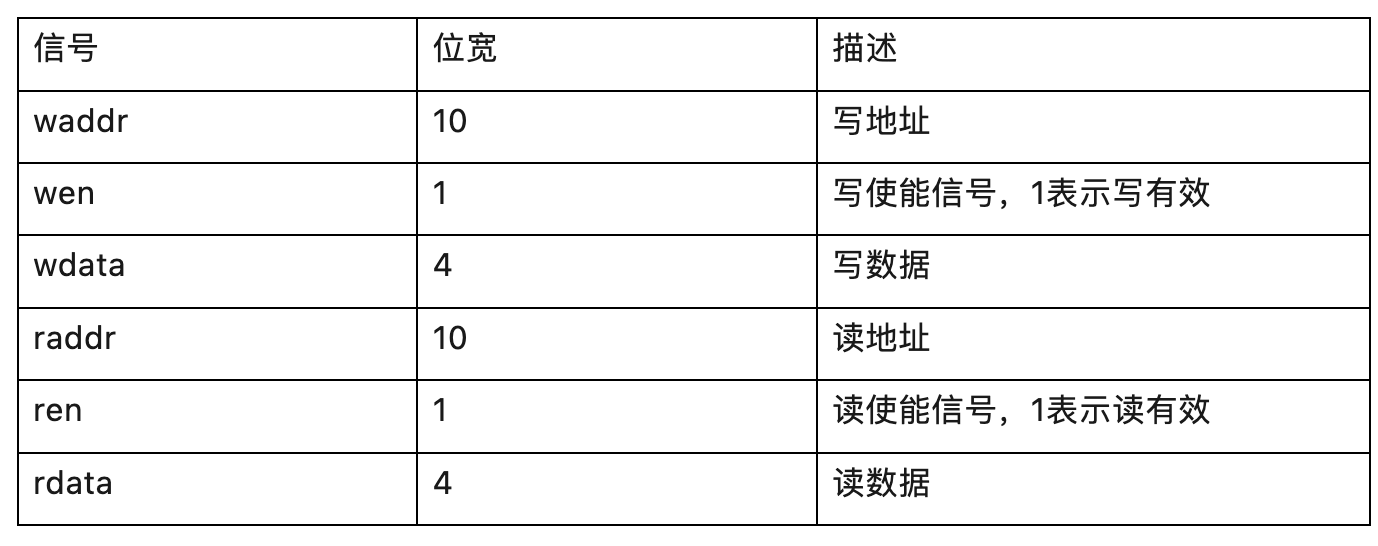

在IC设计中,我们有时会使用深度很大,位宽很小的ram。例如深度为1024,位宽为4bit的ram。此类的ram有个明显的缺点:形状狭长,不利于布局布线、导致读写接口走线过长,不利于时序收敛。

本文是由论坛网友在EETOP博客分享的模拟IC工作心得,感觉非常不错,现通过微信文章分享给大家。 博客地址:[链接]正文:在学校的时候,属于电源团队,自己纯属渣渣水平,就只做了个LDO的项目,所以17年毕业找工作,难免磕磕碰碰。后来,终于有一家做军工的企业愿意收留我,我这才有了安身立命的机会。终于进公司了,领导...

随着春节的脚步越来越近,许多身处四面八方的工程师们开始踏上归家的旅途,心中充满了对家人团聚的期待和对过去一年工作成就的回顾。在这个特别的时刻,当父母问起工作时,你脑海中闪现过哪些高光时刻?

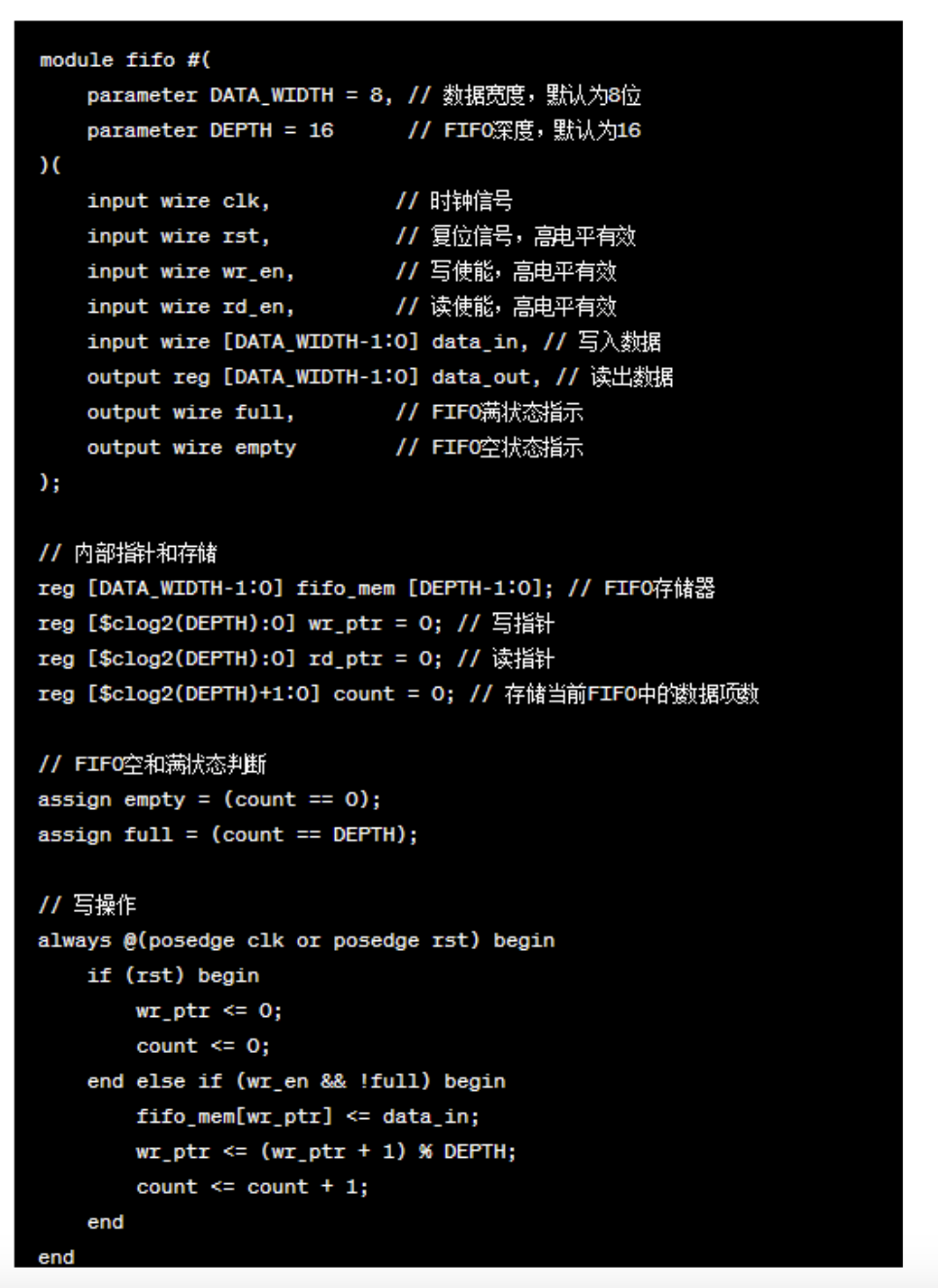

Chisel (Constructing Hardware in a Scala Embedded Language) 是一种用于硬件设计的高级语言,相比于传统的硬件描述语言如Verilog和VHDL,Chisel 有多个显著的优势,主要体现在设计的抽象级别、重用性、测试能力和开发效率上。下面我们通过具体案例来说明这些优势。

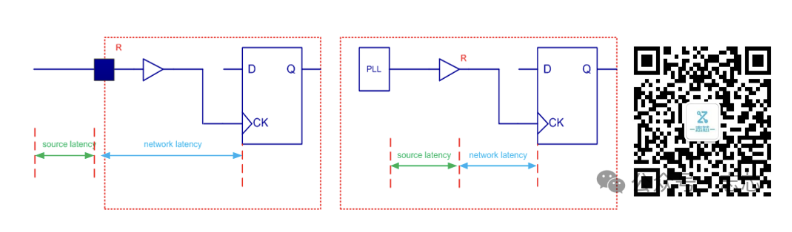

本文基于innovus工具讨论。基于block level的设计进行时序分析,如果在SDC和flow脚本中对clock 没有设置source clock latency 和network clock latency,在ccopt之前clock模式是ideal的,所有的clock latency都是按照0计算。

gvim正则表达式常在命令行模式下使用,一般用于文本文件字符串的替换、删除等操作。 典型的替换命令格式:%s/正则表达式/要替换的字符串/g”典型删除命令格式: %g/正则表达式/d我们先讲元字符,接着讲述一些基本的应用例子,最后讲一些更高阶的应用例子,一文搞懂正则表达式!一. 元字符先搞清几个基本的概念,普通元字...

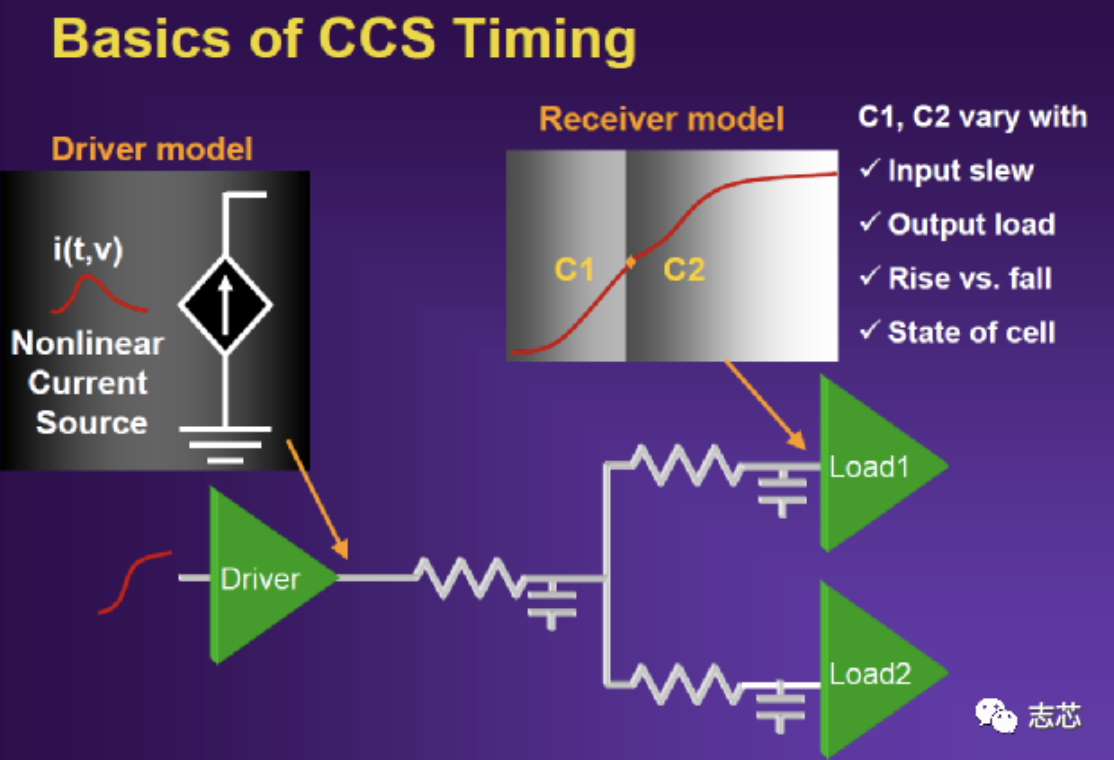

CCS,con_current source即复合电流源模型,比NLDM(none lineal delay model即非线性模型)更进一步,这个模型属于电流源模型,输出I不变,load上cap变化会对I影响,V也变化。

重视spec,拒绝口口相传的feature。完善的spec意味着2方面,一是设计把芯片架构和设计细节想清晰了,代码质量自然会高,bug数目自然会少,后期的收敛速度自然会快。二是给验证提供了正确的输入,验证有了完整的spec,才有可能做出完善的vplan和验证环境;如果设计都没想清楚怎么做,写到哪,想到哪,必然存在很多漏洞,后...

时间已经来到了2024年,芯片行业的热度已然大幅下降,但这个行业的价值依然在。芯片应用的种类繁多,也意味着芯片的类型多种多样,我也经常会被问到做芯片设计,到底哪个方向更有前景?不同类型的芯片设计岗位之间是否可以跳槽换方向,借着这个话题和关注公众号的朋友分享一下我的经验。

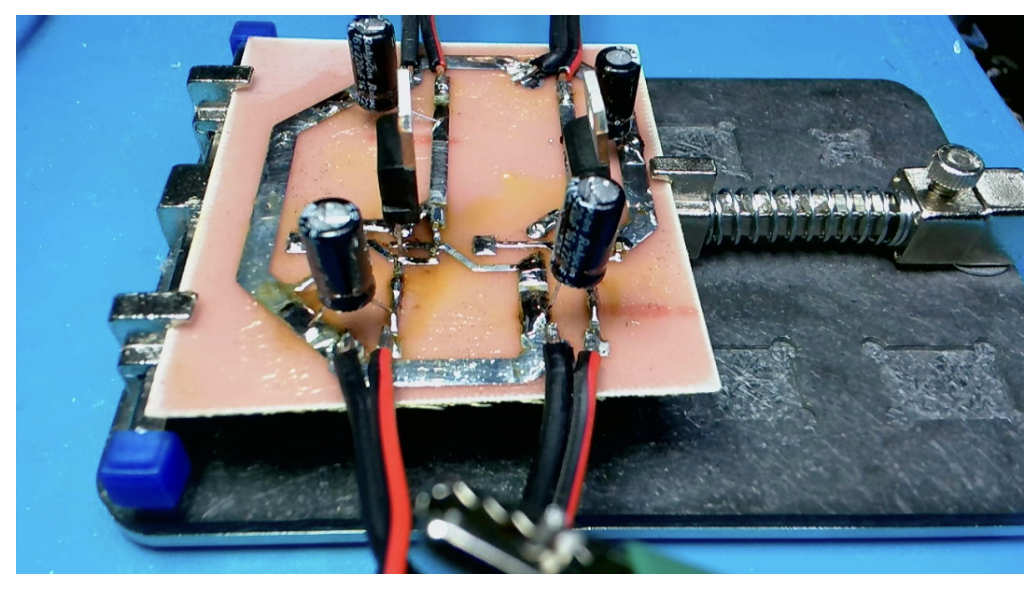

如果一个稳压芯片输出电流不能够满足要求,是否可以简单的将两个稳压芯片进行并联提供更大的输出电流呢? 下面简单测试一下,看会出现什么问题。

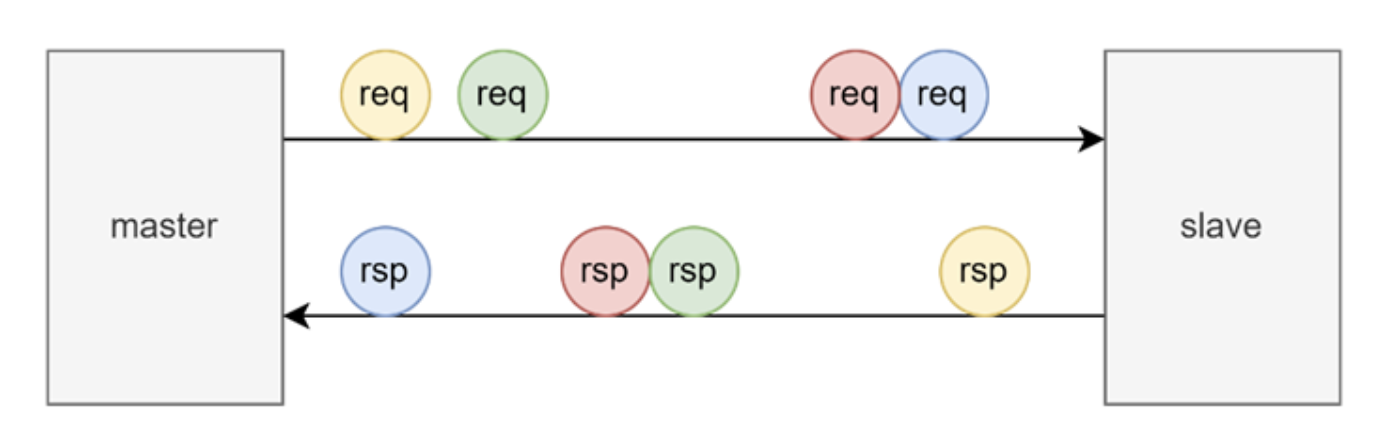

监控总线超时是一个总线交互模块的常见操作。总线超时行为,是对于master端一笔发出去的请求,slave端返回的数据无法在规定的时间内到达。那么我们进行超时检测的本质原因是什么呢?是在总线挂死或者其他模块及存储系统出现致命问题时,能够及时的上报异常,进行后续的处理。或者说,在绝大部分的需求场景下,timeout的...

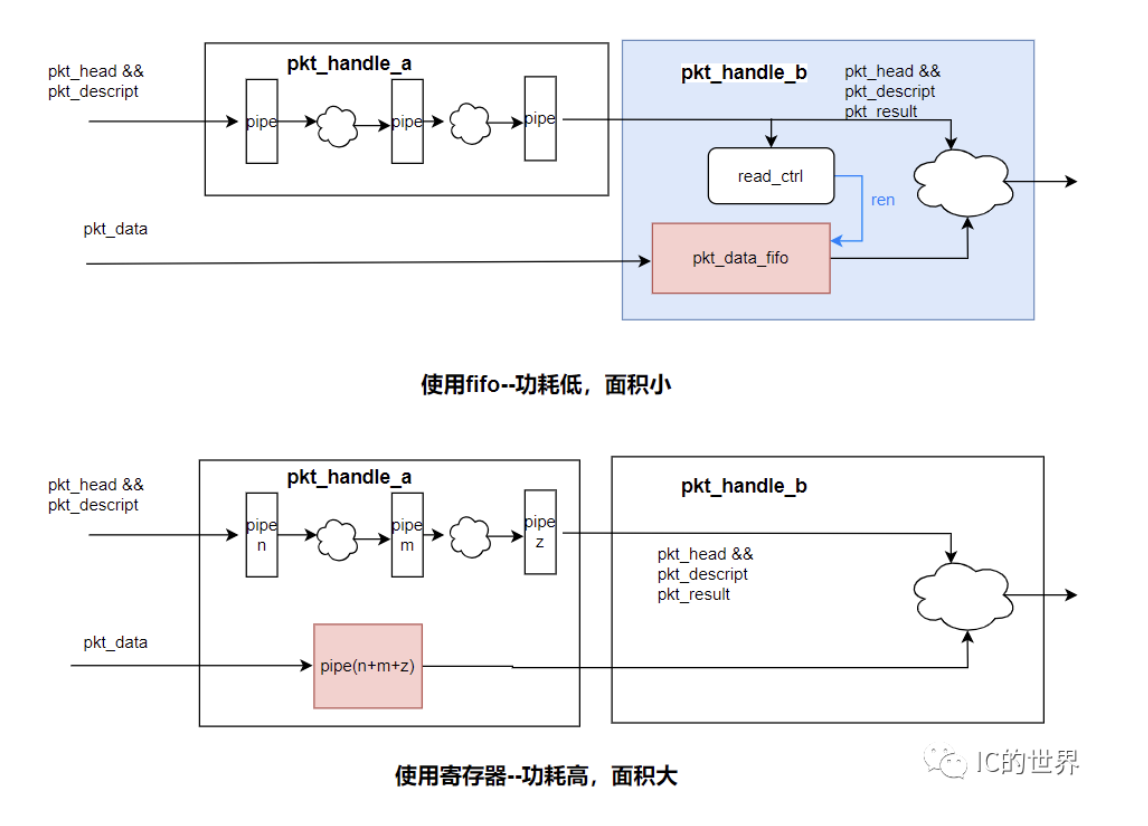

本案例中,我们讲解一种使用fifo节约资源,降低功耗的设计。如图所示,pkt_handle_a模块是对数据包进行处理的模块,但是不需要包数据(pkt_data),而仅仅需要根据包头(pkt_header)和包描述符(pkt_descript)。这时候该怎么设计呢?可以采用如下方式:在pkt_handle_b模块使用一个fifo用于存储包数据(pkt_data),pkt_h...

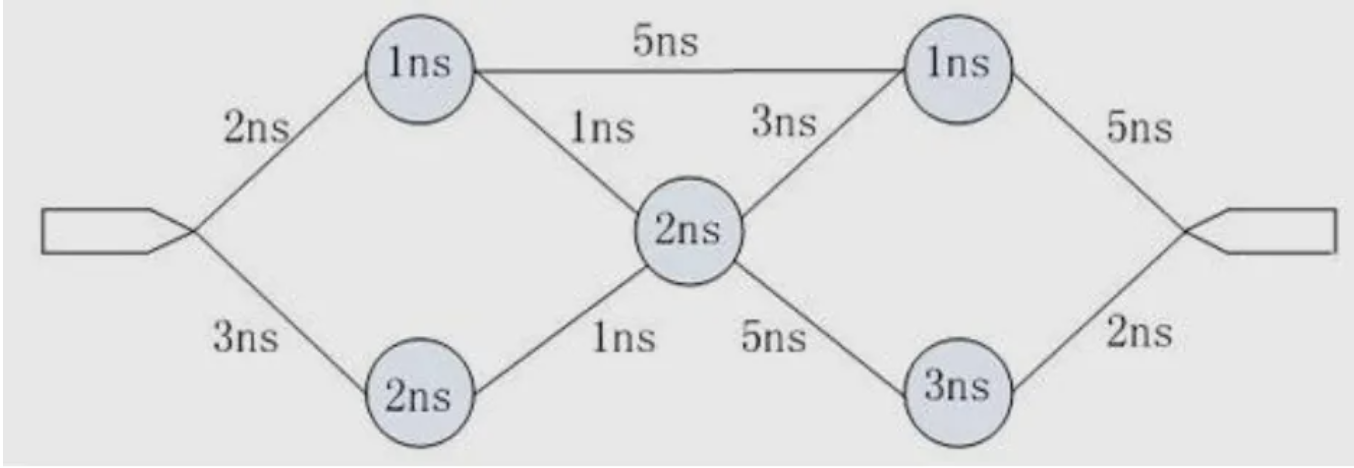

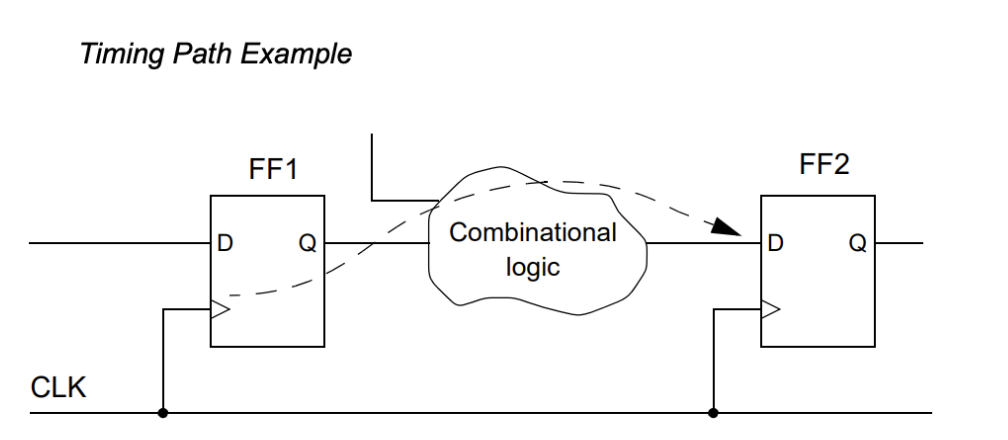

在同步电路设计中,时序是一个非常重要的因素,它决定了电路能否以预期的时钟速率运行。为了验证电路的时序性能,我们需要进行静态时序分析,即在最坏情况下检查所有可能的时序违规路径,而不需要测试向量和动态仿真。本文将介绍静态时序分析的基本概念和方法,包括时序约束,时序路径,时序裕量,setup检查和hold检查等。

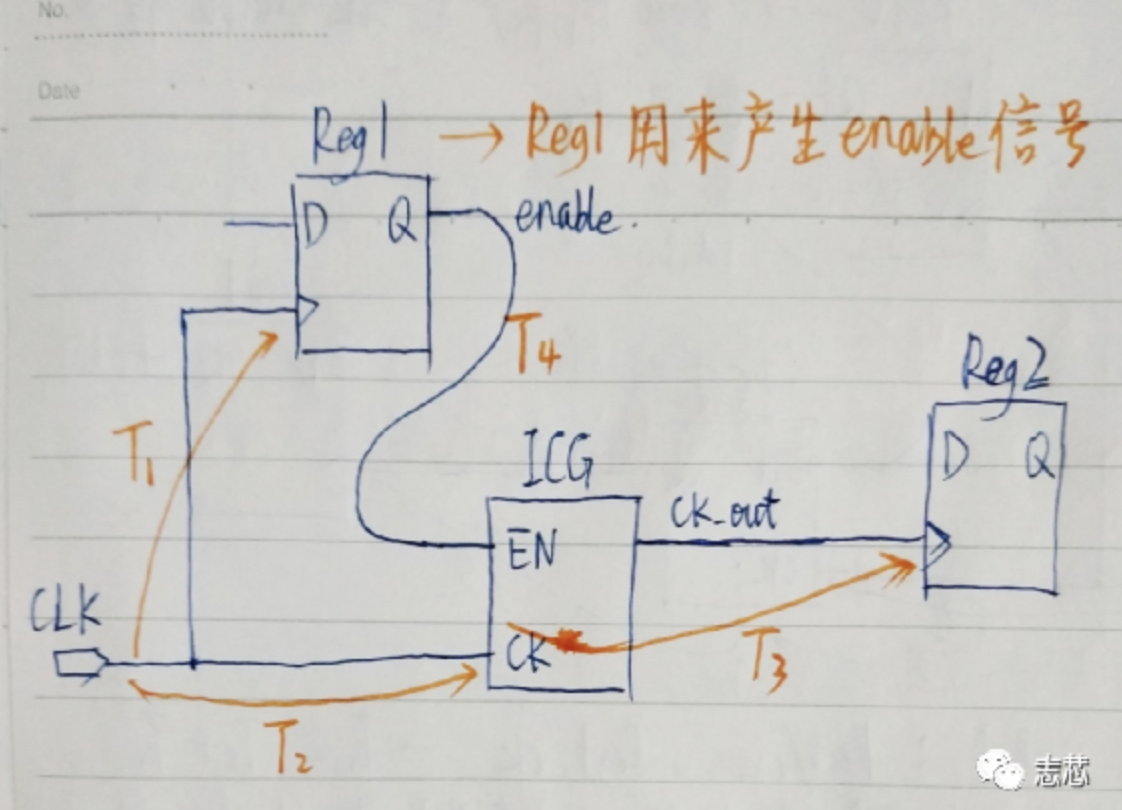

在不人工干预的情况下,tool默认会尝试把reg1的CK pin和Reg2的CK pin做平。但是静态时序分析时,reg1→ICG也会做时序check;所以,ICG会天然存在一个很大的clock skew,导致建立时间违例。

比利时微电子研究中心(imec)宣布推出免费使用版虚拟晶圆厂 imec.netzero 模拟平台,该工具提供了一种量化芯片制造业环境影响的视角,提供学界、政策制定者及设计人员具有价值的洞见。透过此次发布的免费版网页应用,imec旨在跨出半导体供应链,协助产业降低其所带来的环境影响。