技术编辑:王治治丨发自 思否第四大道

SegmentFault 思否报道丨公众号:SegmentFault

近日,Google AI 负责人杰夫•迪恩(Jeff Dean)和谷歌研究部门、谷歌芯片实现和基础设施团队共同撰写了一篇论文,论文中描述了一种基于学习的芯片设计方法,并声称可以平均在 6 个小时内完成芯片的设计。

据悉,这项研究基于谷歌于 3 月份发表的一篇论文的基础上进行,并对当时提出的技术方向做了推进。

该论文的发布,意味着片上晶体管的放置可以在很大程度上实现自动化。如果技术成果可以公开发表,那么这项技术可以让资金紧张的初创公司开发出自己的芯片,用来进行人工智能或其他行业的研究应用。此外,该技术还可以帮助缩短芯片的设计周期,使硬件能够更好地适应理论研究的快速发展。

杰夫•迪恩在去年年底的一次采访中曾透露过这一项技术,并介绍到"从你想要的设计,到实际将其铺设在芯片上,并在面积、功率和线长等方面有适当的限制,满足所有的设计或制造过程,这是一个持续很长时间的过程,而我们基本上设计出了一款机器学习模型,它可以学习如何为一个特定的芯片进行元件布局。"

该 AI 模型的方法旨在将逻辑门、存储器和更多的网格图放置到芯片画布上,从而使设计在遵守放置密度和路由拥塞限制的同时,优化功耗、性能和面积(PPA)。图谱的大小从几百万到几十亿个节点组成的集群不等,通常情况下,评估目标指标需要数小时到一天以上的时间。

该框架通过指导一个通过强化学习训练的模型来优化芯片的布局,进而给出网表、当前要放置的节点的 ID,以及网表和半导体技术的元数据,一个策略 AI 模型会输出一个概率分布在可用放置位置上的概率分布,而一个价值模型则估计当前放置的预期效果。

在实践中,从空芯片开始,到上面提到的模型按顺序放置组件,直到完成网表,直到最后才会得到波长(与功率和性能相关)和拥挤度的负加权总和(受密度限制)。为了指导模型选择先放置哪些组件,组件按大小排序;先放置较大的组件可以减少以后没有可行的放置的可能性。

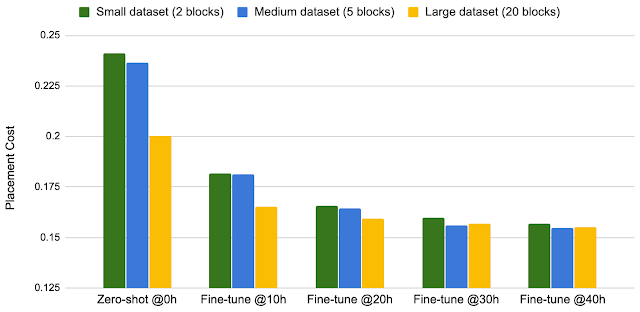

训练该模型需要创建一个由 10,000 个芯片放置的数据集,其中输入是与给定放置相关的状态,标签是放置的补偿效果(即线长和拥挤)。研究人员通过首先挑选 5 个不同的芯片网表进行构建,并对其应用 AI 算法,为每个网表创建 2000 个不同的放置状态。

在实验中,研究者报告表示随着他们在更多的芯片上训练该框架,他们能够加快训练过程,更快地产生高质量的结果。事实上,他们声称,与领先的基线相比,该框架在 TPU 上实现了极佳的 PPA。

"与现有的方法不同的是,我们的工作利用了从放置之前的芯片中获得的知识来优化每个新芯片的放置,使其随着时间的推移变得更好,"研究人员总结道。"此外,我们的方法可以直接优化目标指标,如线长、密度和拥挤度等,而无需像其他方法那样定义函数。当新的成本函数出现时,我们的公式不仅可以很容易地将其纳入,而且还可以根据给定芯片块的需求(例如,时序关键型或功率受限型)对其相对重要性进行加权。"

资料来源:

Venturebeat:《Google claims its AI can design computer chips in under 6 hours》