写完了UART,接下来说一下另一个通信协议。SPI协议。SPI,中文串行外围设备接口,SPI总线是在物理上是通过接在外围设备微控制单元上的同步串行端口的模块来实现。他允许MCU以全双工的同步串行方式,与各种外围设备进行高速数据通信。和上一篇类似,主要针对的初学者,所以用更加简单的白话来讲述这个协议与实现。全双工意味着收发两个方向上同时工作,也就是可以边发边收,好比一个人可以一边说着话,一边听对方说话。

作者:Trustintruth

来源:https://zhuanlan.zhihu.com/p/94335206

和UART一样,SPI也是串行口。SPI实为高速同步串行口。收发同步,可同步进行。与UART不太相同的是SPI在芯片的管脚上只占用四根线,节约芯片的管脚。(与其他的高速协议比起来节约。)

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。一主一从就是一个人说话一个人听,而一主多从就好像是一个人和多个人说话,当他CUE到你的时候你就知道“奥,他在和我说话”。SPI的设备共有的四根线,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

- SDO – 主设备数据输出,从设备数据输入

- SDI – 主设备数据输入,从设备数据输出

- SCLK – 时钟信号,由主设备产生

- CS – 从设备使能信号,由主设备控制

其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个SPI设备成为可能。”

SPI是串行传输协议,数据是一位一位的传输的,而确定传输位的就是SCK信号,有他来产生脉冲信号,SDI和SDO则是基于这个脉冲完成数据传输,数据的输出通过SDO线,数据在时钟上升沿或下降沿改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,所以要完成8位数据的传输,至少8次的时钟信号改变。但SCK时钟线只受主设备控制,从设备不能控制信号线。与普通的串行通信不同的是,普通的串行通信通讯一次至少8位,而SPI允许一位一位的传输,甚至允许暂停。主设备通过SCK时钟的控制可以完成对通信的控制。SPI还有一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入输出。在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,所以简单高效。但是SPI接口没有指定的流控制,没有应答机制确认是否接收到数据。

在对应的接口上,

- MOSI:主出/从入

- MISO:注入/从出

- SCK:串行时钟

- SS:丛属选择

而SS的引脚数决定了可连到总线上的器件数量。你要想和足够过的人说话,你首先要知道做够多的名字。SPI传输串行数据是首先传输最高位,波特率可达到5Mbps

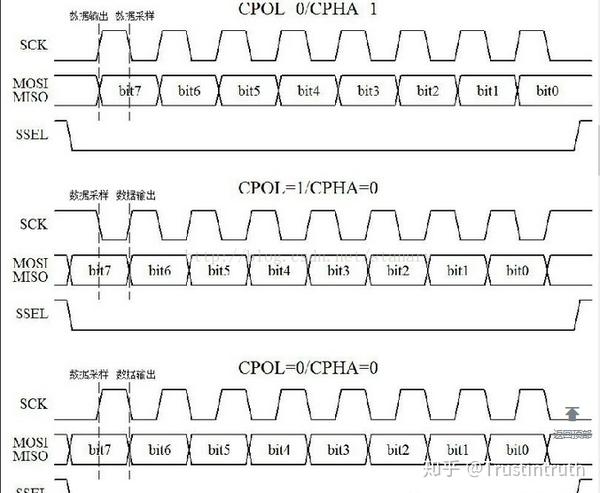

时序图如下:

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果 CPOL="0",串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设音时钟相位和极性应该一致

CPHA = 1,就表示数据的输出是在一个时钟周期的第一个沿上,至于这个沿是上升沿还是下降沿,这要看CPOL的值而定,CPOL=1那就是下降沿,反之就是上升沿,数据的采样就是在第二个沿上

CPHA = 0,就表示数据的采样是在一个时钟周期的第一个沿上,那么数据的输出就在第二个沿上了

实际就是时钟的高有效与低有效。

代码实现是一个之前做W5500时写的,功能单一而且只发,所以不贴源码了,感兴趣的可以自行下载。

https://download.csdn.net/download/stanary/10503725

推荐阅读

关注此系列,请关注专栏FPGA的逻辑