本作品介绍参与极术社区的有奖征集|分享研电赛作品扩大影响力,更有重磅电子产品免费领取!

参赛单位:华东师范大学

参赛队伍:SSPT

指导老师:王淑仙 刘一清

参赛队员:唐宇枫 洪展鹏 王泽宇

1.作品简介

近年来随着5G技术的不断发展,通信设备间的数据传输速率不断提升,逐步解决了超高清显示等信息感知领域面临的高数据传输速率的难题,使得这些领域发展迅猛。与此同时,为了提升信息感知系统的性能,作为此领域数据源的传感器,其产生的数据量也在逐渐增长,对后级的数据采集系统的数据采集速率提出了新的要求。而现有的数据采集设备存在数据采集速率低、售价高、兼容性不足的现象。

本团队针对现有的数据采集系统的不足,设计了一套基于ZYNQ UltraScale+的高速数据采集系统,为数字信号源提供了100路LVDS信号线,数据采集速率可达160Gbps;通过更换系统子板为模拟信号源提供了采集前的预处理(包括模拟域的放大、滤波及模拟信号-数字信号转换),系统还能以,5Gsps的采样率采集模拟信号,采样精度为10bit。

2.硬件介绍

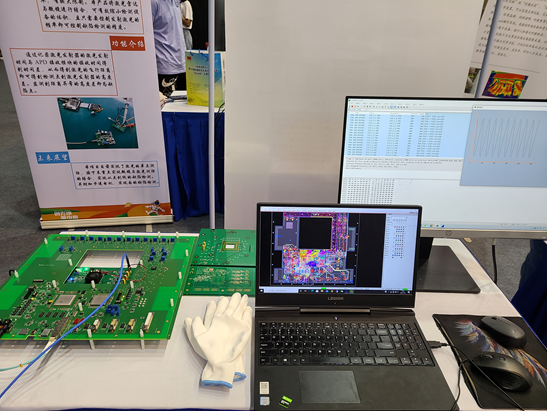

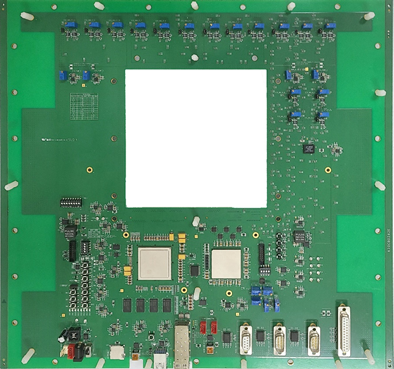

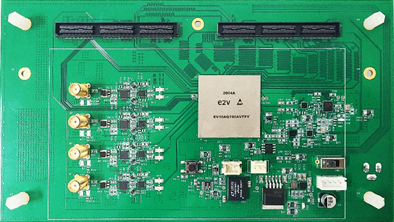

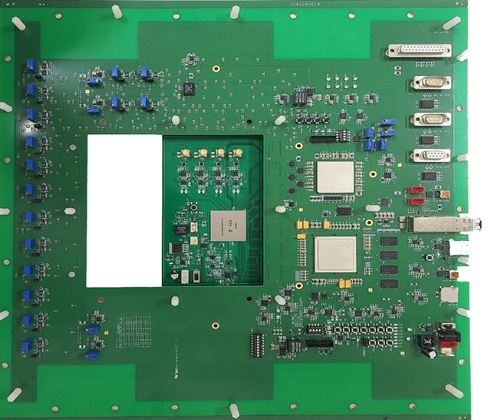

基于系统设计方案,我们设计了通用性强的母板,能够适配于各种类型传感器的数据采集,本项目母板硬件架构由核心处理器ZYNQ UltraScale+及协处理器FPGA构成。具体来看, FPGA结合相关接口构成了控制模块,以ZYNQ UltraScale+与DDR4为核心构成了数据采集模块。其中,控制模块完成芯片寄存器的读写及与上位机的数据交互;数据采集模块则专门负责完成子板数据的采集和缓存工作。下面将分别展示系统母板、子板以及两者连结的图片。

系统母板:

系统子板:

系统子母板连接图:

3.算法介绍

本系统中核心处理器及协处理器中的逻辑设计复杂,同时ADC、DDR4、SFP+的数据读写控制状态机复杂,此外本系统软件还涉及多处理器间数据传输,相互之间通信复杂。具体算法可以概括为一下三项:

1.系统控制模块,负责产生控制信号。(协处理器负责)

2.数据接收模块,负责数据的接收及缓存。(核心处理器负责)

3.数据处理模块,负责将采集的数据进行处理和显示。(上位机负责)

4.模拟信号采集展示

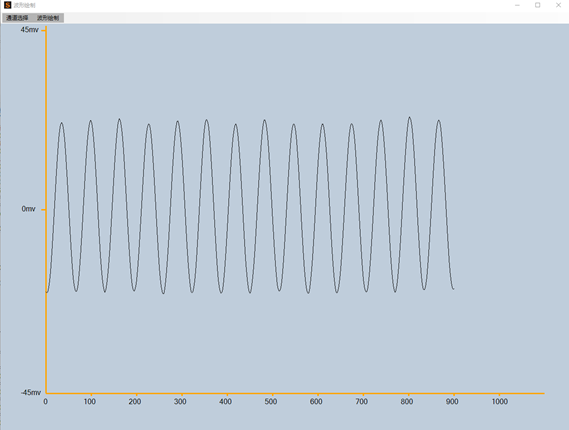

下面我以单通道高采样率的模拟信号采集为例,介绍一下整个系统的工作流程,首先信号源产生500MHz的正弦波信号,通过 SMA接口传入模拟信号采集子板。子板上的ADC芯片完成模拟数字信号转换,将结果通过高速座子传输到母板上的核心处理器Zynq Ultrascale+芯片中,Zynq Ultrascale+芯片实现数据的接收及存储,之后通过高速收发器将数据传输到协处理器中。协处理器完成数据的组包并通过万兆以太网口传输到上位机中进行存储,处理及波形的绘制。

上位机的波形图如下:

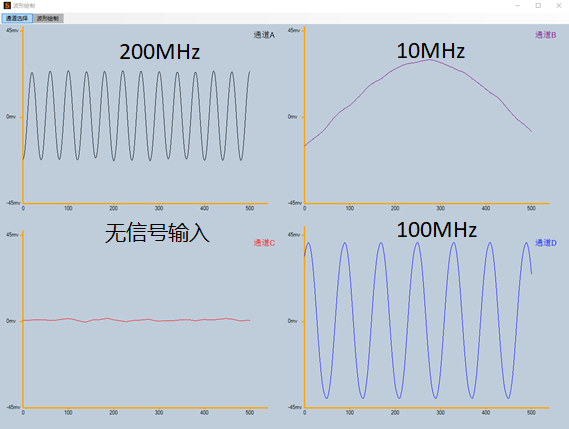

此外系统还能以1.25Gsps的采样率实现四通道模拟信号的同时采集,此时上位机的波形图如下:

5.未来展望

本文以Xilinx公司的ZYNQ UltraScale+作为核心处理器设计的高速数据采集平台,采样速率可达160Gb/s。从软硬件两方面现实了基于并行LVDS接口的传感器的数据采集。本文系统采用子、母板的设计方式将实现了图像数据采集部分与传感器部分的分离,通过更换子板实现多种传感器的数据采集,具有通用性也减小了更换传感器时的开销。此外,通过更换系统子板为模拟信号源提供了采集前的预处理(包括模拟域的放大、滤波及模拟信号-数字信号转换),使得整个系统不仅能采集高速数字信号还能采集模拟信号。

综上,本平台具有自主知识产权,具有强大的通用性及可扩展性,为现今多元化、多场景下的各种模拟信号及数字信号的采集和处理提供了一个高性能的可行性平台,潜在应用场景有超高清视频采集、雷达信号采集、多种传感器数据采集等等,具有实用性。

当然本作品目前处于设计的初始版本还存在的改进空间:

本作品在设计模拟子板时由于ADC芯片国内采购受限的原因选用的ADC芯片的输出数据速率最高仅50Gbps,而母板的100对LVDS接口最高支持160Gsps的数据传输速率。若希望进一步提升模拟信号的采样精度可选用采样率更高分辨率更高的ADC芯片。

更多研电赛作品请查看2021年研电赛获奖作品合集