本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。

团队介绍

参赛单位:中国科学技术大学

队伍名称:Supernova

总决赛奖项:三等奖

1.项目简介

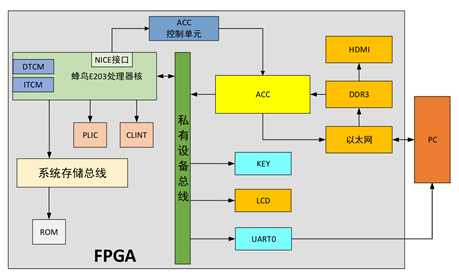

本设计以E203处理器为核心,添加协处理器、神经网络加速器、用于显示的外设(12864型LCD屏和通过HDMI连接的显示器)、输入按键、DDR、以太网等外设构成SoC。

需要识别的图片信息通过以太网从PC发往FPGA,并在DDR3中进行暂存,通过HDMI显示当前将要识别的图片。加速器从DDR中获取图片数据并进行识别,有两个模式供用户选择:单张识别和连续识别。单张模式下加速器将识别结果送入E203核内,并由程序控制LCD显示相应的字符;连续模式下加速器可以直接将识别结果通过以太网返还给PC上位机。

系统整体结构图如下所示:

1.1 E203程序设计

C程序主要由主函数、GPIO初始化函数、PLIC配置函数、GPIO中断函数、UART配置及发送函数、LCD控制函数构成。

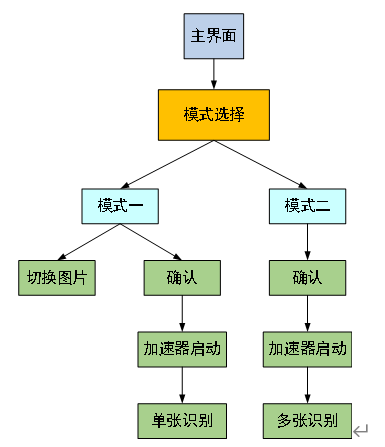

主函数流程图如下图所示。当程序处于模式选择阶段时,第一个GPIO按键中断用于模式切换,第二个GPIO按键用于模式确认选择;当程序处于模式中的选择性识别时,第一个GPIO按键中断用于模式一中的切换当前显示图片的功能,第二个GPIO按键用于实现确认识别当前图片的功能。

1.2 NICE接口与协处理器

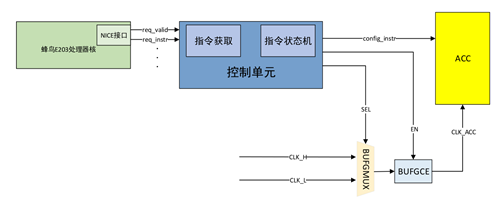

神经网络加速器在设计的时候考虑了两种功能模式切换以及低功耗的需求,对加速器的启动、停止、模式选择的控制均由E203以自定义指令的形式通过NICE接口传递给加速器的控制模块。

本系统里加速器将直接从DDR中读取数据,若没有数据送入时将进行无效运算,为了降低功耗,我们可以对加速器进行启动和关闭操作。同时,本系统的功能包含单张识别和连续识别两种模式,对于单张识别来说速度的需求并不高,使用较低的时钟频率,而连续识别的定位是大量数据集中处理,对速度的要求较高,使用较高的时钟频率,控制图如下:

1.3 UART通信

当用户在程序中选择具体模式后,E203核通过UART向PC发送对应的模式代号,此时PC将选择通过以太网向FPGA发送单张(模式一)还是连续发送多张图片(模式二)。若处于模式一状态下,程序通过UART向PC发送指令是否切换当前将要识别的图片。

1.4 TCP/UDP以太网接口

以太网是目前应用最广泛的局域网通讯方式,同时也是一种协议。以太网协议定义了一系列软件和硬件标准,从而将不同的计算机设备连接在一起。

我们的设计中,图片信息通过以太网从PC发往FPGA,连续模式下加速器可以直接将识别结果通过以太网返还给PC上位机。

为了验证以太网接口的正确性,本文使用wireshark软件和NetAssist网络调试助手来进行调试,wireshark可捕获网口发出的报文,观察发出的报文是否正确,测试结果如下图所示,可见以太网功能正确实现。

1.5 HDMI显示图片

开发板上HDMI接口由Sil9134芯片驱动,在使用时需要先由I2C通信协议初始化芯片寄存器,之后以VGA接口时序将图像数据发送至屏幕显示。

1.6 LCD显示结果

LCD硬件模块我们选用了12864B点阵液晶显示模块,可实现汉字、数字、英文、符号的显示。

1.7 神经网络模型

在本设计中LCD用于显示程序用户界面以及加速器最终识别结果。当用户通过程序完成模式选择并确认识别后,加速器在核的命令下开始识别图片,识别完成后加速器将识别结果通过核送到LCD模块中,LCD模块解码收到的识别结果并在LCD屏上显示最终识别结果。

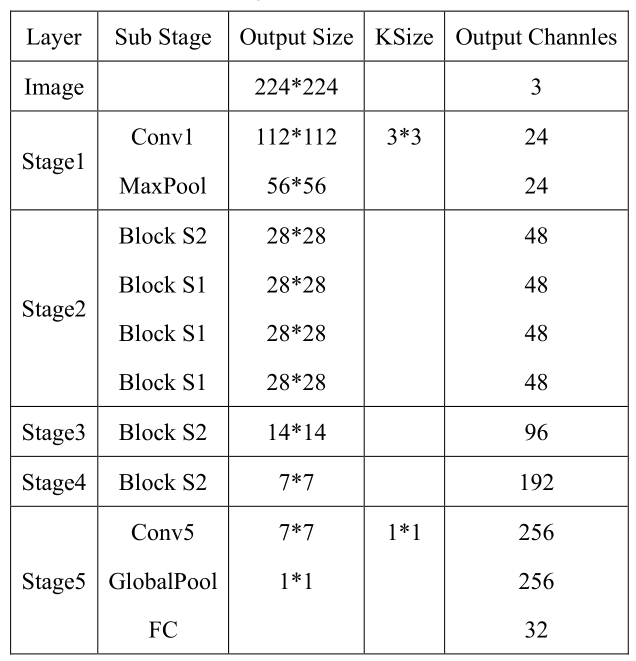

本设计以旷视科技官方的ShuffleNet v2 x0.5版本模型为蓝本,结合FPGA硬件资源的考量,对模型的部分结构做了改进,命名为ShuffleNet v2 x0.1(以下简称为x0.1),可对ImageNet数据集进行32种生活用品的图像分类。

在整个模型上共包括5个Stage,基本框架如下:

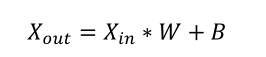

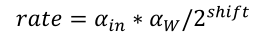

本设计的前向推理过程完全采用有符号整型数据格式进行运算,基本思路为对每一层设定固定的位宽,将计算结果放大或缩小至该位宽的取址范围内。为了进一步节约计算资源,对数据的缩放全部使用移位来进行。

关于权重(W)和偏置(B)的放大,参考下列公式:

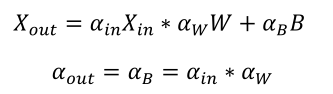

对于偏置(B)的操作,参考下列公式:

参考上面公式,假设上一层输出结果相较浮点运算的放大比例为𝛼𝑖𝑛,权重放大比例为𝛼𝑊,最后移位至固定位宽的位数为𝑠ℎ𝑖𝑓𝑡,这样相比正常的浮点运算,设量化后的整型运算将输出结果放大了𝑟𝑎𝑡𝑒倍,满足如下公式:

该参数在本设计中称该值为放大系数𝑟𝑎𝑡𝑒。由于卷积层的偏置参数的放大需要使用该值,并且每层的放大系数均不同,所以该参数将在量化网络的层与层之间进行传递。

根据以上的量化策略,对 ImageNet 中选出的 32 种生活用品进行量化后推理测试,其量化后的准确率为 90%,相比浮点运算的 96%的准确率有所下降,但考虑到本设计采用了较为激进的量化策略(全程整型运算且放大缩小均采用移位操作而不是乘法),这一结果是完全可以接受的。

1.8 神经网络硬件设计

在本设计中,加速器的应用场景和算法已经固定,且算法模型比较复杂,包含多个分支与 Block,为了更高的性能,我们选用将每层单独实现的方式作为本SoC 中 CNN 加速器的实现方式,之后连接到一起搭建完成整个网络模型。

本设计中使用滑窗法实现特征图的生成,以生成 3*3 大小的特征图为例,具体如图:

输入特征图大小为 2242243,conv 层采用的时33 大小的卷积核,步长为2,padding为 1,最终 conv 层计算得出的特征图大小为 11211224。将上述过程生成的特征图与权重进行相乘得到运算结果后在进行累加,主要的乘加运算由 DSP 完成,DSP 设置为 4 级流水线,每个 cycle 进行一次加法和乘法运算。

Shuffle 层的本意是将,输入数据的多个通道进行打乱,在 FPGA 中,数据流以像素点形式传递,只需将数据按照 shuffle 的顺序重新拼接即可,Shuffle 层的实现原理如下图所示:

2.技术创新点

- 本项目完成了模型训练、前向量化、硬件设计的全流程设计,可以快速迁移到基于各种数据集的图像分类的应用上。

- 实现了两种识别模式:单张识别和连续识别。系统的设计定位为云端处理,可以对大量图片(来自以太网)进行快速识别,即连续识别,此模式实现了 PC 和 FPGA 进行图像数据的传输与通信。

3.参赛体会

通过本项目的研究和探索,我们学习了深度学习的知识和嵌入式系统构建与实操,完成了神经网络加速器的硬件实现及其性能优化。系统性能达到了满意的效果。感谢赛方为我们提供了这样一个锻炼动手能力的机会和交流项目经验的平台。

4.后续工作

进一步优化时序、尝试使用 NICE 接口对加速器进行参数配置(目前的加速器为固定规模,不可修改),优化 PC 上位机等。

作品内容来源于Supernova,非开源,转载请标明出处。欢迎大家参加极术社区组织的有奖征集|秀出你的集创赛作品风采\,免费电子产品等你拿~活动,10月1日截止~