本作品参与极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动。

参与杯赛:IEEE杯

杯赛题目:设计一个满足性能要求的工作在28GHz的功率放大器,电路性能强调在达到一定的输出功率与线性度的条件下,平均输出功率的高能量转换效率(peak and PBO)。

参赛组别:A组、B组

参赛单位:复旦大学

队伍名称:有源负载差动队

总决赛奖项:二等奖

1. 背景与项目简介

随着工业和通信时代的迅猛发展,对带宽、传输速度、传输容量需求也日益增加,第五代通信技术标准应运而生。3GPP(3rd Generation Partnership Project)对5G频率范围的最新定义,分为450MHz-6000MHz的TR1频段和24250MHz-52600MHz的TR2频段,即sub-6G频段和毫米波频段。由于5G毫米波频段所具有的更多频谱资源、更大带宽容量和更低传输时延等特点,是移动通信计数发展的必然走向。

为了提高传输速度以及传输容量,信号的调制方式也越来越复杂。然而,复杂的调制方式加之5G频段更宽的带宽,也使得发射信号在时域的峰均比大大增加,从而对射频前端的线性度、以及峰值和功率回退处的效率提出了更高的要求。作为发射系统中功耗与非线性的主要来源,功率放大器对于信号的发射距离与质量有着决定性的作用。但是,传统的线性功率放大器以及开关类功率放大器均无法同时满足线性度与效率的要求。因此,针对幅度-相位联合调制方式中具有较高峰均功率比的信号研究者提出了兼具高效率与高线性度的架构,并且提出了一些功率回退时的效率提升技术,例如Doherty架构、Outphasing架构以及最新提出的Dual Drive架构。

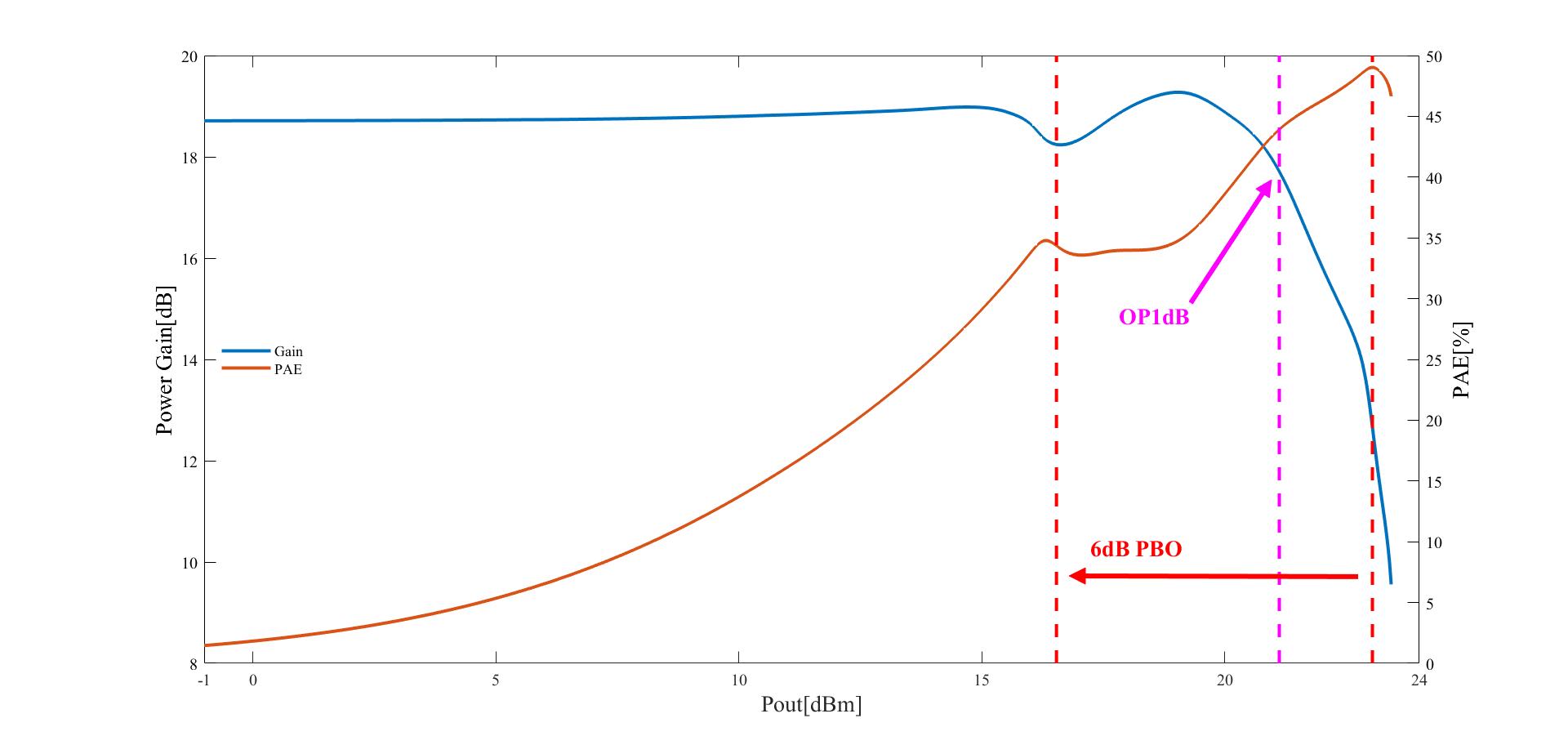

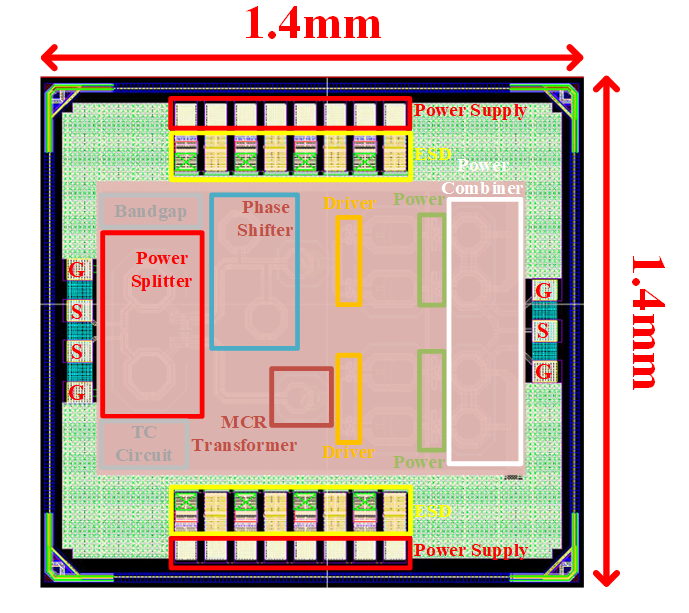

本设计基于TSMC 40nmCMOS工艺,实现了串并联合成Doherty架构功率放大器。功率放大器采用两级差分结构,利用变压器实现输入、输出级间阻抗匹配。在基于各模块的版图后仿真结果的联合仿真中,在1.1V工作电压下,功率放大器实现饱和输出功率23.4dBm,峰值功率附加效率50.0%,增益18.5dB。输出1dB压缩点为21.1dBm,此时的功率附加效率为43.1%。6dB功率回退处的功率附加效率为34.9%。1dB压缩点处功率放大器的直流功耗为290mW。

设计流程:

- 1)首先查阅文献,确定基础架构,本设计决定采用四路串并联功率合成的Doherty架构。

- 2)之后,根据指标确定有源部分,即晶体管的尺寸;并对晶体管进行合理的偏置;最后根据尺寸与偏置,确定晶体管的输入阻抗,以及能使晶体管达到最大输出功率的最佳负载阻抗。

- 3)根据得到的最佳负载阻抗和输入阻抗,设计高效低损耗的无源匹配网络,包括级间匹配与输入、输出匹配。

- 4)进行行为级前仿真,确定电路的大致性能与工作状态。

- 5)在确定PA正常工作在Doherty架构下,且性能达到指标以后,进行版图的绘制与优化。

绘制好每个模块的版图之后进行联合后仿真,确定最终性能。

系统结构框图:

仿真结果:

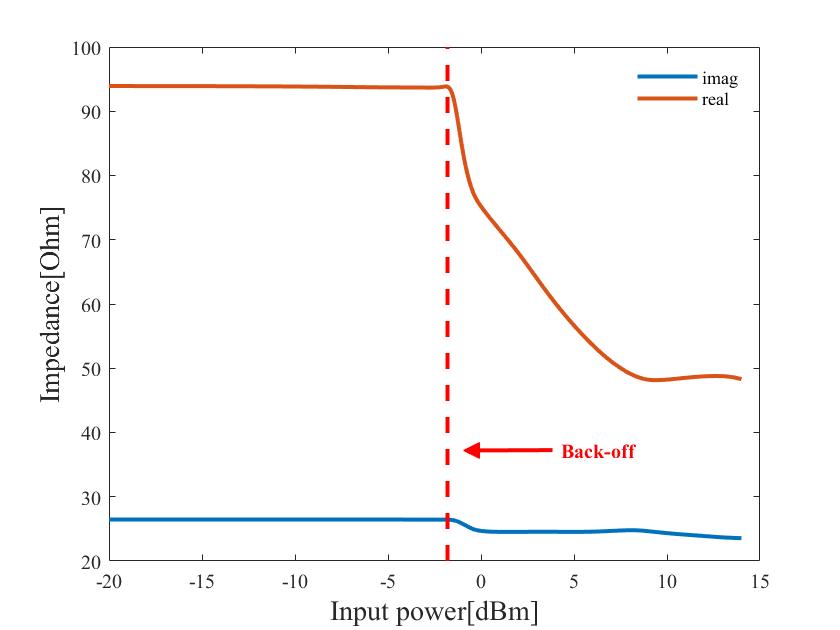

在下图中,可以明显看出当输入功率增大至功率回退处时,辅路功放开启,从而对主路功放的负载进行调制,使得主路功放的输出功率得以继续增加。在峰值功率处(辅路功放完全开启)主路功放看到的负载约为功率回退处(辅路功放刚刚开启)的1/2,证明所设计的功率放大器确实工作在Doherty架构下。

功率放大器所看到输出阻抗的变化:

大信号PSS仿真结果:

整体版图:

2. 设计创新点

- 1) Doherty架构的实现中,需要在主路功率放大器后加入一λ/4传输线起到阻抗倒置器的作用,以实现有源负载调制。由于面积和损耗的问题,λ/4传输线无法进行片上集成,因而常用基于LC的π型网络进行代替。在实际电路中,我们将功率合成网络和阻抗导致网络联合设计,增加版图对称性,减小损耗。

- 2) 放大器输入端为高Q高阻抗网络,要实现宽带匹配难度较大。为了增大工作带宽,本设计中采用了带宽拓展技术,利用主线圈与副线圈不同的谐振峰,取得更宽的工作带宽。

- 3) 由于功率级功放在大的输入功率下会出现增益压缩的情况,恶化线性度。因此本设计引入模拟预失真,提升了整个系统的线性度。

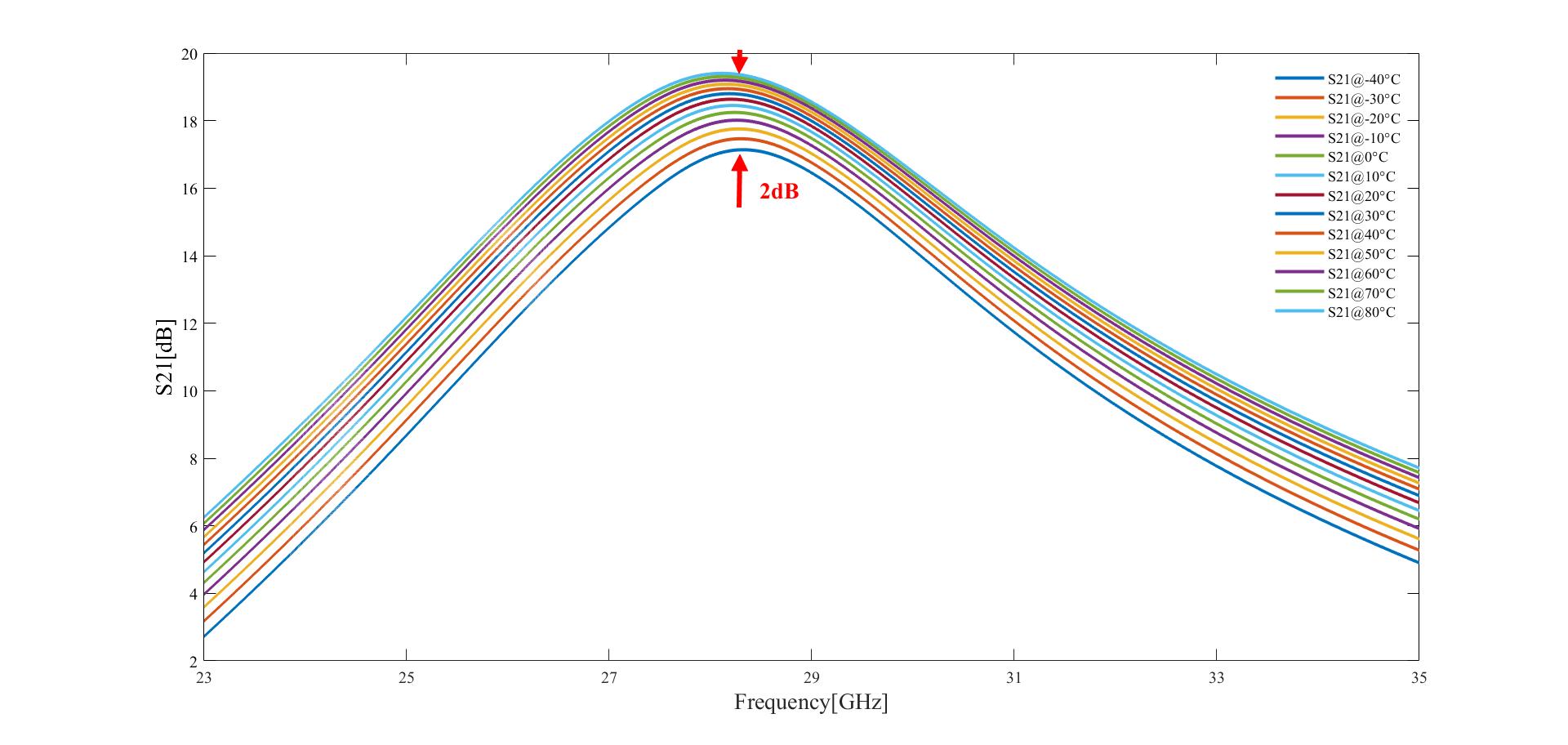

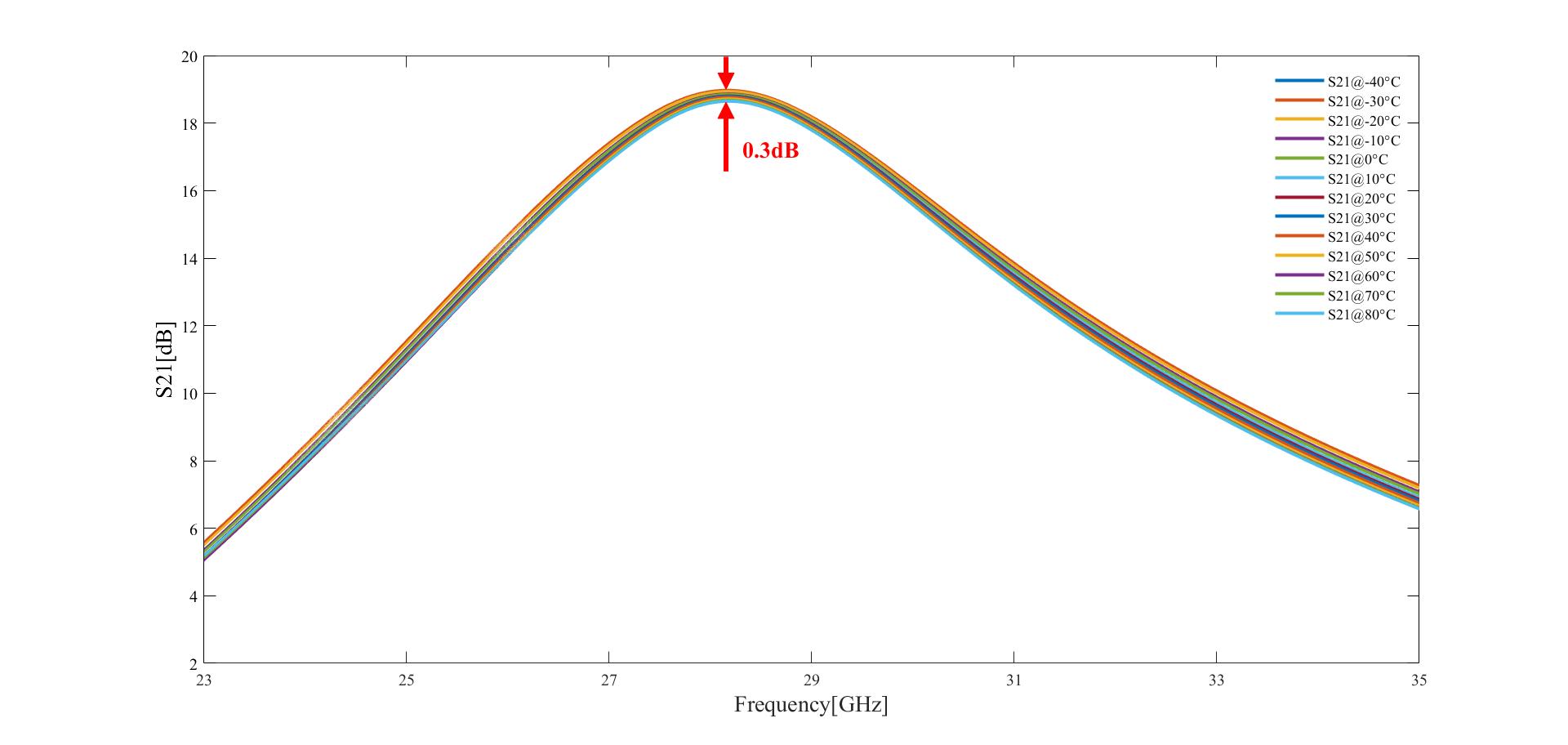

- 4) 在电路中引入温度补偿技术,从而有效减小了因环境温度变化引起的增益波动。

引入温度控制前:

引入温度控制后:

3. 参赛体会

在本次比赛中,很感谢集创赛提供了这样一个平台,我们完整地经历了从文献调研,到搭建核心电路进行验证性的行为级前仿,再到对各个模块进行优化与版图实现的过程,收获了相当完整的设计经验。此外,集创赛也让我们有机会与来自全国各地顶尖队伍进行交流、沟通与切磋的机会,相互学习、进步;同时还提供了相关企业乃至微电子行业的相关讯息,让我们可以更全面地了解到整个行业的动向,为我国芯片领域贡献自己的绵薄之力。

4. 未来展望

- 1) 对版图的精确优化。本文分析中有分析寄生对毫米波频段功率放大器的性能影响。但是,目前的设计中,对版图的整体优化仍然不够准确。下一步,将基于更完善的电磁场仿真,对这些部分的寄生做更全面的考虑;

- 2) Bonding Wire的考虑。芯片从Pad上连接到封装引脚上,需要借助Bonding Wire。Bonding Wire本身会引入一定的电感,并且不同的引线之间还存在互感。这会引起信号之间的耦合,以及阻抗变换网络的偏移。下一步,将对这部分的设计加以考虑。

作品内容来源于有源负载差动队,转载请标明出处。欢迎大家参加极术社区组织的有奖征集|秀出你的集创赛作品风采,免费电子产品等你拿~活动,10月1日截止~