1 - APB引言:

首先考虑一下以下的场景

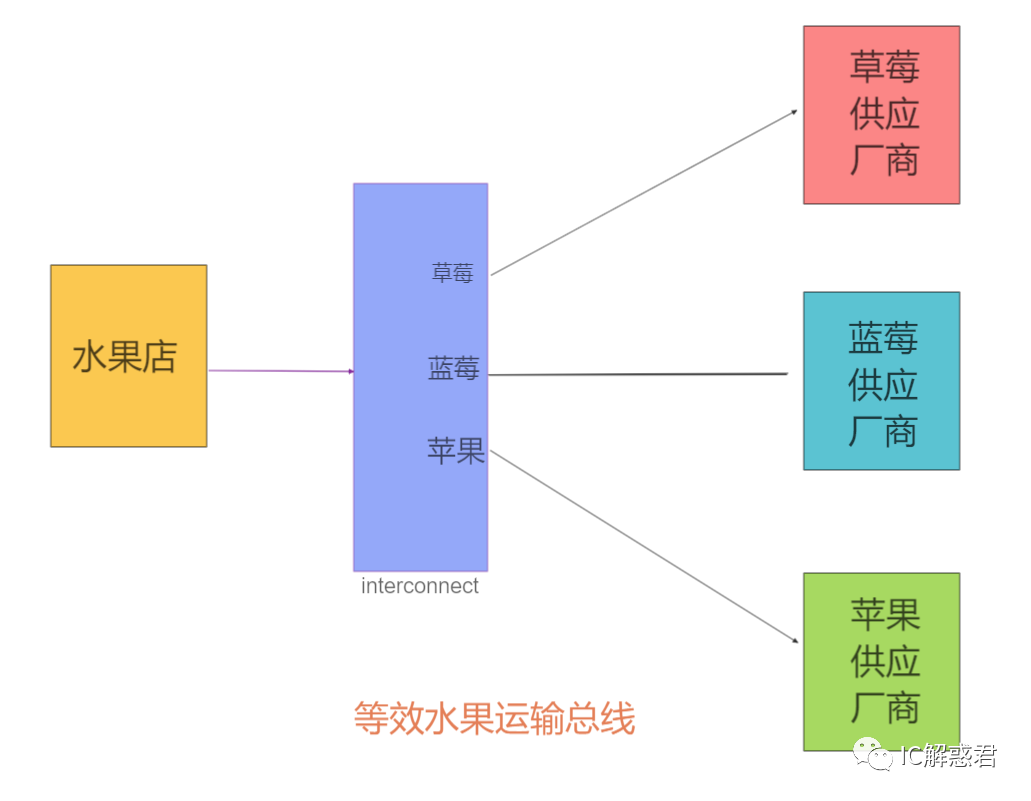

有一个水果店,只卖三种水果,分别是草莓、蓝莓和苹果。水果店按照客人购买量进行水果的进货。厂商根据水果店的要求,提供对应数量的水果并运送到水果店。

每次交易如下:

水果店根据需求使用大喇叭广播自己的订单需求,说出想要订货的数量,对应厂商提供水果上门,水果店签收。

使用这条水果运输总线类比AMBA总线的APB总线:

概念1: 主机(Master)

订单的发起只能由水果店发起,所以水果店在这条水果运输总线里面运输水果占有主动地位。

类比:

在APB总线里面,数据的传输只能由主机发起,其他部分响应主机操作。

概念2:从机(Slave)

当水果店发起订单之后,和订单匹配的厂家需要提供对应的水果送到水果店。这里面的厂家只能根据要求送水果,自己不能随便向水果店送水果(没有主动的权限)。

类比:

在APB总线里面,数据的回复由从机完成,从机只能完成主机发起的操作,自己不能发起操作然后完成操作。

概念3:单主机(Single Master)

在这条水果运输总线里面,当前只有一个水果店,也只有这个水果店可以发起订单需求,所以在这条水果运输总线里面,只有一个主机(按上图来说)。

类比:

在APB总线里面,有且只有一个主机可以连接到APB总线接口,其他的只能连接从机(外设),所以APB总线只支持单主机模式。

概念4:总线协议(Bus Protocol)

在这条水果运输总线里面,水果店按照自己的需求,发起订单,厂商提供水果,水果店确认收到。这一个完整的流程以及顺序被称为水果总线在传输水果的协议。

类比:

在APB总线里面,主机先发起要访问的外设地址,外设根据要求返回数据,主机收到数据,这一个完整的流程被称为APB总线协议。

所以我们可以根据上面得出(单主机)总线的正式概念:

总线是被总线上所有的部件所共享的一组通路(连线),对于单主机来说,如果该主机想要与其中的外设部件进行通信(获得数据),需要将地址(厂商名字)、数据(水果)、命令(进货还是退货)放到总线上,其他的从机部件对总线上的数据进行侦听,检查地址数据和命令的是否与自己相关,然后相关部件做出响应。

概念5:命令总线、数据总线、地址总线

在这条水果运输总线里面,水果店按照自己的需求,使用大喇叭发出进货还是退货(命令)、哪个厂家(地址)、退货的水果或者进货的水果(数据)。

类比:

在APB总线中,有地址线(PADDR),命令线(PWRITE、PENABLE、PESEL)和数据线(PRDATA、PWDATA)。

PS:举的例子和APB不是一一完全对应,但是表达的意思相同

2 - APB总线协议详解:

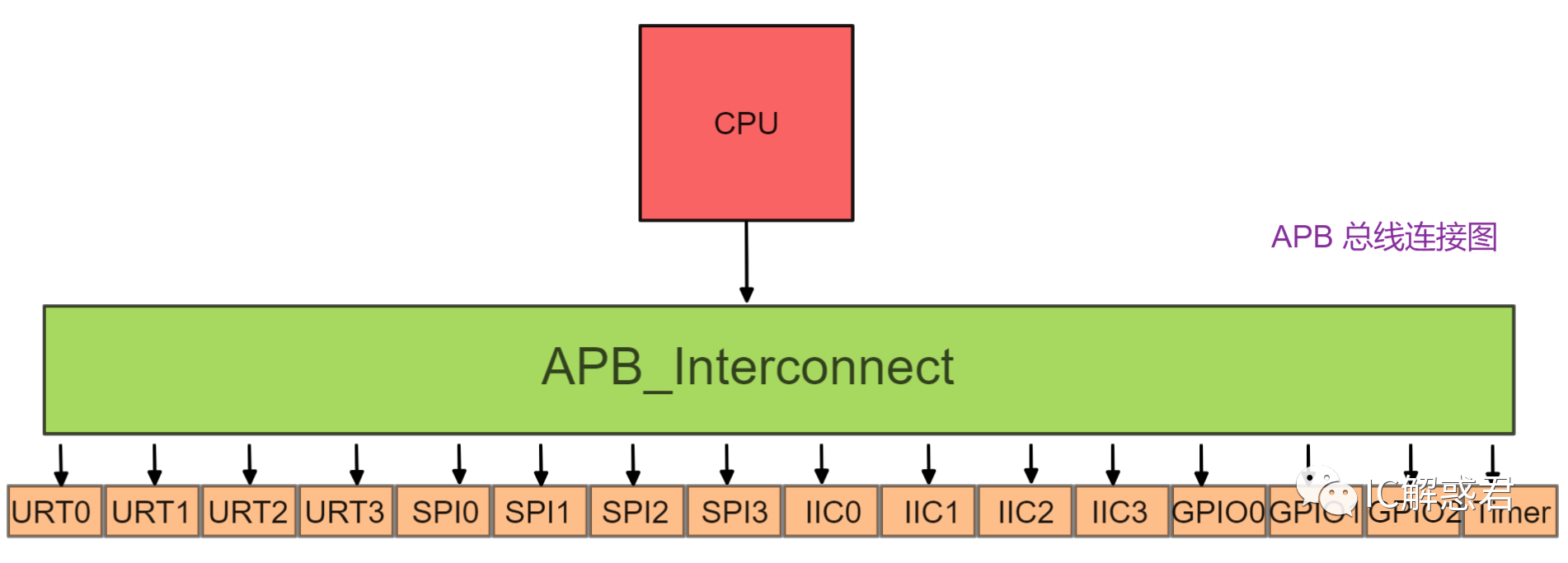

2-1 APB在SOC内使用的部分:

如图:

CPU :CPU是操作的发起者,CPU发起读写外设数据的操作。

APB\\_Interconnect :根据上文所说的总线协议和传输信号的要求,构建出来的设计实体,该实体接收CPU发出的数据和指令,然后广播到每一个外设部件。

SLAVE:对APB\\_interconnect输出数据和指令进行响应。

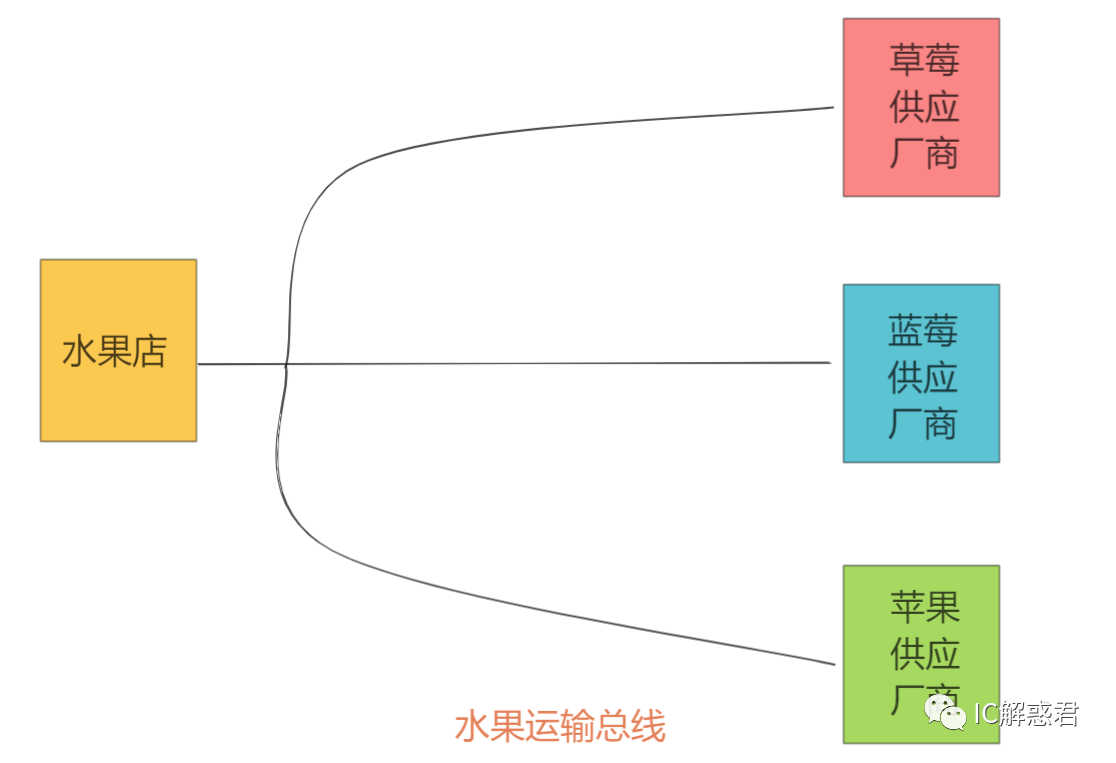

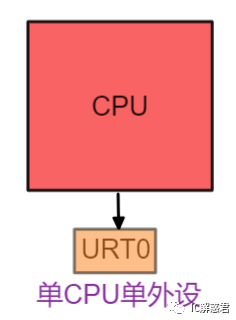

Q1 : 是否可以不需要APB\\_interconnect,APB\\_Interconect的作用是什么?

如上图,当CPU只有一个外设,那么直接可以和外设相连,不需要APB\\_Interconect。此时CPU的发出的指令和操作只会发给URT0,不需要地址来仲裁。如下图:

但是当CPU需要连接多个外设的时候(CPU只管发出地址和命令),根据CPU地址范围分配表:

(1)APB\\_Interconect对每一个外设设置地址,然后APB\_Interconect根据CPU发出的地址,选中对应地址的外设,把CPU的地址和指令传输到该外设 [地址路由仲裁]。

结论:是否需要APB\\_interconnect根据应用而定,如果只是单个的外设连接CPU(很少出现),可以直接连接CPU和外设通过APB总线。不需要APB\\_Interconect,但是当外设数目变多,自然而然的就引入了不同外设的区分,所以当多个外设的时候,需要引入APB\\_Interconect来做这些相关的处理。

用水果店类比:水果店用大喇叭发出订单,所有的水果厂家进行侦听,然后响应订单,或者假如水果厂家没有侦听装置,可以在水果店和水果厂家之间加一个Interconect,这个Interconect的作用是当收到某一个厂家的名字时,根据厂家名字和地址的关系,把需求单独发送给对应的厂家,专门通知供应厂家(也就是选中外设)。

2-2 APB总线接口:(AMBA APB 2.0)

系统信号

PCLK APB总线的时钟,APB所有的操作在时钟下进行,上升沿有效。

PRESETN APB总线复位信号,给APB 总线电路结构初始值

地址总线

PADDR 传输APB 想要操作的地址

命令总线

PSELx 根据地址生成选中的信号

PENABLE 根据地址生成使能的信号(APB协议要求)

PWRITE 传输APB主机的读写操作,1写0读

数据总线

PRDATA 外设给主机返回的数据通道

PWDATA 主机需要给外设写入的数据通道

根据上图,结合之前的类比和概念我们基本就可以知道APB该怎么运行。

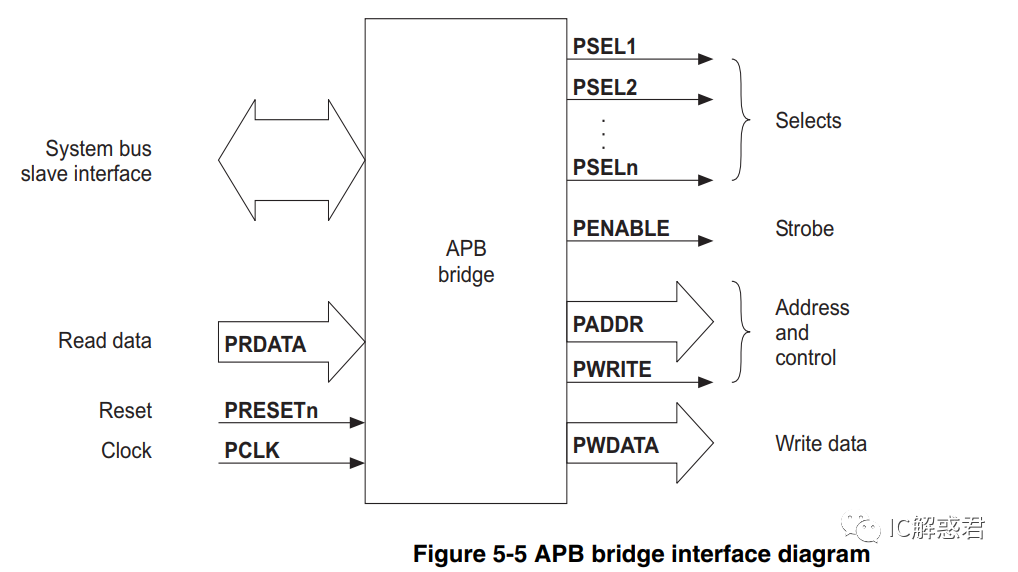

2-3 APB Bridge示意接口(APB\\_Interconect)

根据AMBA APB手册,截取APB Bridge接口:

图左边的接口System Bus Slave Interface,连接APB 主机(即上面的CPU),这个接口也是APB完整的接口,包含上面举例的信号。图右边和左下面的接口连接多个SLAVE,其中PSELn有多个,每个对应不同的SLAVE。其他信号对于SLAVE是一致的,因为PSELn已经可以选中不同的SLAVE来接收传输的共享信号了。

2-4 APB BUS时序图(AMBA APB 2.0手册)

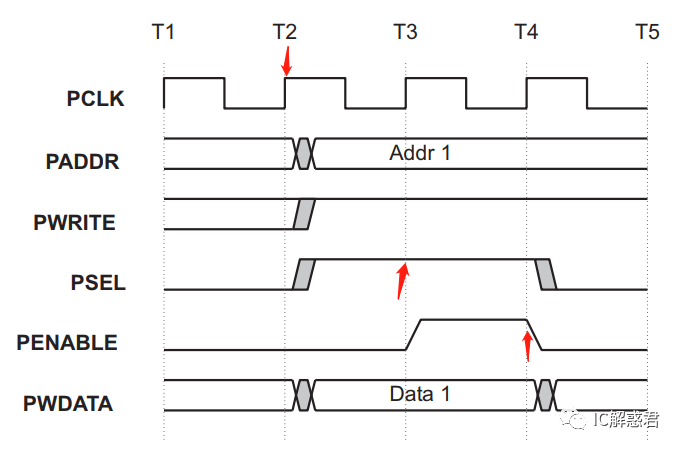

写传输:

如上时序图,主机在T2时刻把所要访问的地址,命令和数据全部放到APB总线上,沿着组成APB的接口的金属线传播到从机接口处。在T3时刻,从机发现自己的PSEL信号为高,就知道主机选择它来处理数据的写操作,此时从机内部准备好处理数据的准备动作,在T4时刻,从机完成总线上数据采样并进行内部数据处理。

WriteEnable = PSEL & (!PENABLE) & PWRTIE ;

或者

WriteEnable = PSEL & PENABLE & PWRTIE ;

always @ (posedge PCLK or negedge PRESETn)

begin

if(~PRESETn)

begin

reg_paddr <= 'h0 ;

reg_pwdata <= 'h0 ;

end

else if(WriteEnable)

begin

reg_paddr <= PADDR ;

reg_pwdata <= PWDATA ;

end

end

TODO:外设内部处理数据

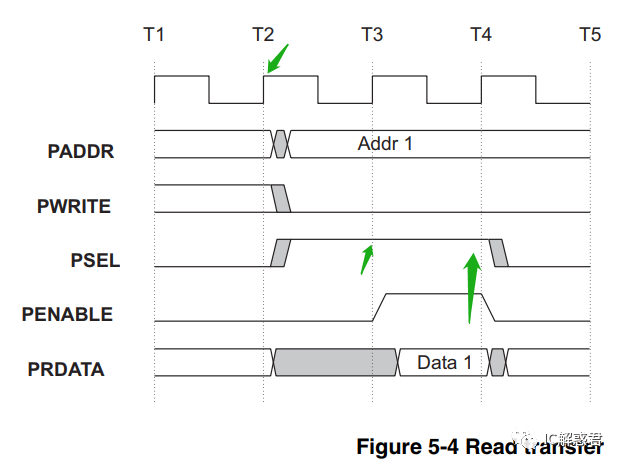

读传输:

如上时序图,主机在T2时刻把所要访问的地址,命令和数据全部放到APB总线上,沿着组成APB的接口的金属线传播到从机接口处。在T3时刻,从机发现自己的PSEL信号为高,就知道主机需要它内部的数据(PWRITE ==0),此时从机内部准备好返回数据并把返回的数据放在数据总线上,在T4时刻,主机完成总线上数据采样得到需要的数据。

ReadEnable = PSEL & (!PENABLE) & (!PWRTIE)

always @ (posedge PCLK or negedge PRESETn)

begin

if(~PRESETn)

begin

reg_paddr <= 'h0 ;

reg_prdata <= 'h0 ;

end

else if(ReadEnable)

begin

reg_paddr <= PADDR ;

reg_prdata <= 外设内部产生的数据 ;

end

end

assign PRDATA = reg_prdata ;

2-5 APB BUS的优缺点:

优点:设计简单,时序简单,用在不需要高性能总线的外设上。

缺点:每个数据的传输都需要两个时钟周期,这样的话,APB BUS满载的带宽也只有50%,带宽利用率不高。

下一站:

漫谈AMBA总线-AHB

https://mp.weixin.qq.com/s/zXwmwxiWP2POACTEy3tJmQ

微信关注IC解惑君,IC设计不迷路。

一起学习一起成长,一起成为最好的工程师