本文介绍了两篇芯片设计顶会(ISSCC2020)文章中设计的面向超低功耗的语音唤醒芯片。在智能计算/人工智能领域,芯片占整体技术栈价值的40-50%,而在其他领域只占10%以下,这是芯片领域近几十年最大的机会。也希望看到越来越多国内类似的自主设计芯片产品的出现。本文引用网上对两篇文章的介绍来给大家分享一下语音唤醒芯片的关键技术。欢迎大家留言讨论。

作为新兴信息产业的重要应用领域,物联网的万亿级别市场正在逐步形成,超万亿级的设备和节点将通过物联网技术实现万物互联和万物智联。受限于体积、重量和成本等因素,物联网节点(如可穿戴设备、智能家居节点、无线传感器节点、环境监测节点等)需要在微型电池或能量收集技术进行供电的情况下,能够持续工作数年乃至十年以上,这对芯片提出了苛刻的低功耗要求。

目前,降低物联网芯片功耗的主要研究方向是基于周期性工作模式的专用型唤醒芯片(例如:专用语音识别唤醒芯片),通过让芯片处于周期性的“休眠-唤醒”的切换状态,来实现降低功耗的目的;然而,物联网节点通常工作在“随机稀疏事件”场景下,为了避免丢失随时可能发生的事件,通常需要“休眠-唤醒”的频率远高于事件的真实发生率,从而导致了严重的功耗浪费。

第一篇文章由北京大学信息科学技术学院微纳电子系的黄如院士-叶乐副教授课题组,与浙江省北大信息技术高等研究院、芯翼信息科技(上海)有限合作完成。论文题目为Ultra-low Power Asynchronous Event-Driven Wake-Up Chip foe IoT Applications。

据悉,为突破现有物联网芯片的功耗瓶颈,研究团队首次提出的多级流水异步事件驱动型芯片架构,将传统的“定期上报”的周期性工作模式,转变为“出现异常再报警”的异步事件驱动型工作模式。这一全新的设计,显著降低了物联网芯片在“随机稀疏事件”场景下的功耗。

此外,课题组还提出了时域屏蔽型阈值交叉模数转换器技术,解决了“噪声误触发导致功能错误和功耗上升”难题;设计了基于时域脉冲信号处理技术的多功能信号特征判决器电路,满足了物联网唤醒芯片对通用性的需求;去掉了时钟信号和时钟网络,将芯片在待机状态下的主要功耗来源彻底摒弃。并设计了基于时域脉冲信号处理技术的多功能信号特征判决器电路,通过离线或在线软件定义的方式实现了对幅度、斜率、时间间隔、波峰、波谷等信号特征的组合判决,满足了物联网唤醒芯片对通用性的需求;此外,该芯片无时钟信号和时钟网络,去除了芯片在待机状态下的主要功耗来源。

基于上述创新技术,课题组研制了一颗极低功耗无时钟的物联网通用唤醒芯片,平均功耗仅为57纳瓦,比当前国际同类工作的最好水平提升了30倍。该芯片演示了心率异常预警、心电T波异常预警、癫痫预警、语音关键词包络唤醒等典型物联网应用场景,芯片与微控制器MCU芯片等高性能模块配合,可以在保证极低功耗的前提下实现更多复杂的物联网唤醒功能。该工作首次提出的异步流水线事件驱动型架构,为极低功耗物联网芯片领域的研究提供了一种突破现有功耗瓶颈的研究思路和解决路径。

以上内容来源于知乎:

https://zhuanlan.zhihu.com/p/...

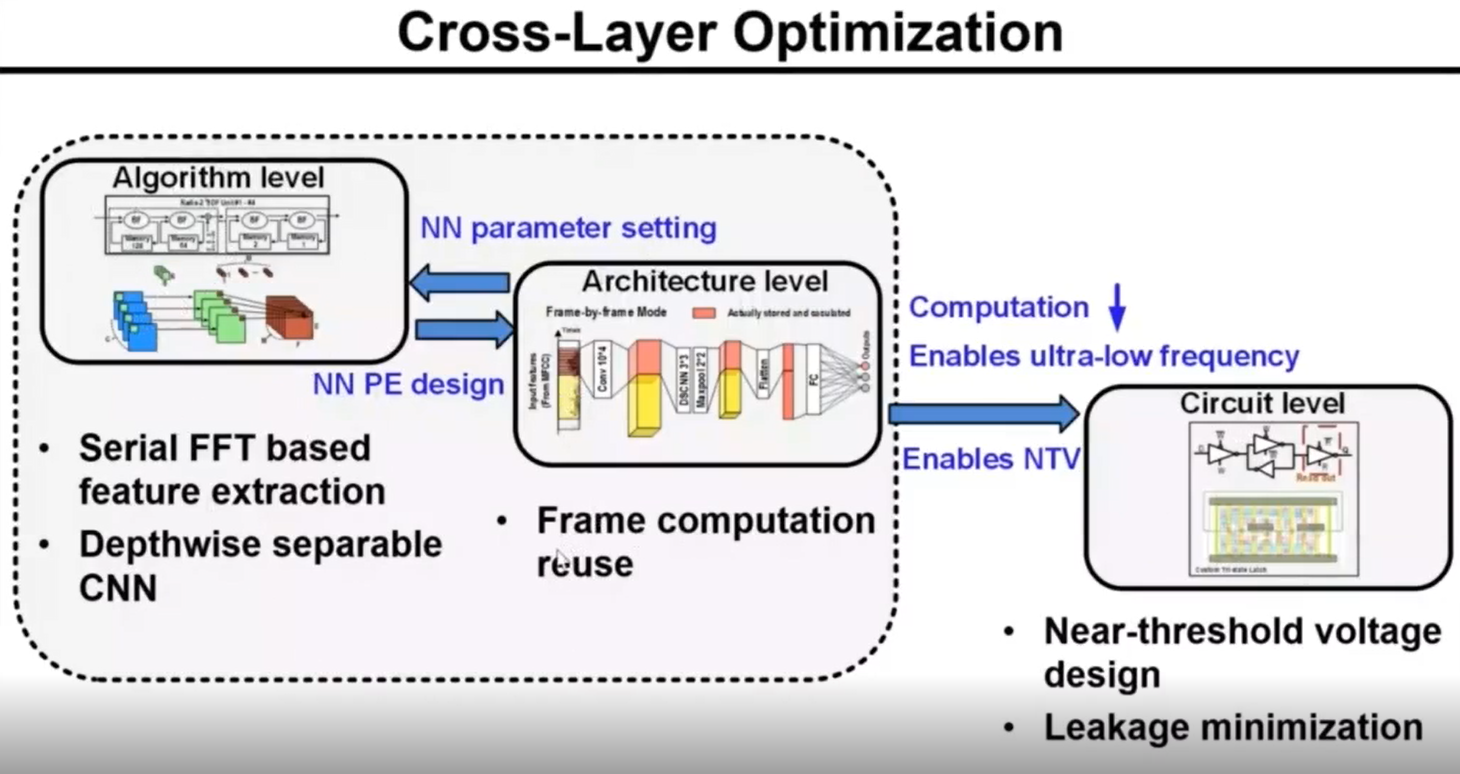

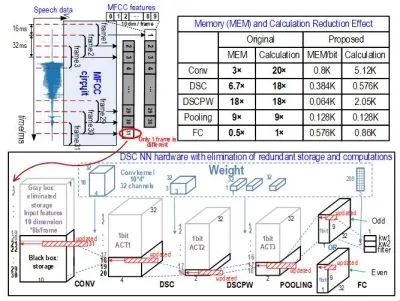

第二篇论文是关于语音关键词唤醒的低功耗AI加速器的论文:A 510nW, 0.41V low-memory, low-computation keyword spotting chip using serial FFT based MFCC and binarized depthwise separable convolutional neural network in 28nm CMOS。该语音唤醒智能芯片从算法、芯片架构和电路三个层次统筹优化,如下图所示,算法级采用基于串行FFT的MFCC特征提取和深度可分离卷积神经网络,极大降低了计算量和存储量;架构级提出了语音数据的逐帧数据复用方法。这两个级别联合使得芯片可工作在极低频率40kHz下,进而促成了全芯片的近阈值设计和超低漏电的定制存储器电路,最终现了史上功耗最低的关键词唤醒电路,功耗仅为510纳瓦**。

语音唤醒智能芯片的算法、芯片架构和电路三个层次统筹优化

独特的创新技术如下:

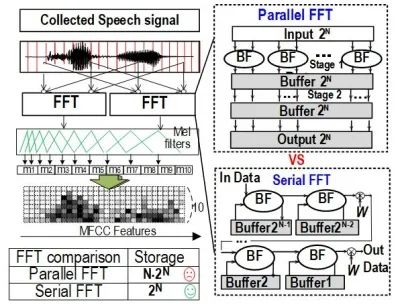

(1)提出并实现了基于串行FFT的梅尔频率倒谱系数(MFCC)特征提取电路,同时用混合量化逐层降低硬件实现代价。FFT是特征提取中计算最复杂、功耗最大的模块,与传统并行FFT相比,提出的串行FFT电路的存储量降低8×,功耗降低11×;

MFCC特征提取电路结构及亮点

(2)深度可分离卷积神经网络的二值化轻量级神经网络,与CNN相比存储量和计算量均降低7×;基于此设计了契合算法的神经网络硬件架构,由计算单元(PE)阵列(含32个乘累加MAC单元)、存储模块、数据映射模块及控制状态机组成;

(3)提出了逐帧数据复用技术,利用语音应用中相邻两帧输入数据的计算存在大量重复导致的卷积计算中存在大量重复计算的特点,对神经网络中的数据的存储和计算量进行压缩,使得计算量降低17.4×,中间存储量减少3.5×;

深度可分离卷积神经网络架构及逐帧数据复用技术

(4)全芯片近阈值设计与定制的极低漏电存储器,再次降低功耗。前面算法级和架构级的双重优化,使得整体神经网络加速器仅需640个周期就能完成一轮推理,在16ms的帧间隔内完成即可,因此工作频率仅需40kHz下,这就促成了全芯片可采用近阈值设计。近阈值设计的难点有二:存储器和漏电控制。我们定制了能工作在低电压下、且具有低漏电的latch型存储器,实现神经网络与MFCC所需的片上多块、多类型的小容量存储。定制Memory比工艺厂提供的SRAM编译器生成的同等大小的SRAM模块的漏电低了12倍,且可与其他数字电路一起工作在0.41V。

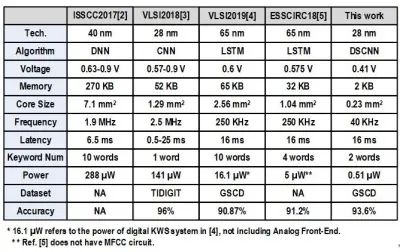

这些技术应用在T28nm的神经网络加速器,实现了史上最低的关键词唤醒电路芯片,0.41V电压下整体功耗仅0.51uW,比国际同类研究降低了10到564倍,见对比表格。

以上内容来自网页:

https://www.seu.edu.cn/2020/0...

以下是第二篇文章作者介绍的视频:

"小爱同学"之类语音唤醒芯片相关技术介绍

作者:网络交换FPGA

原文链接:网络交换FPGA

推荐阅读

更多IC设计技术干货请关注IC设计技术专栏。