rk3568硬件开发笔记(第二篇 ) 外围模块设计

前言:

rk3568处理器属于中高端通用型SOC,RK3568兼具CPU、GPU、NPU、VPU于一身,是一款高性能低功耗四核应用的处理器。

rk3568采用22nm先进制程工艺,集成4核arm架构A55处理器和Mali G52 2EE图形处理器,支持4K解码和1080P编码。RK3568支持SATA/PCIE/USB3.0等各类型外围接口,内置独立的NPU,可用于轻量级人工智能应用。

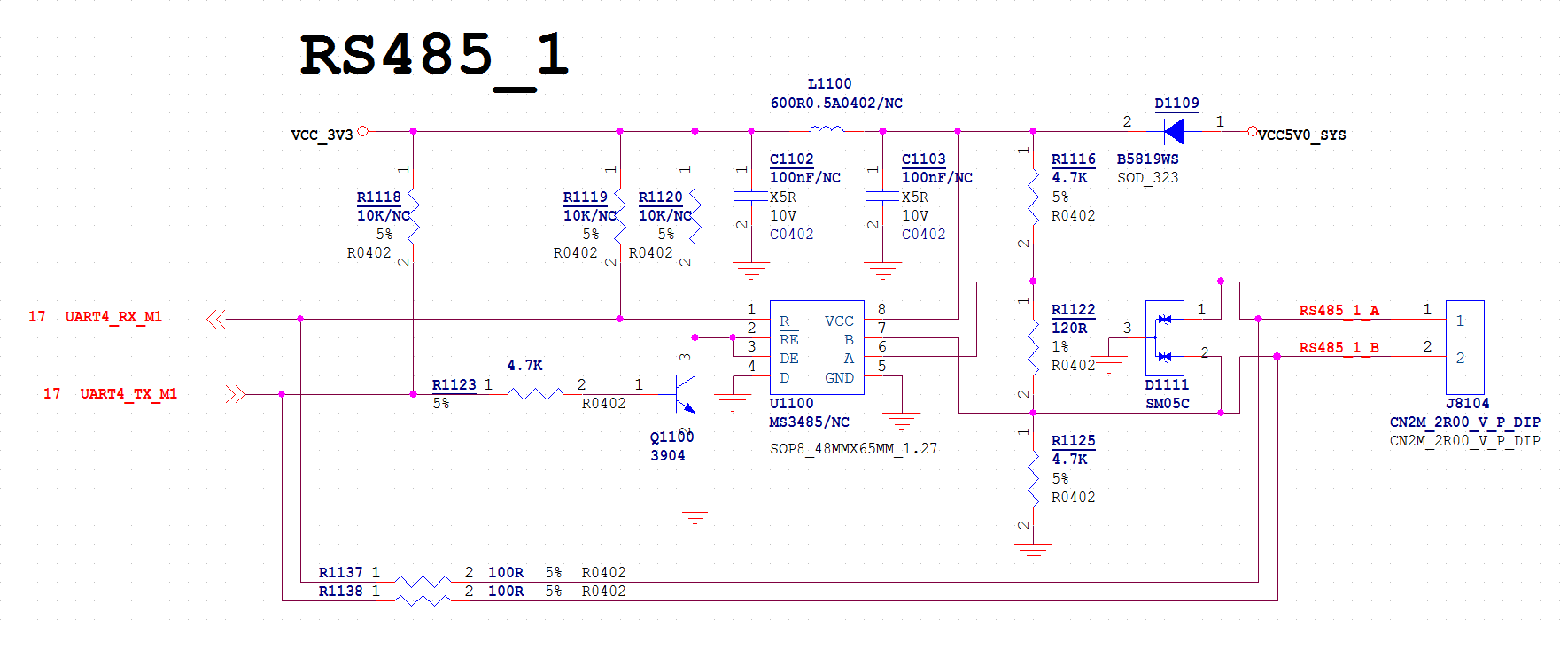

第一节:RS485电路

如图所示,RS485芯片MS3485的RE使能低电平有效,DE的作用为定义芯片的收与发模式。其中,使能信号RE和DE可采用TX控制,节省资源,因为加了一个三极管3904,所以在TX输出高电平时,RE=DE=0V,进入接收模式;TX输出低电平时,RE=DE=3.3V,进入发送模式。

在A上加上拉,B上加下拉电阻,主要原因是:RS-485总线在空闲(idle)状态时,电平是不固定的,即电平在-200mV~+200mV之间,收发器可能输出高也可能输出低,UART在空闲时需要保持高电平的,如果此时收发器输出一个低电平,对UART来说是一个start bit,会导致通信异常。(所以RX需要加上上拉)其中:

① A上加上拉,B上加下拉,接反数据通信也可能出错。

② 某些收发器内部集成上下拉电阻,则外部不需要再添加。

电路特点:

1、此电路兼容3.3V和5V,注意选贴;

2、在A、B线上加入TVS二极管D1111,能够提高电路的抗浪涌,防静电;

3、此电路兼容TTL输出,此时贴R1137 R1138 ,而U1100不贴;

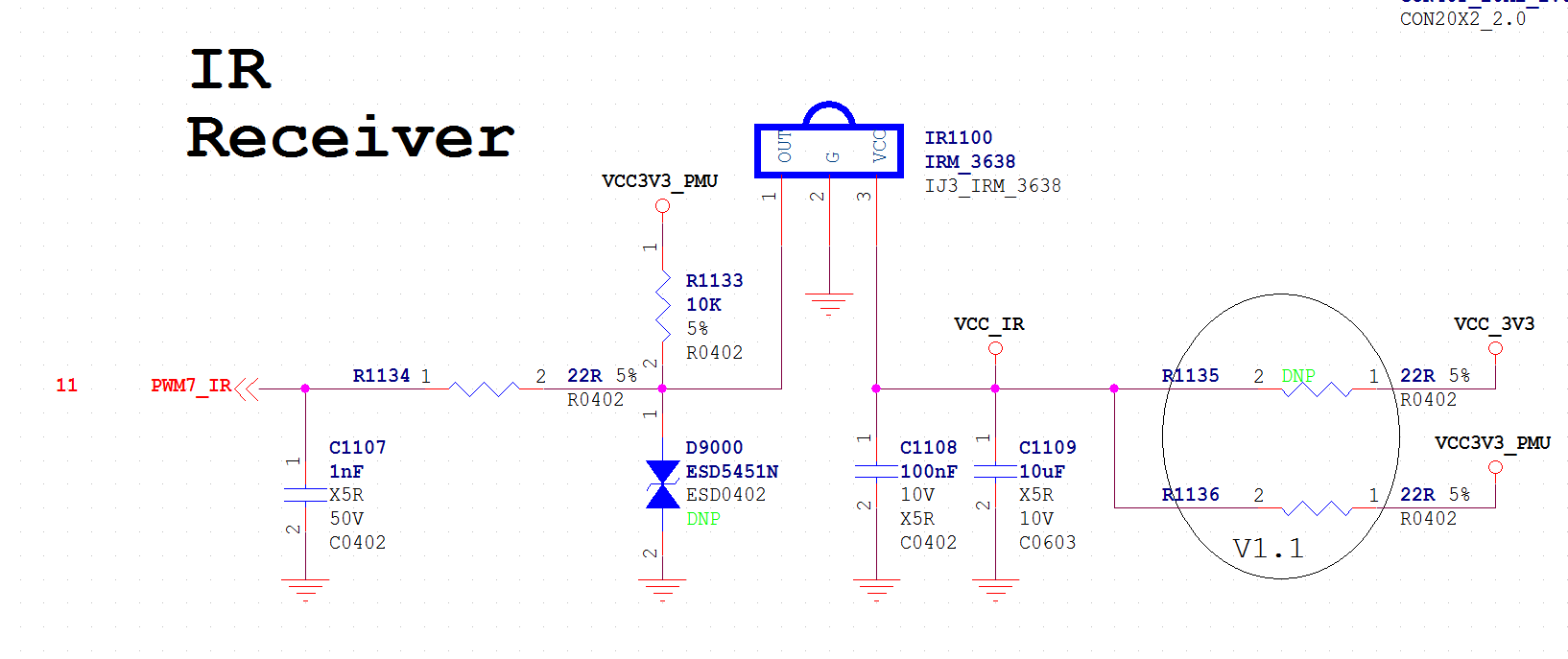

第二节:IR红外接收电路

讲解:

1、IR模块通过PWM信号传输给RK3568,注意接到PWM引脚,同时外部加上拉电阻,引脚加ESD保护,预留电容滤波,和阻抗匹配;

2、接地

3、3.3V供电,如果选VCC\_3V3那么只能在开机之后才能遥控,如果选VCC3V3\_PMU,这个电在DC插入后一直有,那么就可以在关机状态下进行开机控制;

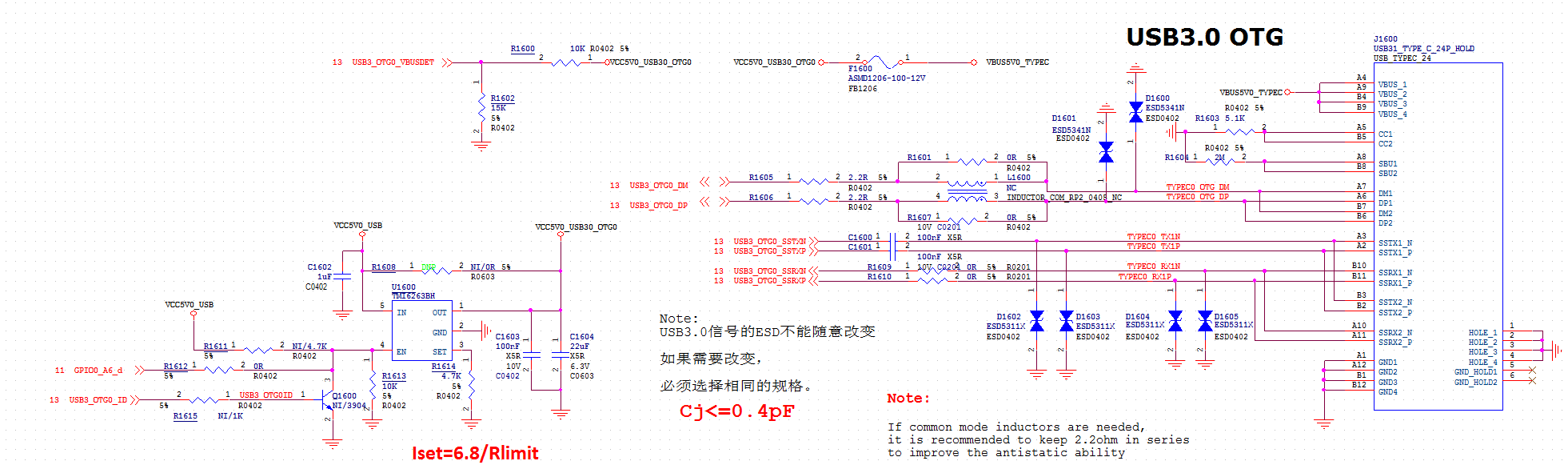

第三节:typec接口设计

原理图讲解

1、此typec接口可以实现正反插;

2、因为项目不需要typec充电功能,cc脚直接下拉;

3、各个信号线需要加ESD保护,在插拔usb线时容易产生静电;

4、信号线加共模电感和匹配电阻,防止EMC EMI干扰;

5、注意SSTX信号需要加电容;

6、ESD保护器件对寄生电容有严格要求,Cj<=0.4pF;

7、USB接口需要加限流电路防止外设损坏引起电路烧毁,输出电流大小通过R 1614设置,计算公式为Iset=6.8/Rlimit

附图

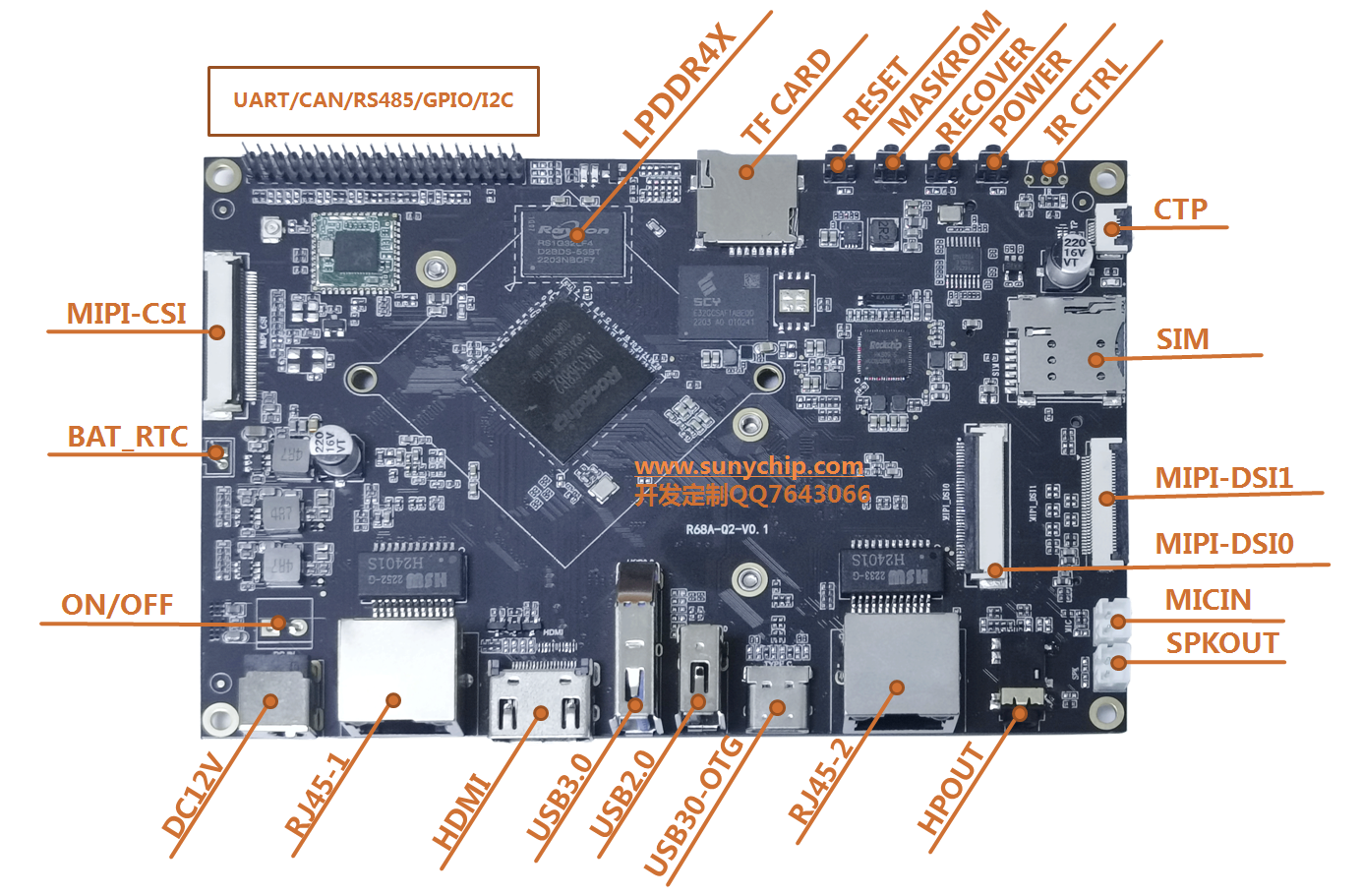

以上电路设计来源于新创云R680A-Q2开发板