近日,由意大利国家核物理研究所(INFN)主导的国际天文观测研究团队,在切伦科夫望远镜阵列(Cherenkov Telescope Array Observatory, CTAO)项目中取得了重要突破,其最新研究成果已正式发表在《IEEE Transactions on Nuclear Science》这一期刊。

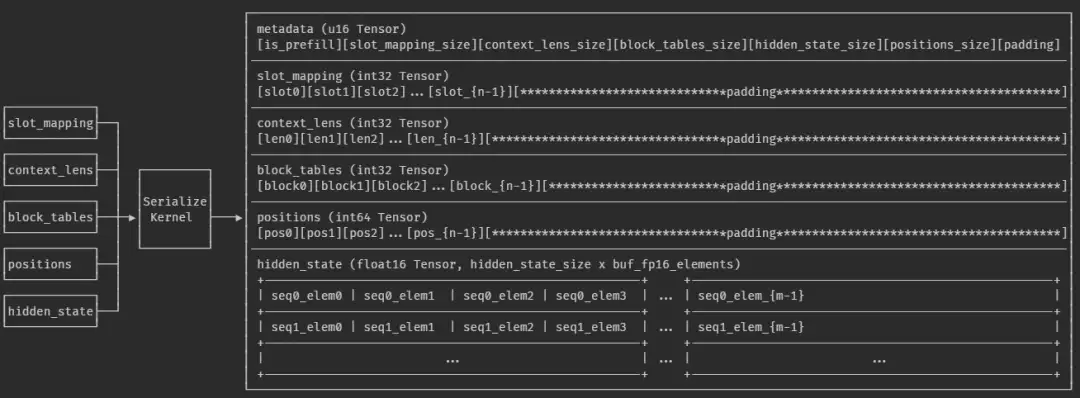

在大模型时代,对极致性能的追求永无止境。作为一门为大规模并行计算而生的高性能语言,Triton 正凭借其出色的开发效率和接近硬件极限的性能,受到越来越多AI工程师的关注。在达坦科技,我们也在积极拥抱 Triton,利用它来开发和优化GPU算子,以加速大模型的推理效率。

达坦科技始终致力于打造高性能AI+Cloud基础设施平台,积极推动AI应用的落地。达坦科技通过软硬件深度融合的方式,提供AI推理引擎和高性能网络,为AI应用提供弹性、便利、经济的基础设施服务,以此满足不同行业客户对AI+Cloud的需求。在本周的前沿技术分享中,我们邀请到了软硬件联合开发工程师陈添,来为大家分享Triton ...

2025年,全球开源芯片开放架构技术的盛会——第五届RISC-V中国峰会将于7月16日至19日上海张江科学会堂盛大召开。本届中国峰会将聚焦人工智能、高性能计算、汽车电子、软件与生态系统、教育与人才培养、前沿技术创新、EDA、投资与并购等九大热门话题,采用“主论坛+专题研讨+生态展览+开发者活动”的多元形式,汇聚全球顶尖专...

在 《虚拟 RDMA 设备驱动实现(一):环境配置与Linux内核模块初探》 中,我们已经完成了内核驱动开发所需的基础设施构建。通过部署一个标准化的虚拟化开发环境,并实践了 out-of-tree 内核模块的完整生命周期,我们确立了在内核空间执行自定义代码的基本能力。

在当今数据以前所未有的速度和规模产生、传输和处理的时代,系统性能的每一个环节都面临着极致的考验。从高性能计算集群到大规模分布式存储,从实时金融交易到低延迟的云服务,对高效数据交换的需求日益迫切。然而,传统的网络通信方式,尽管成熟稳定,其固有的处理开销和多次数据拷贝,在这些追求极致性能的场景下,往...

鹏城实验室与琶洲实验室(黄埔)作为国内顶尖的科研机构,长期致力于人工智能、高性能计算及信息科学领域的前沿探索。鹏城实验室聚焦智能技术与系统创新,琶洲实验室(黄埔)则依托粤港澳大湾区区位优势,深耕网络通信与硬件研发,两者共同推动产学研深度融合。

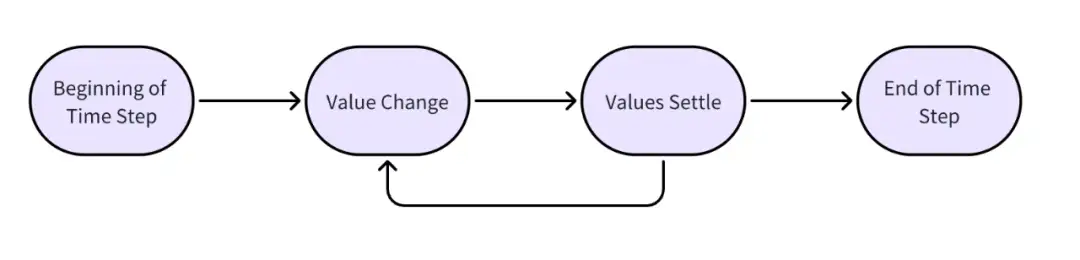

达坦科技即将开源的100G RDMA RTL代码采用cocotb对其功能进行验证。其中,对于DMA引擎的验证工作使用了开源的cocotbext-pcie框架来进行验证。本文将简要介绍cocotbext-pcie的使用方式,以及在使用中遇到的问题。

blue-rdma是一个新的RDMA实现。本文将介绍blue-rdma是如何实现常见的几种RDMA操作的,并且我们会分析blue-rdma设计和InfiniBand的异同点。

达坦科技即将开源的100G RDMA RTL代码采用cocotb对其功能进行验证。因此,本文预先介绍一些cocotb验证框架相关的内容,希望以此抛砖引玉,引起大家对基于cocotb的敏捷验证的相关讨论交流。

当用户向 Deepseak 等大语言模型发起对话时,看似流畅的文字输出背后,模型需要为每个新生成的词语重新计算数十亿参数的关联关系,而这些关联关系往往都和之前的对话上下文有着密切的联系。

达坦科技始终致力于打造高性能AI+Cloud基础设施平台,积极推动AI应用的落地。达坦科技通过软硬件深度融合的方式,提供AI推理引擎和高性能网络,为AI应用提供弹性、便利、经济的基础设施服务,以此满足不同行业客户对AI+Cloud的需求。

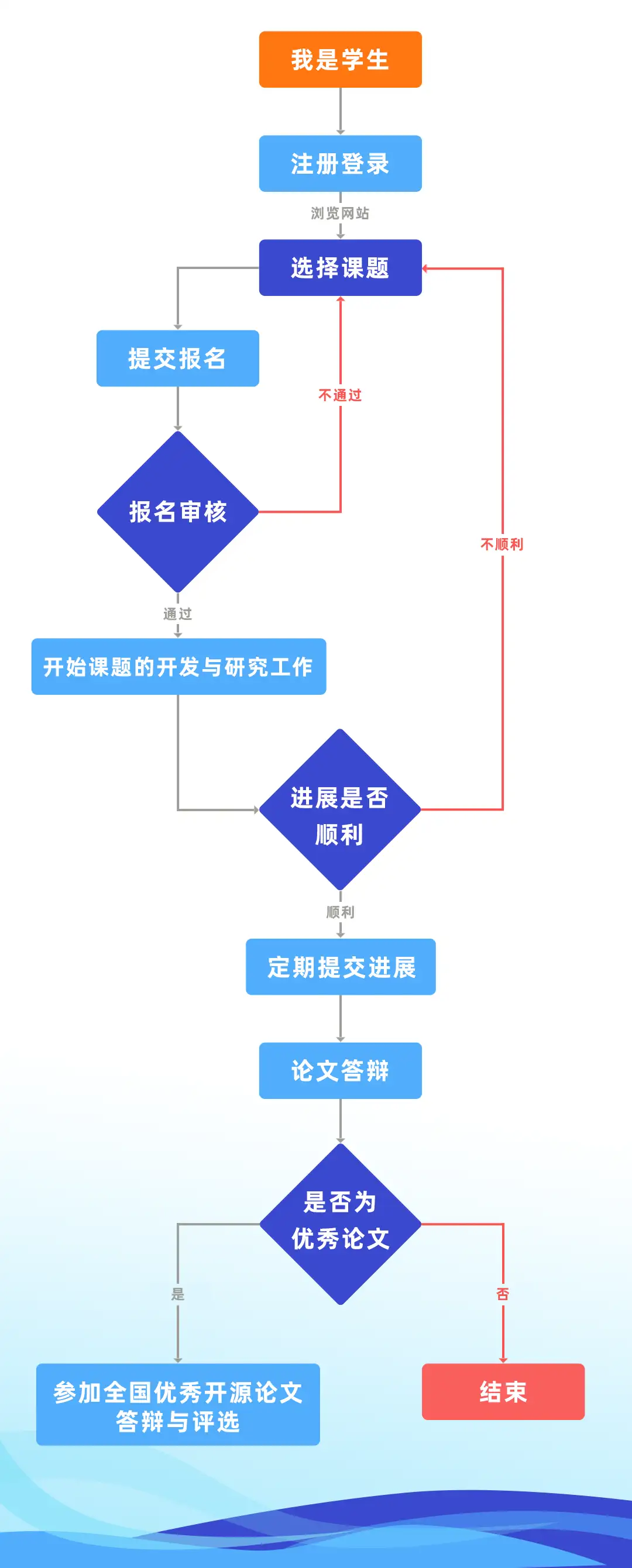

天工开物开源创新实践毕业设计活动(简称:开源毕设)是由天工开物开源基金会发起,并联合开源企业、开源社区、高校教师多方提供支持的一项面向高校学生的开源技术实践活动。开源毕设是一种结合开源社区实践和高等教育实践的创新模式,旨在通过参与真实的开源项目,为高校学生提供一个将理论知识应用于实践、培养创新思...

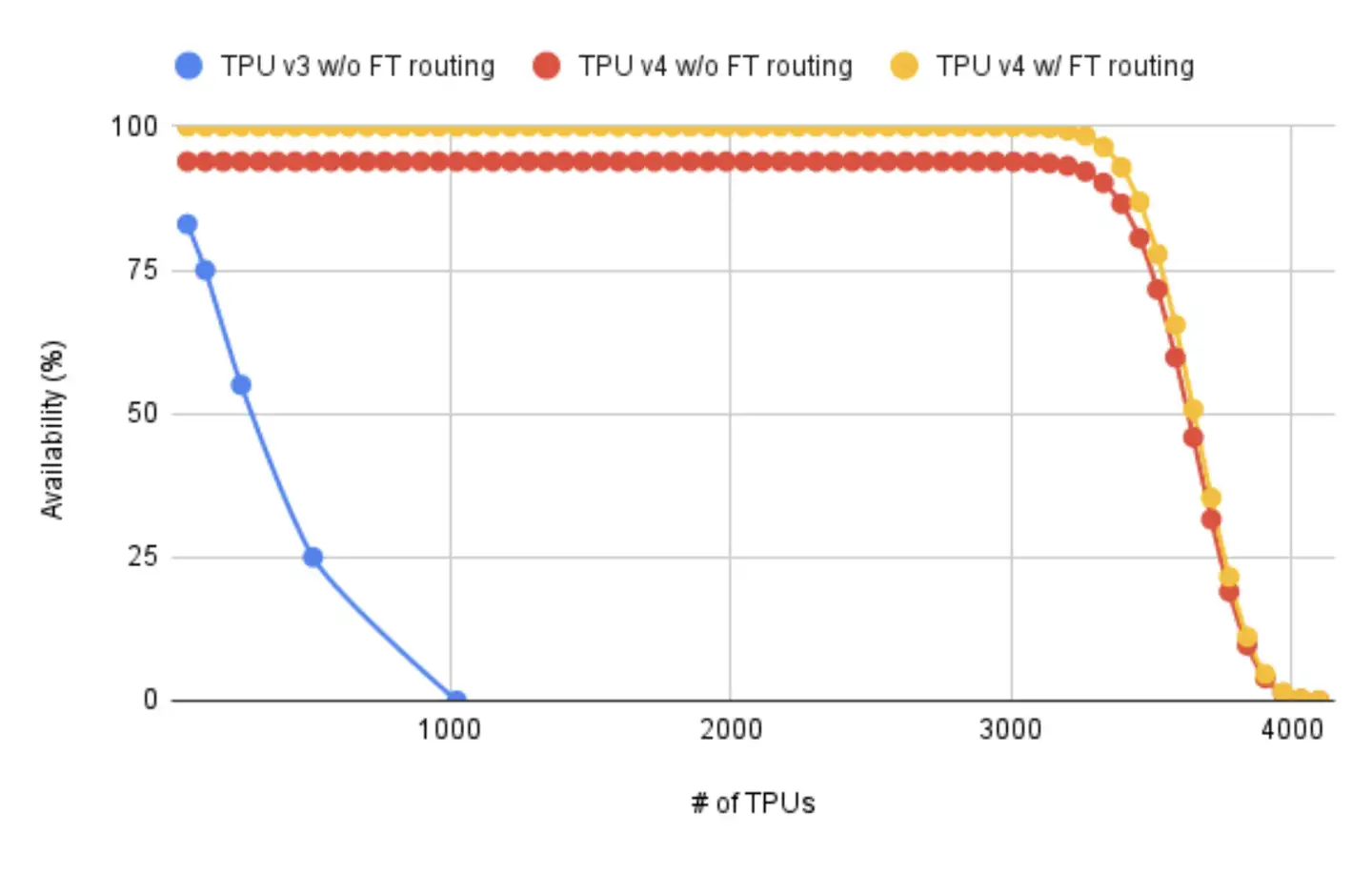

Resiliency at Scale: Managing Google’sTPUv4 Machine Learning Supercomputer。

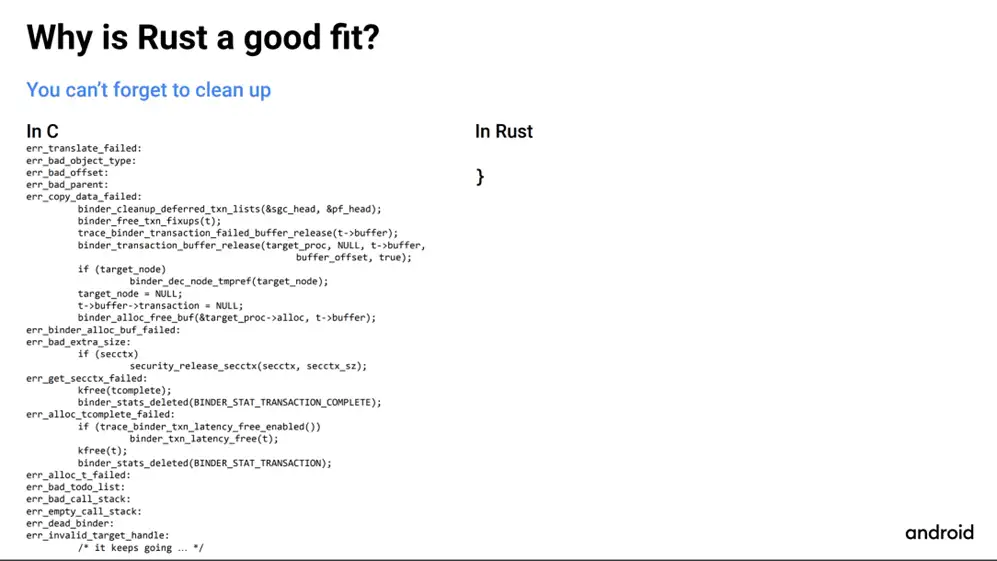

本文提供了一个设计模式的综合概述,涵盖了设计模式的必要性,基本原则以及23种常见模式的概括性描述。结合Rust语言自身的特性,重点阐述了Rust中Builder,Combinator,RAII,Typestate(state machine), Command, Strategy和Visitor七种设计模式的应用。本文前半部分主要在阐述设计模式的思想和具体实例,如果读者已经很...

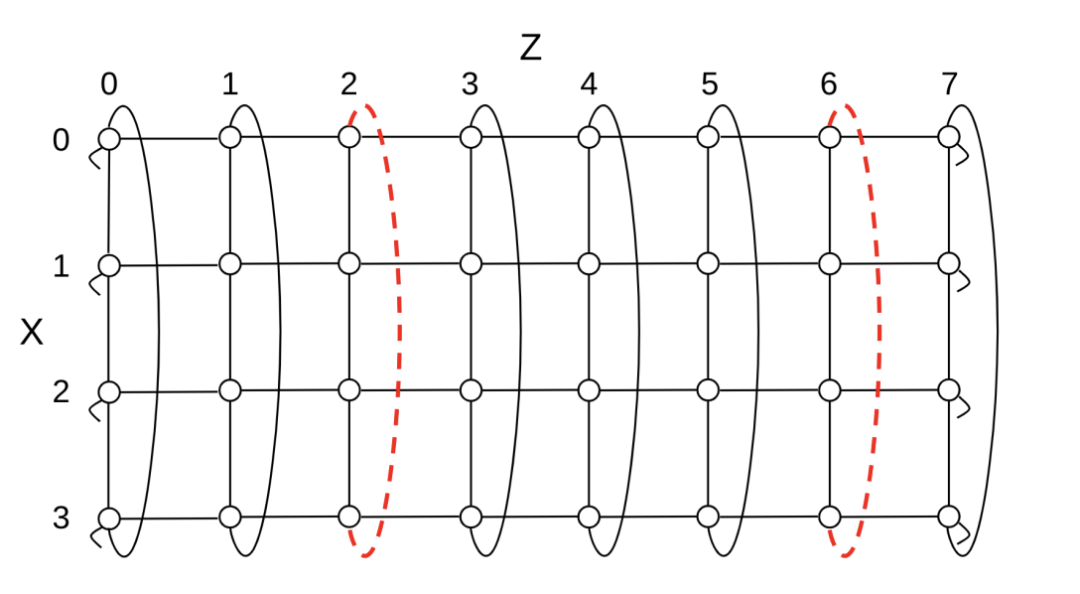

TPUv4(张量处理单元)是谷歌用于机器学习训练的第三代加速器,采用定制的三维环形互连,部署为 4096 节点的超级计算机。在本文中,我们将介绍设计和运行软件基础设施的经验,这些软件基础设施使 TPUv4 超级计算机能够大规模运行,包括自动故障恢复和硬件恢复功能。

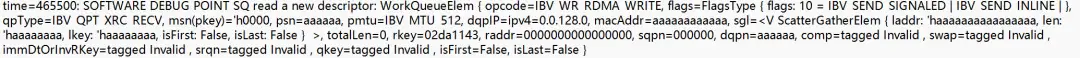

本系列文章将带领读者逐步了解Linux操作系统下的RDMA子系统。本篇文章作为系列的第二篇,将深入内核态驱动程序的代码,主要介绍如下内容:

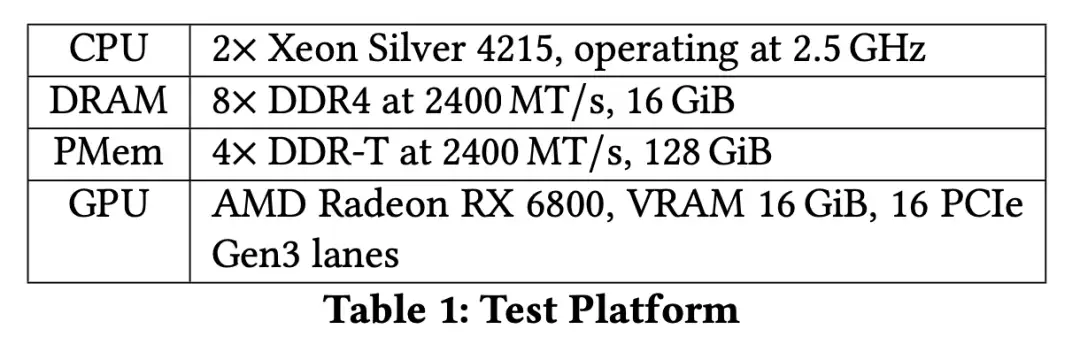

摘要 现代高性能计算和人工智能计算解决方案经常使用 GPU 作为其主要计算能力来源。这就为 GPU 应用程序的存储操作造成了严重的不平衡,因为每一个此类存储操作都必须向 CPU 发出信号并由 CPU 处理。在 GPU4FS 中,我们针对这种不平衡提出了一个彻底的解决方案:将文件系统的实现转移到应用程序中,并在 GPU 上运行完整...

本系列文章将带领读者逐步了解Linux操作系统下的RDMA子系统。本篇文章作为系列的第一篇,将从全局视角介绍如下内容:

在达坦科技实习期间,笔者开发了一个RDMA用户态驱动,用于与达坦科技自研的BlueRDMA进行交互。整个驱动分为内核态和用户态两个部分,内核部分做的仅仅是将必要的内存空间暴露给用户态,例如将bar空间上的csr(control status register)寄存器映射到了用户态,主要的操作由用户态驱动执行。用户态驱动申请了4个巨页,并分...