Arm相关的技术文档资料下载汇总专栏,欢迎收藏关注点赞。

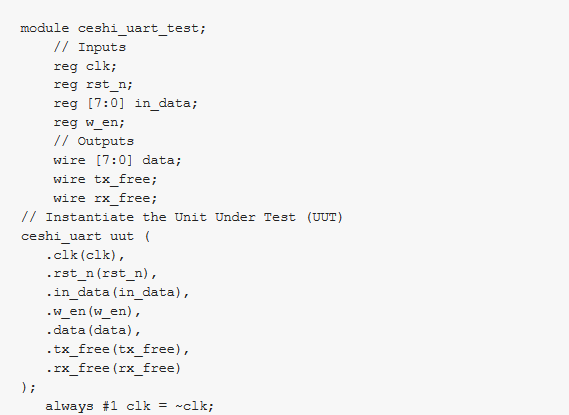

安装vcs工具,需要借助installer工具来进行安装。首先从官网下载vcs的安装包。我这里是vcs的最新版本,2020.12-SP1版本。下载的安装包内容如下所示:将该安装包,拷贝到内网服务器。启动installer。然后填入安装包目录,点击Next。installer工具会解压该安装包,等待一会即可。在下一个界面,输入工具的安装位置。然后点...

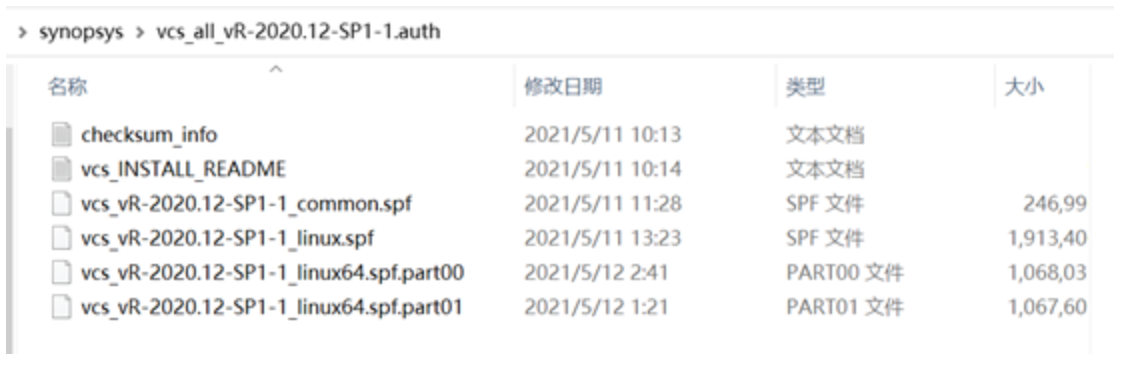

安装verdi工具,需要借助installer工具来进行安装。首先从官网下载verdi的安装包。我这里是verdi的最新版本,2020.12-SP1-1版本。下载的安装包内容如下所示:将该安装包,拷贝到内网服务器。启动installer。然后填入安装包目录,点击Next。installer工具会解压该安装包,等待一会即可。在下一个界面,输入工具的安装位置...

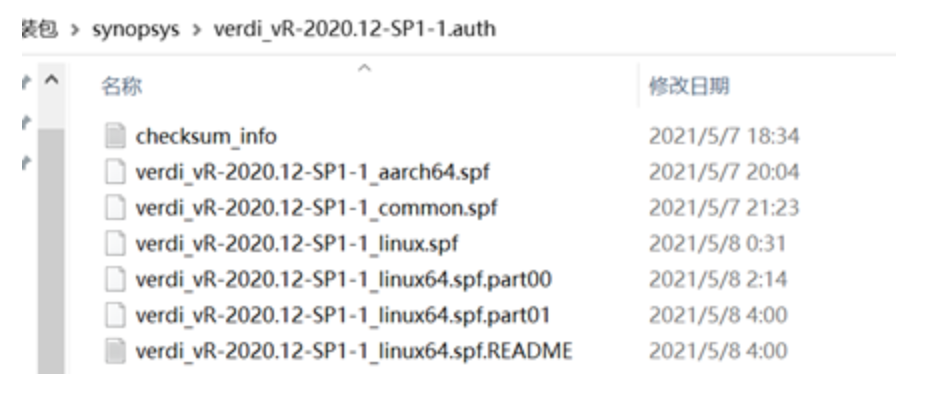

synopsys的工具,是需要官方授权的license认证,才可以运行的。因此需要搭建license服务器,以提供license服务。

synopsys为eda工具安装,提供了一个安装器,名叫installer。所以,首先要先安装installer这个工具,之后才能安装其他的eda工具。

linux中,会有几个常用的工具:◾m4◾autoconf◾automake◾libtool下面介绍下,如何在linux中,源码安装这些工具。一、安装m4-1.4.18m4源代码地址:[链接] 目前,最新版本1.4.18。安装命令 {代码...} 二、安装autoconf-2.69m4源代码地址:[链接] 目前,最新版本2.69。安装命令 {代码...} 三、安装automake-1.16m4源代码地址...

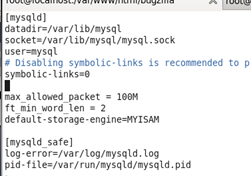

经过自己的摸索,与尝试,成功在centos6.5上,安装bugzilla。并且可以发送邮件。一、安装软件首先,需要安装一些软件 {代码...} 安装mysql,apache,gcc,g++以及一些依赖包。二、创建mysql数据库 {代码...} 如下图所示:执行如下命令: {代码...} 如果第二步修改密码,出现错误,请参考如下博客进行解决。[链接]在mysql...

/etc/sysconfig/HOSTNAME文件中保存了主机名。在/etc目录下,创建profile文件,并加入以下信息。

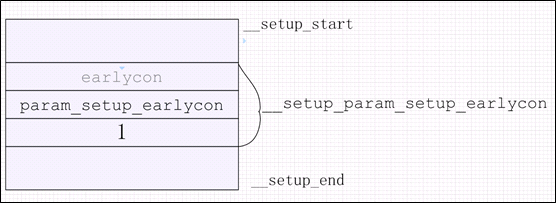

ARM64,在kernel未建立console之前,使用earlycon,实现打印。在bootargs中,要加入如下选项:

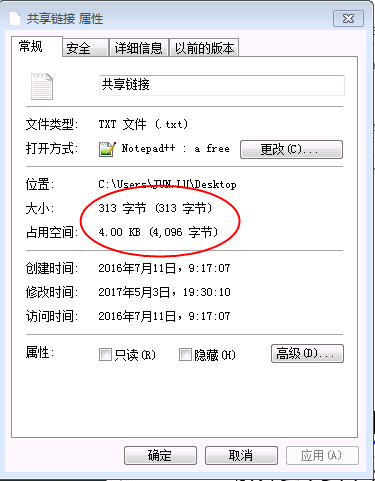

一、文件系统文件系统,是管理文件数据的一堆程序。操作系统,可以通过这些程序,从块设备中,读取或者写入文件。常见的一些文件系统:◾FAT32◾NTFS◾EXT2◾EXT3二、扇区和簇扇区,是块设备(硬盘,nandflash,SD卡)读取和写入的最小单位。一般是512字节。簇是文件系统,管理的最小单位,一般是扇区的整数倍。如4k,16k,3...

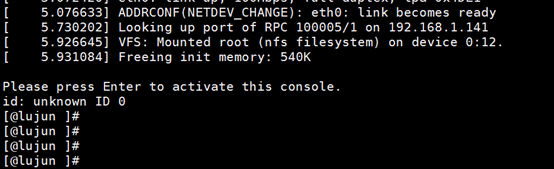

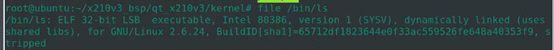

rootfs有两种格式:nfs方式启动的文件夹形式的rootfs和用来烧录的镜像形式的rootfs。

linux在启动之后,会去执行init进程。将自己变为应用进程,而init进程就是linux的进程1,然后再由这个进程,去生成其他的进程。

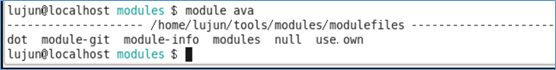

linux中的环境变量管理,让人烦不胜烦。但是有了module这个开源的环境变量管理工具,就让linux中的环境变量管理变得容易。

在sv的assertion中,会用到时钟打拍操作。一般会在assertion代码块中,显示的写上使用的时钟,

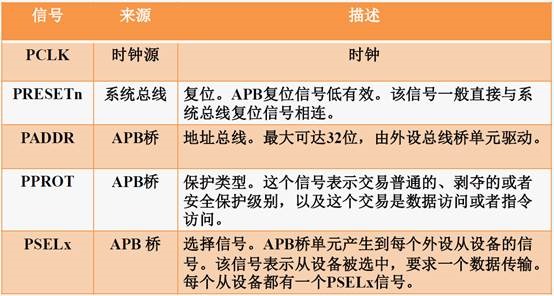

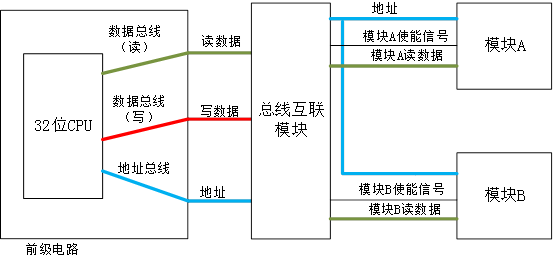

之前,说了片上互联总线,但是光有总线可是不行的,还需要片上总线协议支持才行,因为有了协议,才能对寄存器准确无误的进行操作。

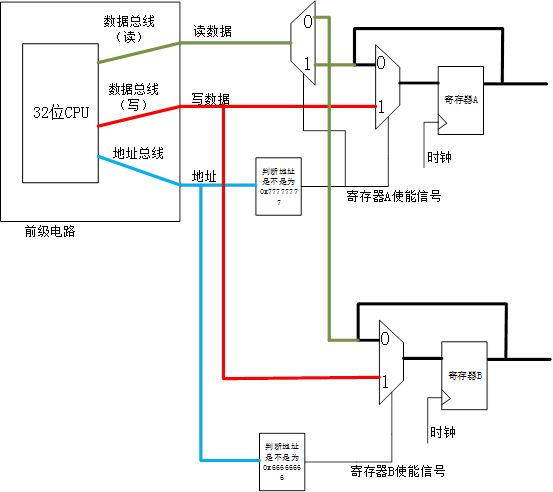

之前说明了软件控制硬件的原理,本质上就是控制寄存器。但是软件也只能控制一个寄存器,那如果要控制多个寄存器了,那又该怎么办呢?这个时候,你就得了解片上总线互联技术了,为什么是片上了,因为这些都是在芯片里面实现的,所以就叫片上了。

很多人肯定很疑惑,在嵌入式开发中,为什么写c代码,就能够控制硬件。这一切是怎么发生的了,下面我就给大家解剖一下,软件是怎么控制硬件的。

之前,说明了,当外部需要增加寄存器的时候,需要更改总线互联模块。在总线互联模块中对于读数据和使能信号是每一个寄存器都有一个连线和总线互联模块相连的,如果寄存器比较少,似乎是没有什么问题。但是如果外接的寄存器有几千,几万个呢?那这一块的电路可真是不敢想象了,基本上做不出来,因为要做出来的话,面积太...

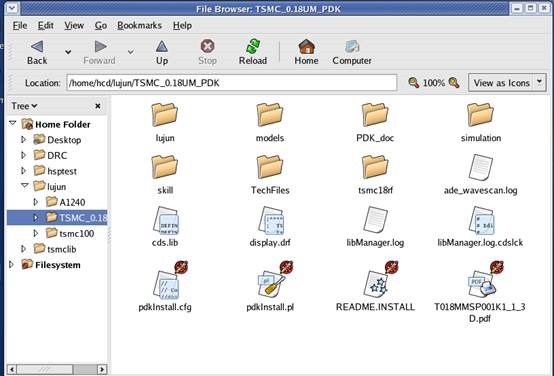

这里用的库是TSMC_0.18UM_PDK,0.18的库。从eetop下载的库。此库只可用于学习用。

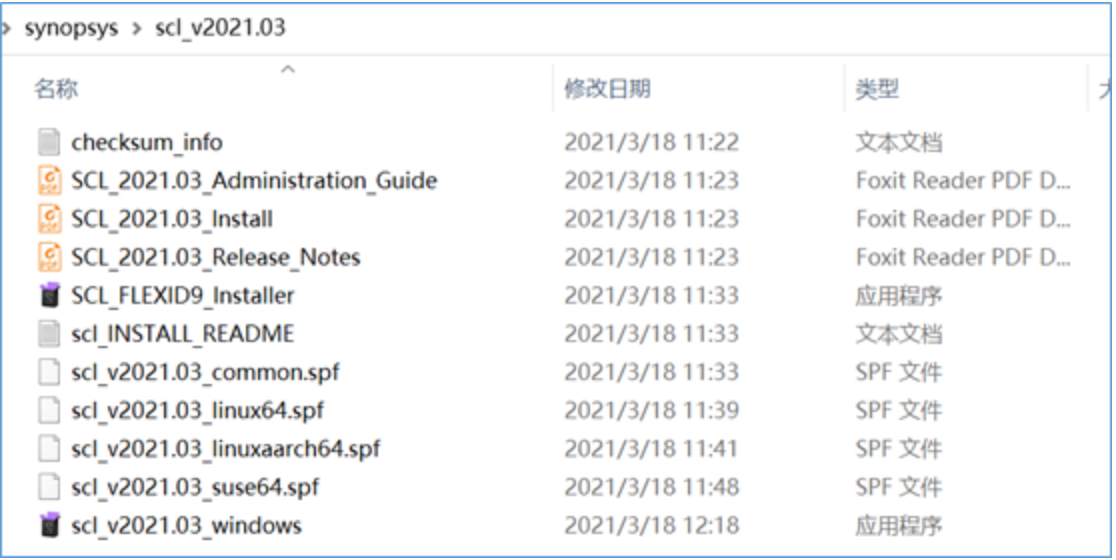

VCS是synopsys的仿真verilog的仿真器。基于linux系统。有命令行模式和图形化模式。图形化模式是用的dve。