乔布斯2007年发布iPhone时,引用图灵奖得主Alan Kay的一句话“真正在乎软件的人,应该打造自己的硬件”。同样道理,想玩好软件无线电,也必须深入SDR(软件无线电)硬件。

拿自由/开源软件/硬件去挣钱?“挣钱嘛,生意,不寒碜”(让子弹飞),但如何“站着,还把钱挣了”?为何用户吐槽裤子都脱了就给我看这?为何会被人怼“既当又立”?为何Google明令禁止员工使用某些协议的开源项目。当公司开源项目遇到外部开发者,为何把工程师关进小黑屋由律师监视进行开发?你以为下载了代码就能为所欲为?...

这一切都是无线通信技术在过去二十多年时间里“暴力扩张”的结果,其背后的基石无疑是芯片制程在过去几十年的高歌猛进。伴随着产业百倍千倍的扩张,有进取心的公司发展为巨头:高通,华为,苹果,太多的昔日的霸主跌入谷底:朗讯,北电,Intel,摩托罗拉,Nokia。

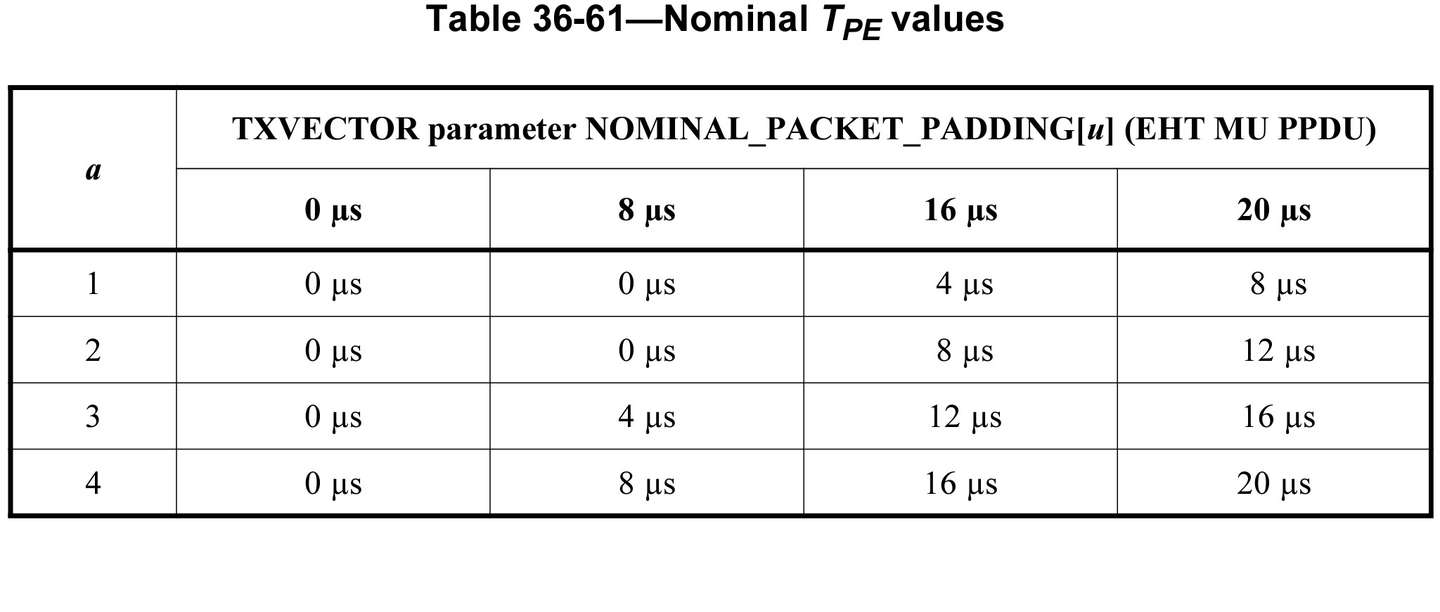

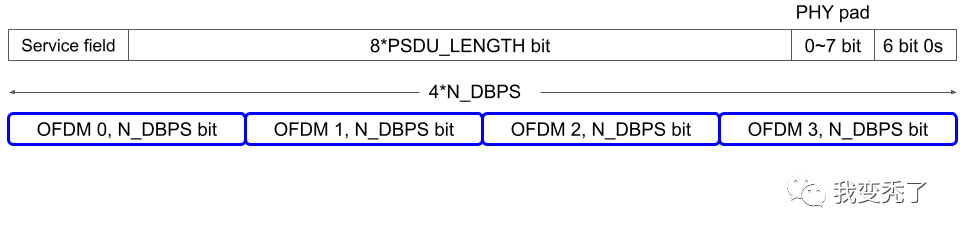

众所周知通信标准主要规定发射端的格式,至于怎么接收和解调是看各厂自己的本事。从WiFi6开始,协议开始从数据填充机制和信号格式进行设计,以允许接收机有合理的解码延迟,保证解码性能和足够时间进行后续操作。

为何自802.11ac开始PHY变成先Pad(0~7bit)最后加6个0 bit,而不是之前的先加6个0 bit再Pad 若干bit?

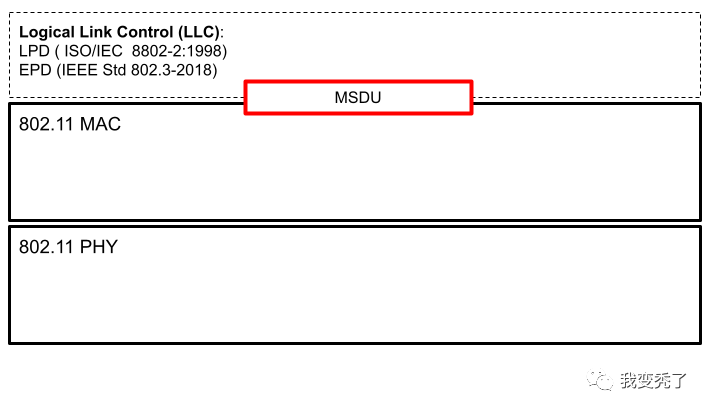

MSDU,A-MSDU,MPDU,A-MPDU,PSDU,PPDU ... 看这些似曾相识似懂非懂的WiFi各层数据包的缩写,是不是很上头?网络数据包就是层层套娃,WiFi也不例外。

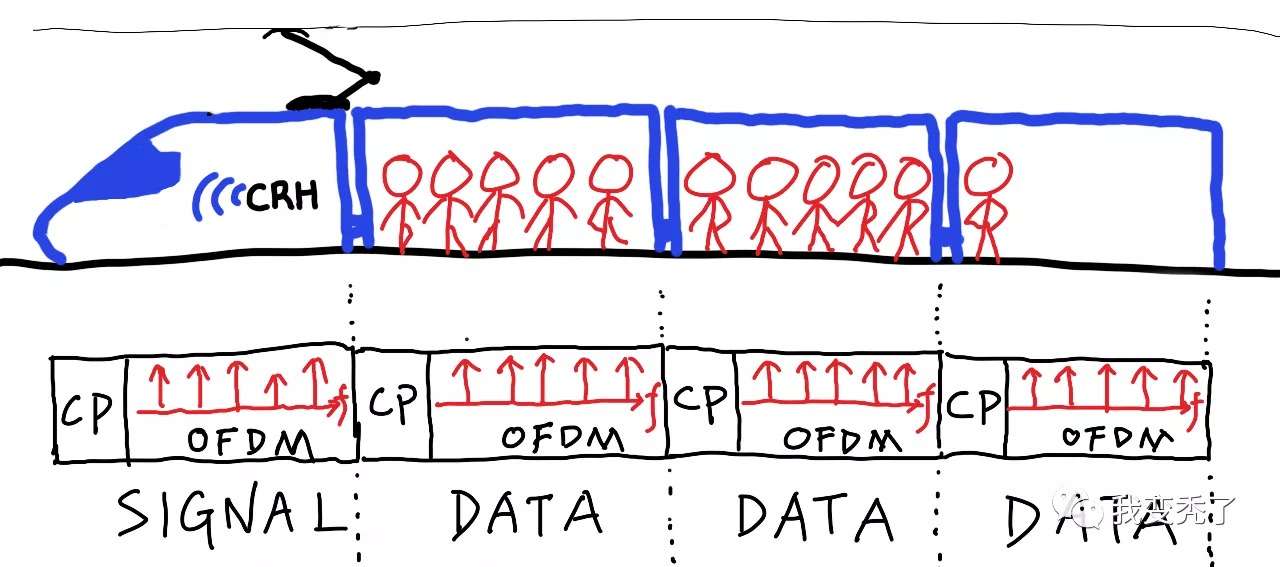

(注:PHY物理层,就是负责通过天线收发一个个bit的最底层,喻为火车。MAC层,媒体访问控制,会把一包包数据交给PHY发送,或者从PHY接收bit,变回一包包数据,可看做闸机,决定往站台放多少乘客)

不开玩笑?标称最高54Mbps的802.11a/g有时只能跑到5Mbps出头?这还是信号完美且没有任何噪声和干扰情况下!

火车车厢可以坐50个乘客,来了101个乘客,该挂几节车厢?挂2节就得扔1个乘客在站台,挂3节那第3节车厢就近乎空跑(仅1个乘客)。

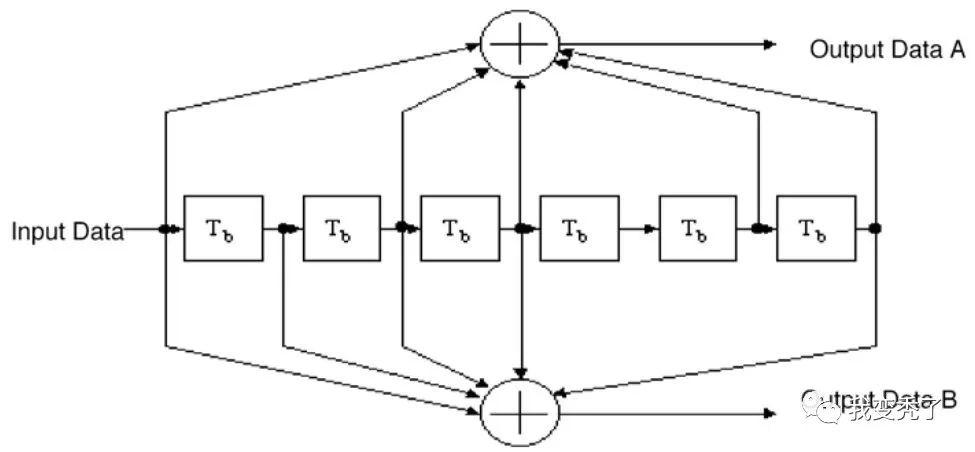

Viterbi解码器是每一个通信人在幼儿园阶段的必修课。卷积编码解码长度可以无限长,工作到宇宙末日。但实际网络数据包长度都是有限的,比如小于1500字节。虽然解码一时爽,一直解码一直爽,但如果不能在正确的时刻停止解码,很可能产生错误bit。对于一个数据包,哪怕只有1bit错误,也会全部丢掉。那么WiFi接收机里的Viter...

[链接]项目网址:[链接]完整腾讯/飞书会议录像:[链接]WiFi基本概念openwifi总体架构以及组成模块介绍openwifi的诞生、定位以及横向对比openwifi科研应用:无线感知、无线通信、无线安全openwifi开发进展和路线图openwifi开源License选择与可持续发展回应质疑

拿自由/开源软件/硬件去挣钱?“挣钱嘛,生意,不寒碜”(让子弹飞),但如何“站着,还把钱挣了”?为何用户吐槽裤子都脱了就给我看这?为何会被人怼“既当又立”?为何Google明令禁止员工使用某些协议的开源项目。当公司开源项目遇到外部开发者,为何把工程师关进小黑屋由律师监视进行开发?你以为下载了代码就能为所欲为?...

openwifi,开源WiFi芯片项目([链接]ppt链接[链接]

“当时的打印机都带有程序的源代码,因此在打印机出现故障时,Richard可以直接修改源代码以解决各种故障。但后来实验室购入了一台新的施乐打印机,但不再附有源代码。Richard无法像以前通过修改代码来解决打印机故障,并向实验室的与施乐公司有往来的教授寻求帮助。但该名教授拒绝了Richard,因为已经与施乐公司签署了保...

划重点:GNURadio加入寻找外星人的SETI组织,并且组织架构从“仁慈独裁者”转变为“委员会”。PySDR -- 当Python遇见SDR,一个极好的SDR入门实践课程:[链接]。追星星(鹊桥,嫦娥,天问)的人Daniel。仅靠“开源”这一个特点,芯片项目能否成功?

FOSDEM21 如期线上举行。openwifi像往常一样在软件无线电开发者房间(free software radio dev room)给出报告!

FOSDEM = Free and Open source Software Developers' European Meeting

RMS构建了自由软件的基石,操作系统内核,gcc,emacs。那么今天就来介绍这个构建了FPGA的gcc — 自由硬件的基石的程序员。他就是Clifford Wolf。当然现在应该说她就是Claire Xen。生于1980年的奥地利程序员。1996年就开始玩UNIX/Linux。

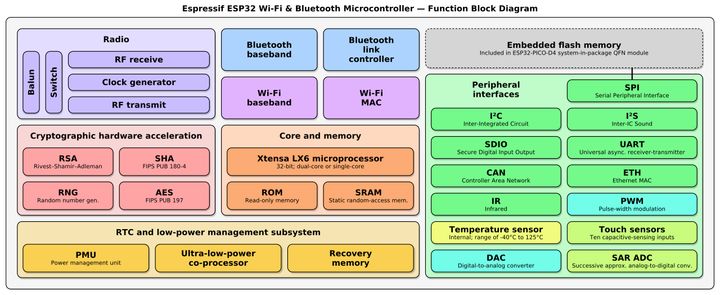

可编程VS可配置:一个东西可编程意味着你可以在上面跑你写的程序,一个东西可配置意味着你只是用你写的外部程序(比如驱动)去配置它和实时的控制它,比如配置它的成百上千个寄存器,进而实时控制它的行为、模式等。例如单片机开发中有上位机(PC)下位机(单片机)的概念。这个下位机(也就是单片机)是可编程的,当你...

最近调试openwifi(开源WiFi芯片),觉得FPGA里的low MAC状态机错综复杂,实在头大(自食其果,自作自受)。于是萌生了“重构”的念头。我深知这是一个危险的想法,但也是一个充满诱惑的想法,想想就刺激。但不妨碍先想想,想想而不动手,这就是传说中的yy吧。