逻辑综合是一种通过EDA工具将设计的RTL模型自动转换为门网表的过程,总的来说,这个过程在研发流程中已经非常非常成熟了。

现代SOC设计可能涉及连接数十个IP,在顶层通过MUX进行总线选择,最终连接到芯片外部的引脚,这些IP的连接具有不同的延迟。

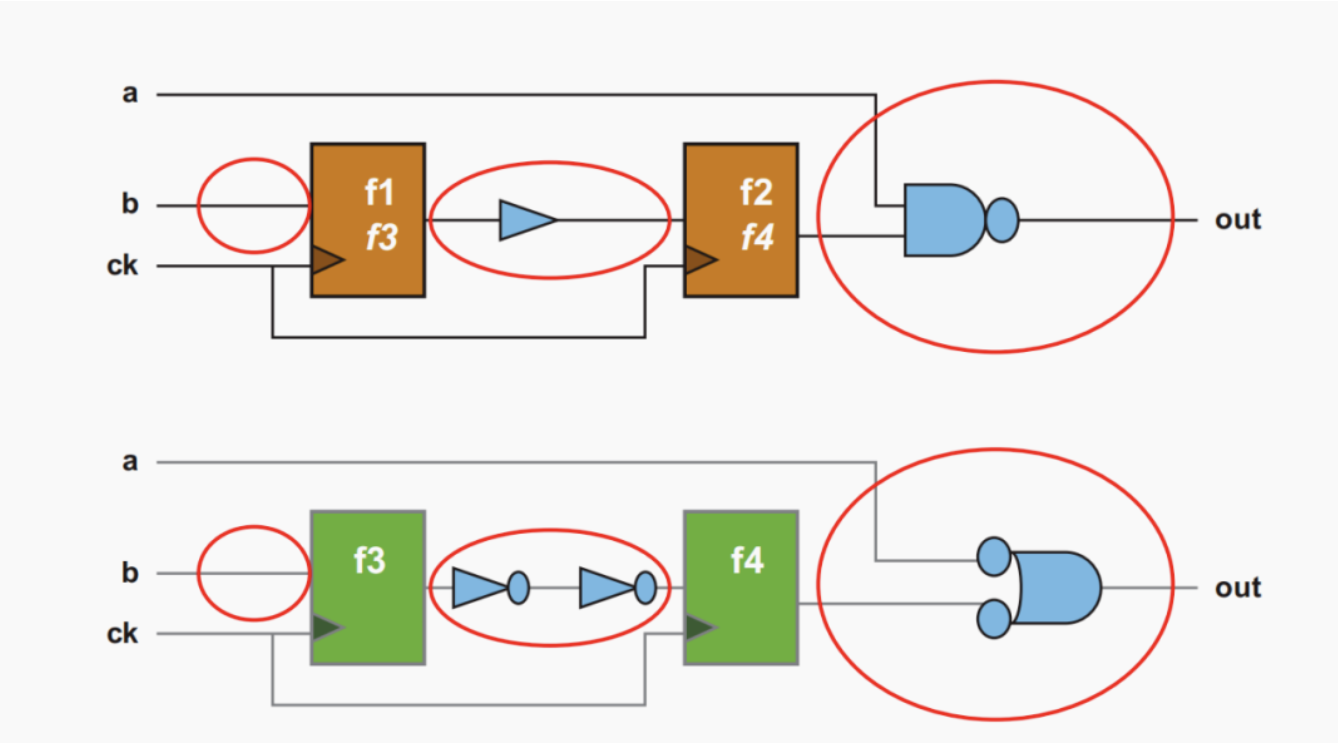

1. 处理FPV中复杂度问题的两个简单办法作为FPV验证计划的一部分,我们应该尽考虑采取措施来减少FPV执行的DUT规模的 复杂度,当然如果设计的复杂度不高,也不是必须要降低复杂度的。所以,对于FPV,最重要的就是在早期评估复杂度问题!以及工具无法run完时的应对策略。我们在这里讨论在FPV验证规划阶段可以考虑的一些基本...

首先,如果你正在考虑使用FPV进行验证,你需要确保你的DUT确实适合使用FPV,例如控制逻辑或数据透传。

• 在任何给定时间,恰好一个方向必须有非红灯。(从那个方向来的汽车有直行和左转的通行权。)• 如果一辆车正在等待,它最终会获得绿灯。• 从救护车发出的“紧急”信号会迫使特定方向的交通灯在两个周期内变绿。

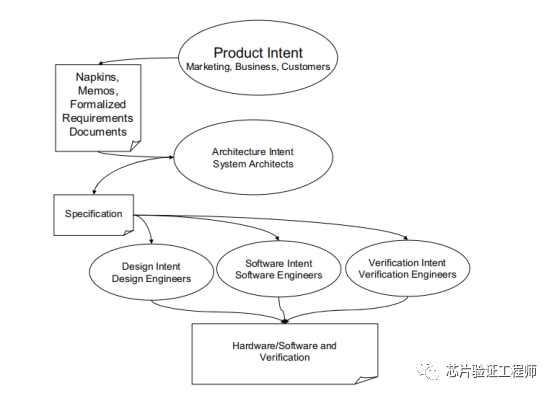

在开发流程中,设计和验证人员关注的点肯定是不一样的,尤其在spec的理解上,验证人员往往需要有自己独立的理解。在拿到spec时,作为验证人员,应该如何提炼其中的功能从而转化为对应的reference model以实现和详细设计的交叉验证。

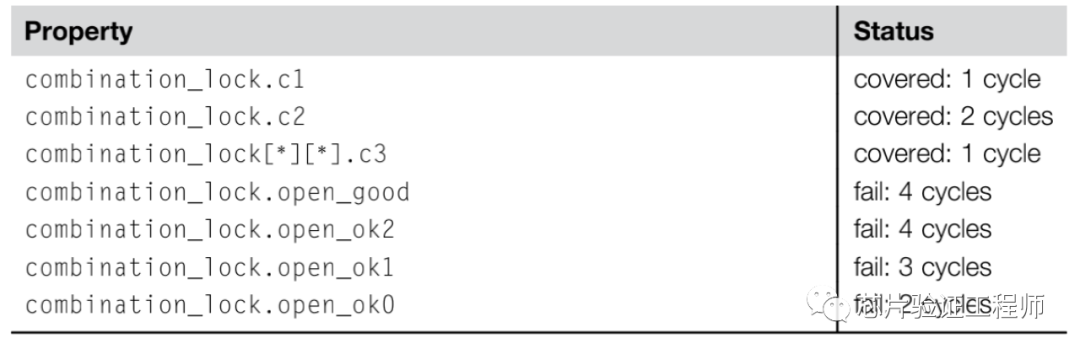

有些输入表示设计的某些特性,暂时不关心,例如我们之前的密码锁设计中的override信号。在验证环境中,我们主要验证输入数据组合对锁的是否打开影响,所以将override信号约束为0

基于前文,我们对于FPV工具已经有了基本的了解了,下面我们进一步分析FPV与EDA仿真(simulation)有何不同。

断言是整个FPV流程的焦点,即我们想要证明的最终目标。如果不考虑算力,理想情况下我们能够证明或者证伪所有的断言。

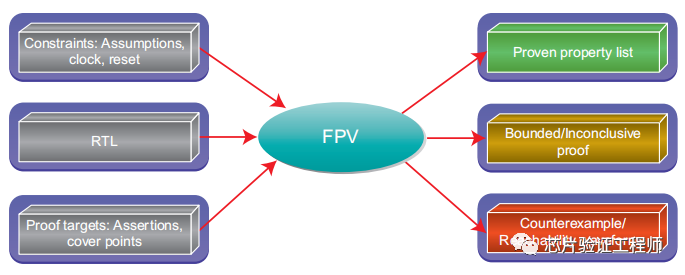

一、什么是FPV?FPV是一种用来证明使用SVA或类似的语言描述的RTL属性的方法。 上图说明了一个FPV工具执行的框图。FPV的输入:1、RTL模型2、要证明的一组属性:assertions 和cover3、一组约束条件:assumptions以及时钟、复位FPV的输出1、已证明的属性列表(proven assertions)2、无法覆盖的场景(unreachable cover poi...

作者:知乎匿名用户 原文链接:芯片验证工程师微信公众号: 推荐阅读有关验证的问题System Verilog面试题(四)更多IC设计技术干货请关注IC设计技术专栏

交付给验证工程师的规格对设计最原始需求的翻译,这两者并不是等同的。保证满足设计的原始需求才是验证工程的终点。

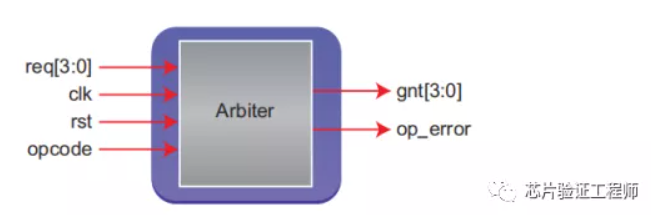

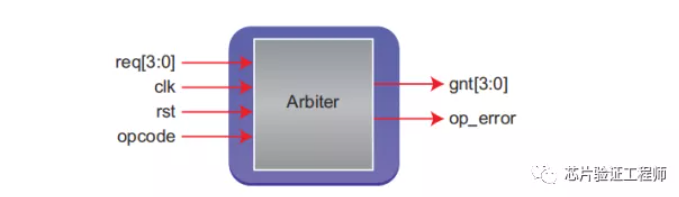

本文将使用一个简单的Arbiter(仲裁)设计示例展示SVA断言的概念和用法。 这个仲裁器有四个请求口req ,gnt信号指示哪个请求被授权。还有一个输入opcode允许使用命令来指定某些行为,例如强制一个特定的请求口获得优先级或者在一段时间内阻挡所有访问。还有一个输出op_error ,用来告警发送了错误的opcode 。

01 如何在子类中调用父类的task?可以在子类中使用super关键字引用父类中的成员,尤其是该成员已经被子类覆盖。 {代码...} 仿真结果: {代码...} 02 rand 和 randc有什么区别?rand 是标准的随机变量。当对随机没有其他约束时,这些变量会均匀地分布。randc是一种周期循环,它随机迭代有效范围内的所有值。每次迭代不重...

queue(队列)是一个可变大小的、有序的元素集合,类似于自动增长和收缩的一维数组。队列可用于建模先进先出缓冲或者先进后出缓冲。

本文将使用一个简单的Arbiter(仲裁)设计示例展示SVA断言的概念和用法。 这个仲裁器有四个请求口req ,gnt信号指示哪个请求被授权。还有一个输入opcode允许使用命令来指定某些行为,例如强制一个特定的请求口获得优先级或者在一段时间内阻挡所有访问。还有一个输出op_error ,用来告警发送了错误的opcode 。

object是类(class)的实例。Class 是对象的定义。当创建一个类时,它不占用任何内存,但是当类的实例(对象)被创建时,它们会占用内存空间。

Callback (回调)是指更改验证组件(driver、sequencer或者monitor)的行为而不更改组件代码的机制。它可以用于功能覆盖率建模,错误注入等功能。

Formal verification的优势在哪里?首先我们应该都有一个共识:在数学上穷尽分析所有可能的RTL空间是最理想的验证结果,这也是传统的仿真很难做到的事情。FPV方法的优点包括:做正确的验证这句话可能比较哲学哈。以一个工程师的角度,你是否问了自己很多次:我们应该如何正在验证我们的设计? 理想的方法是从数学上证明...

竞争冒险这个含义其实广泛存在各个领域,本质上是指当两个或多个进程同时访问一个相同对象的场景。 组合逻辑环 {代码...} 在一般的数字设计中不用使用组合逻辑环,需要在其中进行插拍(异步设计除外)。仿真竞争冒险:在两个或两个以上变量之间没有电路逻辑环,但有一个仿真反馈路径。 {代码...} Verilog语句块有很多是...