在 FPGA 学习过程中,你是否也曾遇到过这些问题:教材晦涩难懂,电路图和代码脱节?找不到既系统又实战的开源学习资料?工具链配置复杂,不知从何下手?如果你点头了,那么今天推荐的开源项目 Project F,可能就是你期待已久的答案。什么是 Project F?Project F 是一个完全开源的、面向学习者的 FPGA 教程项目,由英国...

在过去的十年中,可编程逻辑器件(PLD)市场不断增长,对PLD的需求不断增加。具有可编程特性且可编程的芯片称为PLD。PLD也称为现场可编程器件(FPD)。FPD用于实现数字逻辑,用户可以配置集成电路以实现不同的设计。这种集成电路的编程是通过使用EDA工具进行特殊编程来完成的。

在创建 RTL 示例时,经常使用 VHDL 2008 附带的 VHDL 包。它提供了出色的功能,可以高效地处理定点数,当然,它们也是可综合的。该包的一些优点包括:

这是某乎上的一个问题,我觉得还不错,今天就系统性的总结一下1、fpga4fun[链接]你能在这个网站上找到什么?您可以找到信息页面,以及使用 FPGA 板构建的 FPGA 项目。注重点:项目。FPGA 项目使用一种称为 Verilog 的语言,您需要学习它才能理解项目。但是通过此处显示的示例以及其他可用的在线资源,这并不太难。上面就...

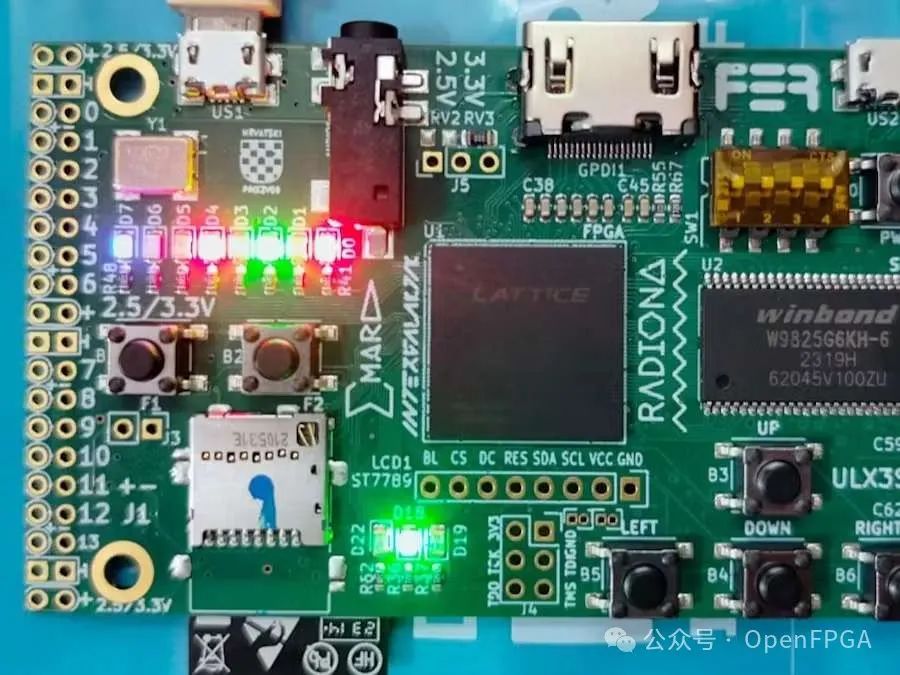

之前的文章《国产 FPGA 搭建的复古游戏平台》说到了目前 Mister 遇到的问题,所以目前有很多 Mister 的继承项目,今天介绍一个目标及规划都远超原版的项目-MisteX。

目前 FPGA 的开发和官方的 EDA 工具是高度绑定的,用哪家的芯片只能用其配套的 EDA 工具进行开发(综合可选工具,布局布线没有可选的工具),那么有没有其他的开发方式呢?今天就介绍一个使用开源工具链来开发 FPGA 的方式。

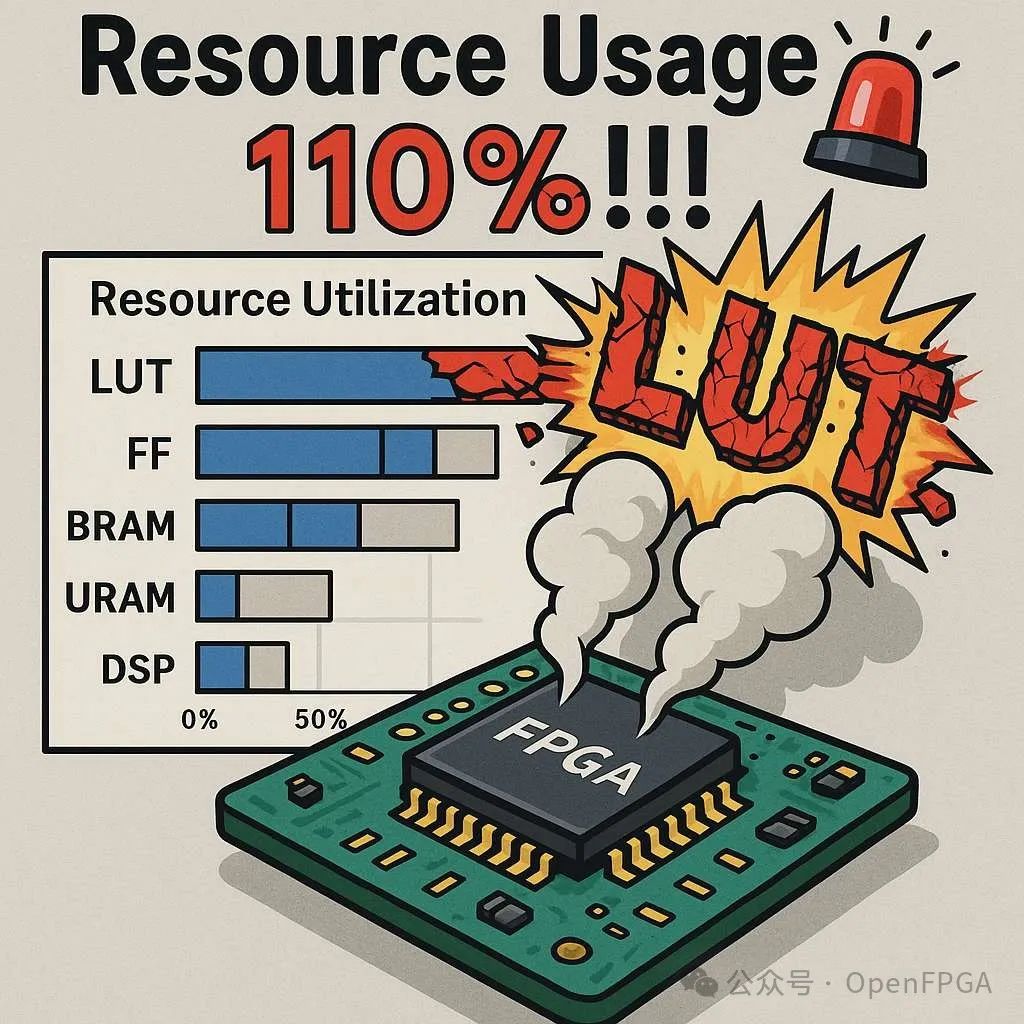

做 FPGA 项目,最怕啥?资源爆表!Timing 炸裂!布线卡死!今天我给大家总结 10 个实战级优化技巧,每条都有具体案例,助你从根源上搞定资源问题!技巧一:减少不必要的总线宽度问题实例:原代码: {代码...} 实际上每次只用前 32 位。优化做法,改成需要的实际位宽:改成: {代码...} 👉 LUT 减少了 90%,走线压力降低!...

本文将逐步介绍如何使用 Vitis Model Composer 生成 FPGA IP 核,从建模到部署。

今年开年 AI+机器人引爆科技圈,都说 FPGA 是“万能芯”,在 AI 方向上已经挣扎了几年,仍旧不能“破圈”,那么在机器人方向呢?

大家在一些二手网站上经常能看到一些没有配套资料(原理图等)的板子,而这些板子相对来说比较便宜,如果量大则可以用来做开发板,那么首先需要解决的就是”逆向“出原理图用来后续例程的开发。

今天给大家带来 DeepSeek 推荐的开源项目,因为有些项目已经失效了,所以会替代为一些相近项目。

亚稳态是触发器或锁存器输出端发生的不可预测行为,其输出在特定时间段内呈现 0 到 1 之间的非特定值。

本文使用 DDS 生成三个信号,并在 Vivado 中实现低通滤波器。低通滤波器将滤除相关信号。介绍用 DDS 生成三个信号,并在 Vivado 中实现低通滤波器。低通滤波器将滤除较快的信号。本文分为几个主要部分:信号生成:展示如何使用 DDS(直接数字合成)IP 生成测试信号 - 10 MHz 信号和 500 kHz 信号,然后将它们组合起来创...

在 AI 大火之后,AI 代码一直是讨论的热题,之前比较火的 cursor 就是基于此出现的,但是国内访问受限,而且价格昂贵,我们今天就做个平替版。

随着人工智能技术的飞速发展,以 DeepSeek 为代表的大语言模型(LLM)正在逐步渗透到传统硬件开发领域。在 FPGA(现场可编程门阵列)和 IC(集成电路)开发这一技术密集型行业中,DeepSeek 凭借其强大的自然语言处理、代码生成和逻辑推理能力,展现出颠覆传统开发流程的潜力。本文将深入探讨 DeepSeek 在这一领域的应用...

VGG(Visual Geometry Group)是牛津大学的 Karen Simonyan 和 Andrew Zisserman 在挑战 2014 年的 ILSVRC 时提出的系列模型。基于模型研究和比赛结果,两人发表了论文《Very Deep Convolutional Networks For Large-Scale Image Recognition》。

LeNet 主要用来进行手写字符的识别与分类,其确立了 CNN 的结构,现在神经网络中的许多内容在 LeNet 的网络结构中都能看到:

为高频交易(High Frequency Trading,HFT)公司开发硬件一直是 FPGA 工程师最热门的职位之一。由于该行业提供的高薪,甚至可以被称为该领域许多人的“梦想职业”。本文根据自己和其他人的亲身经历,写了一篇关于测试职位是什么样子以及如何准备面试的文章。

在我上学的时候,STM32+FPGA 的架构是论文或者研究的一个热点。直到 Xilinx 的 ZYNQ 和 Altera 的 Cyclone V 出现大家才把研究的重点放到 ZYNQ 上,但是 ZYNQ 等架构成本较高及 PS 或者 HPS 端通常需要 DDR,板子较大,同样的功耗也不低。从这几方面来说,ZYNQ 等架构不是为了替代 STM32+FPGA 的架构,所以这种架构目前...

从项目开始规划架构,并尽可能利用 IP 核来减少所需的开发量(并不特指官方 IP)。在层次结构方面,有几点注意事项: