工具简介

在本专栏之前发布的一篇知乎文章中,已经对SoC设计实验需要用到的相关软件工具进行了简单的介绍,文章链接如下:

在走近FPGA系列文章中主要用到的工具有Vivado和Modelsim,其中Vivado软件在上一篇文章中已经做过详细介绍,文章链接如下:

本篇文章将主要介绍Modelsim的安装和使用。

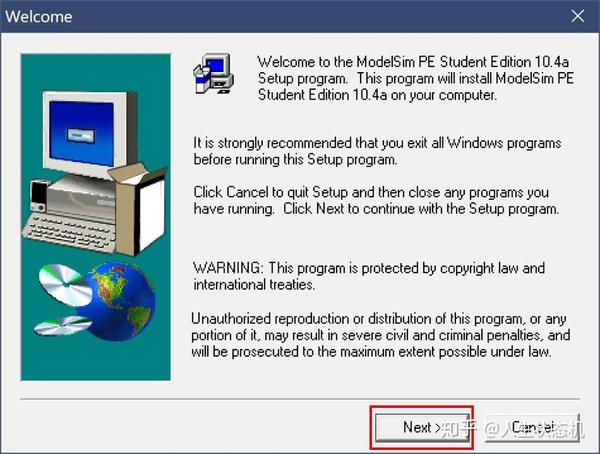

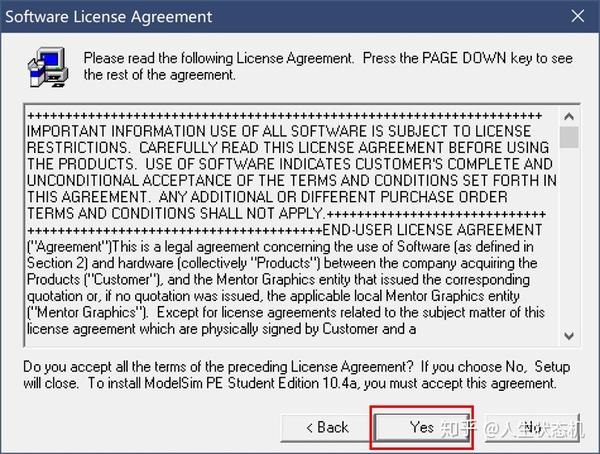

安装流程

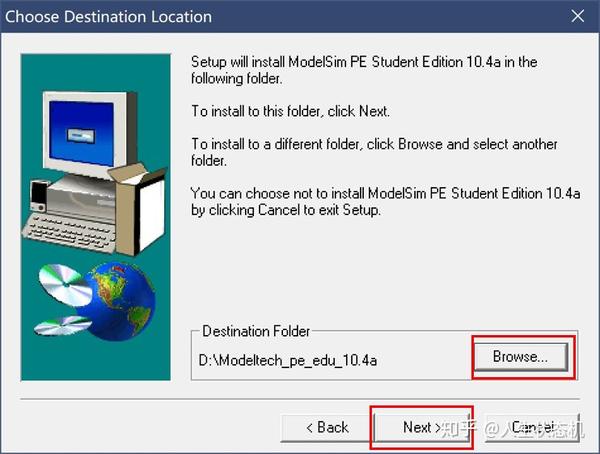

在官网(https://www.mentor.com/company/higher\_ed/modelsim-student-edition)可以下载到免费版(学生版),只需填写少量信息即可。在下载完成后,打开安装包,开始安装过程。前两个界面直接点击Next和Yes即可。接下来选择安装目录,注意不要出现中文。

选择安装目录

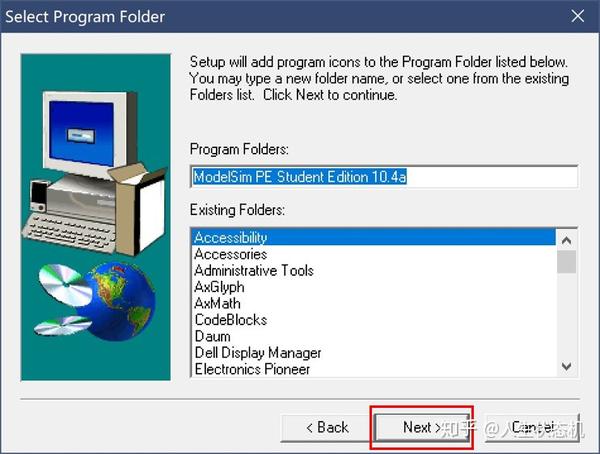

选择图标文件夹,保持默认点击Next即可。

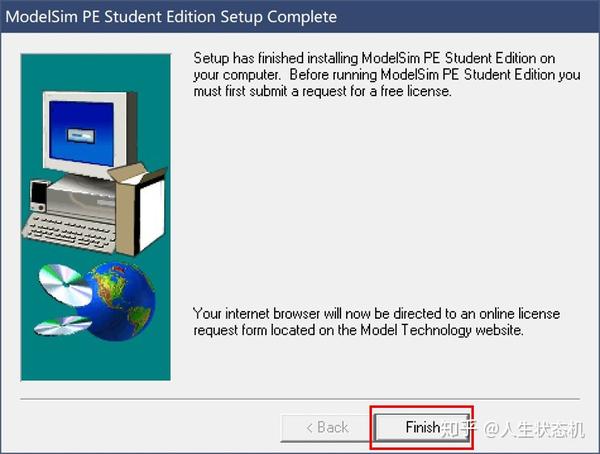

最后点击Finish即可。

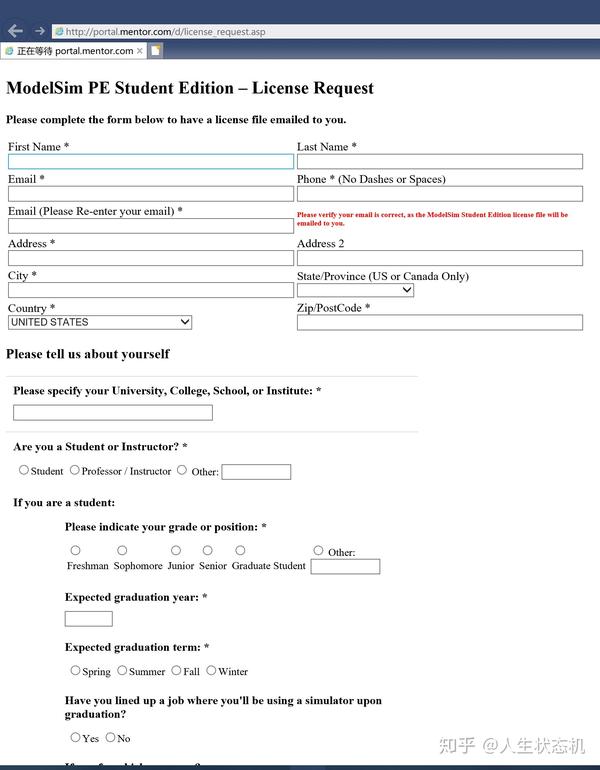

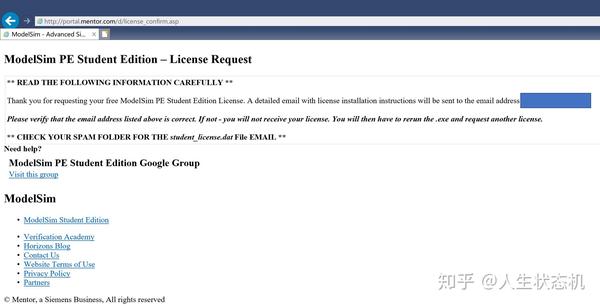

在等待一段时间的安装过程后,会自动弹出申请学生License的网站界面,填写完带*标记的信息后,便会弹出License申请成功的通知。申请成功后License将会很快发送到填写的邮箱中。

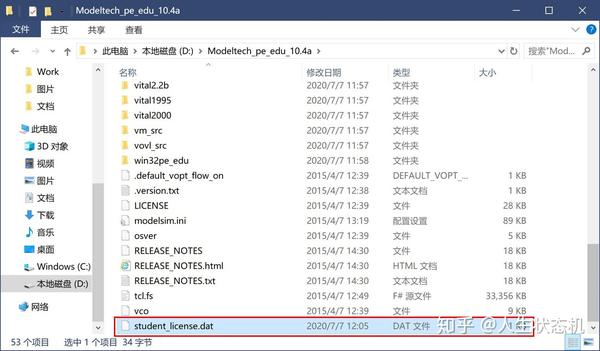

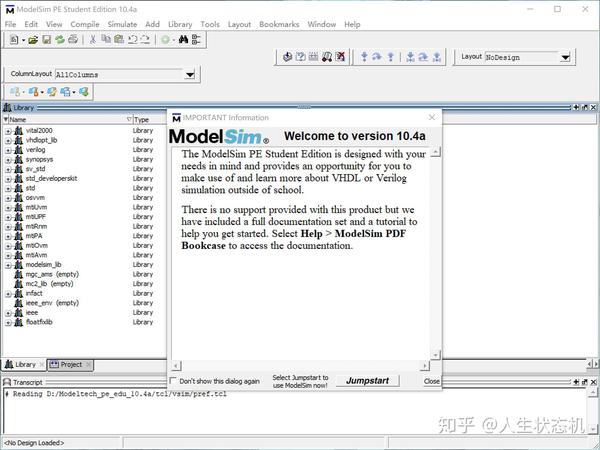

License下载完成之后,将其复制到Modelsim软件的安装目录下,即可正常使用Modelsim软件进行仿真,进入Modelsim时正常的界面如下:

将license移入安装目录

功能仿真

功能仿真(前仿)主要特点是只仿真逻辑功能是否正确,而时序仿真(后仿)主要关心在考虑电路中的时序信息后功能是否正确。关于前仿和后仿更多的区别与联系可以看这个问题下的回答:

本文将简要介绍做功能仿真和时序仿真的步骤。

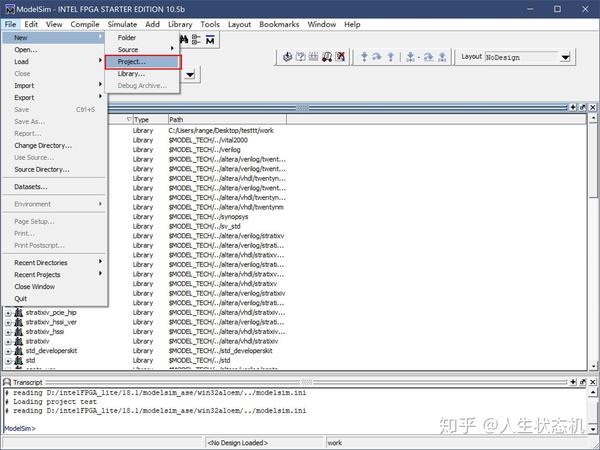

首先打开Modelsim软件,点击左上角的File->New->Project新建一个工程,如图所示。

新建工程

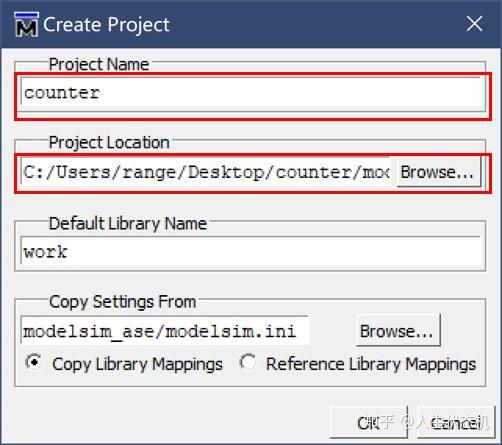

接着在下图所示的界面中输入工程名和工程存放的路径(注意不要有中文)。

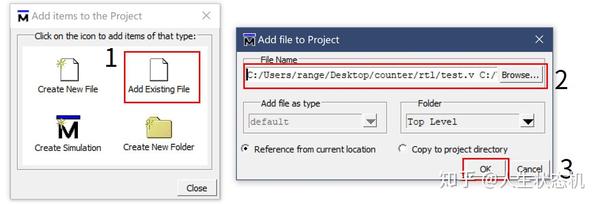

添加文件到工程时选择“Add Existing File”(已经事先编写好模块~一个简单的计数器,为了对比按[N:0]定义A信号,[0:N]定义A\_comp信号,每次时钟上升沿+1),点击browse选择文件(可以一次选择多个文件),然后点击OK。

//counter.v

module counter(

input clk,

input rstn,

output reg [3:0] A

);

reg [0 : 3] A_comp;

wire [3 : 0] A_next = A + 1'b1;

wire [0 : 3] A_comp_next = A_comp + 1'b1;

always @ (posedge clk or negedge rstn) begin

if (~rstn) begin

{A, A_comp} <= 8'b0;

end

else begin

A <= A_next;

A_comp <= A_comp_next;

end

end

endmodule

//counter_tb.v

`timescale 1ns/1ps

module counter_tb();

reg clk, rstn;

wire [3:0] A;

counter uut(

.clk (clk)

,.rstn (rstn)

,.A (A)

);

initial begin

clk <= 1'b0;

rstn <= 1'b0;

#21

rstn <= 1'b1;

end

always begin

#5 clk <= ~clk;

end

endmodule

添加已有设计文件

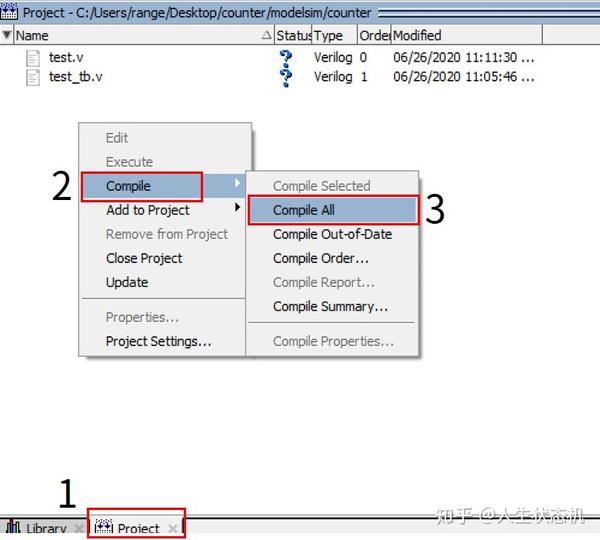

之后便可以在Project一栏看到刚才添加的文件,右键空白区域,选择Compile一栏下的Compile All,将刚才添加的文件全部编译。编译完成后每个文件右边对应的Status会变成绿色的对勾,如果出现错误,则需要根据下方消息框的报错信息进行代码修改再编译。

编译模块

编译完成后,在Library一栏下找到work,可以看到编译好的两个模块test和test\_tb,双击test\_tb开始仿真。

开始仿真

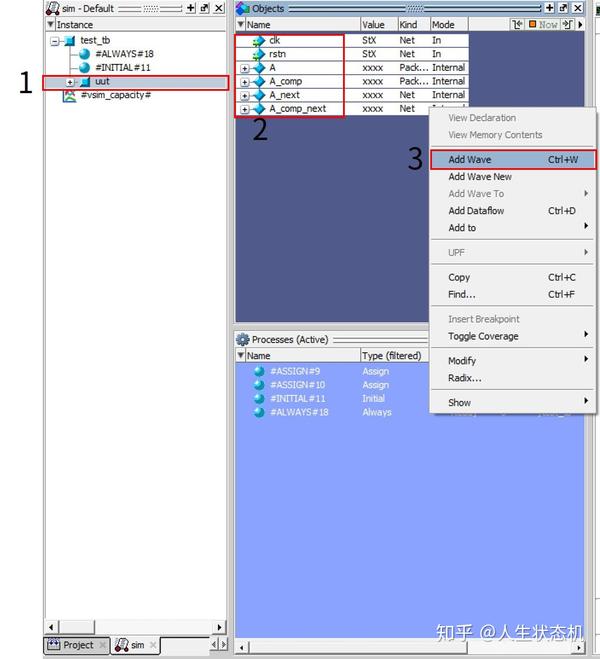

进入仿真界面后,首先在左侧sim栏中选中例化的模块,在右侧的Objects栏中便会出现信号列表,将需要添加到波形中进行观察的信号选中,右键选择Add Wave即可。

添加需要观察的信号

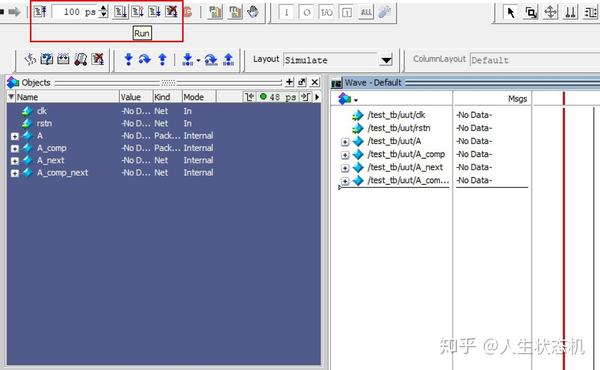

可以看到在右边的波形窗口中已经出现了刚才添加的信号,最后点击上方工具栏的的Run即可,时间框内的100ps表示Run一次的仿真时间。

至此,功能仿真过程结束,可以在右边的窗口中看到波形。

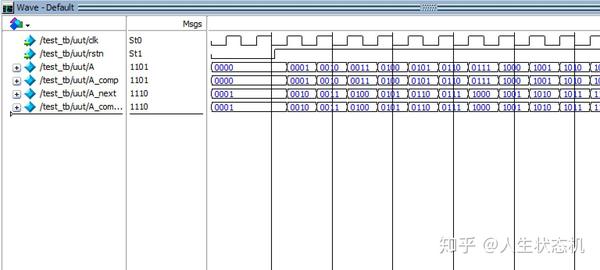

波形图

联合Vivado进行时序仿真

进行时序仿真需要考虑到FPGA实现时布局布线带来的延迟,因此需要在Vivado综合实现后进行(Vivado的基本操作在上一篇文章已经讲过,所以本篇不再赘述),为了联合Vivado和Modelsim软件进行时序仿真,首先需要在Vivado中进行相应的设置。

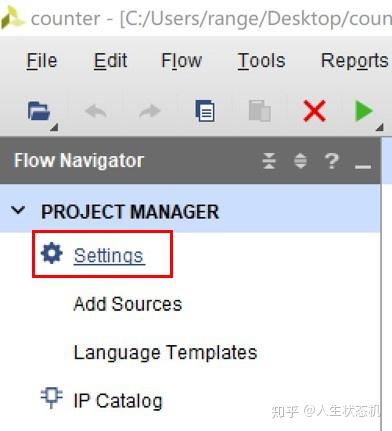

首先从左侧工具栏中的Settings进入设置,如下图。

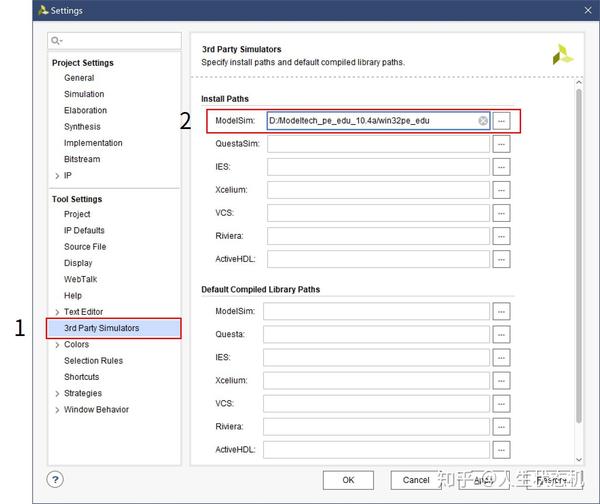

在Tool Settings下方的3rd Party Simulators中找到Modelsim,选择安装路径之后点击OK。

指定第三方仿真器

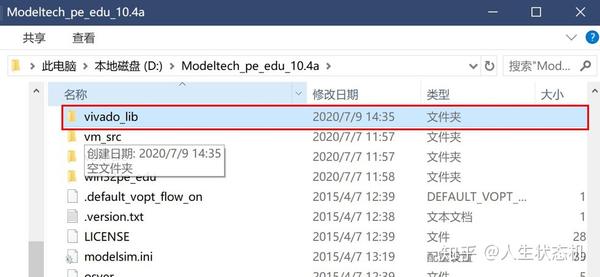

接着在Modelsim的安装路径下新建一个文件夹(vivado\_lib),用于存储仿真库。

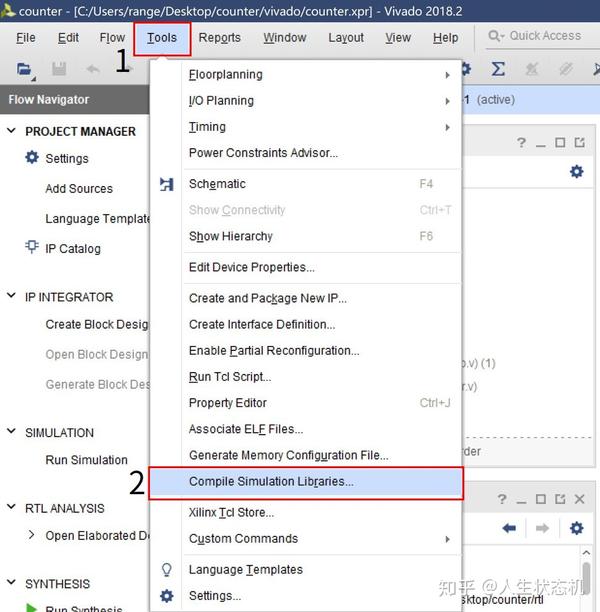

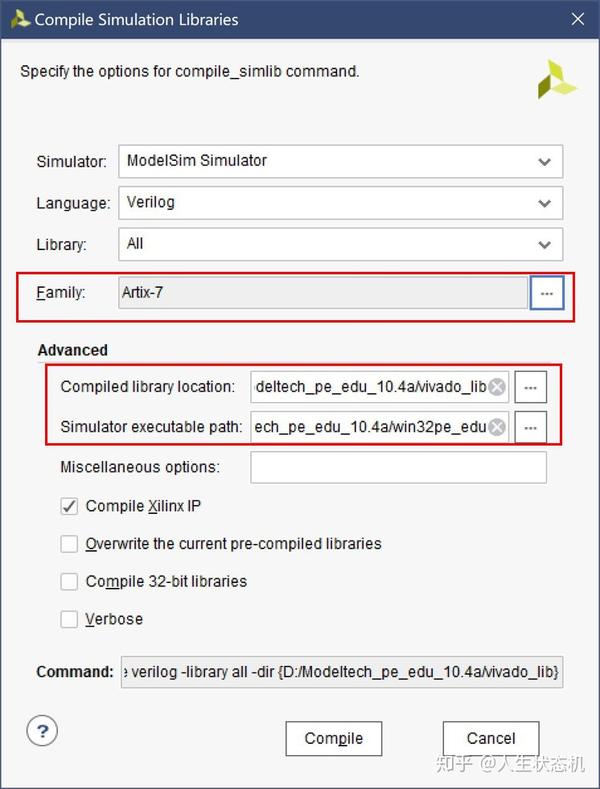

在Vivado中Tools栏下点击Compile Simulation Libraries开始编译仿真库。

编译仿真库

在弹出的界面中选择Modelsim Simulator,器件里选上Artix-7,Compiled library location选择刚才新建的文件夹vivado\_lib,Simulator executable path选择modelsim的安装路径,都选择完成后点击Compile开始编译。这个过程需要等待一段不算太短的时间,建议玩会游戏。

路径设置

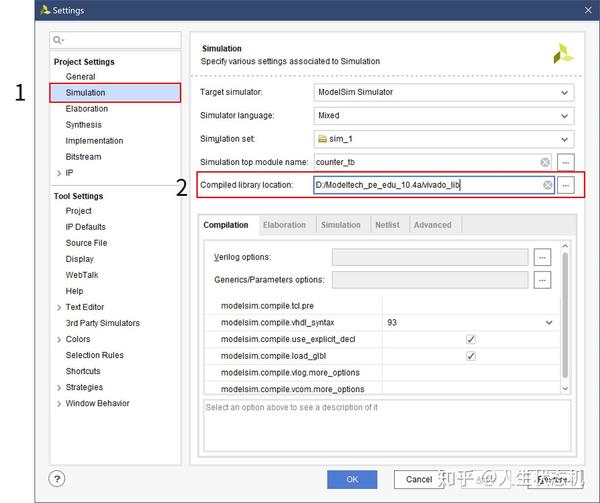

编译完成之后再回到Simulation设置中将Compiled library location设置为刚才新建的vivado\_lib文件夹即可。

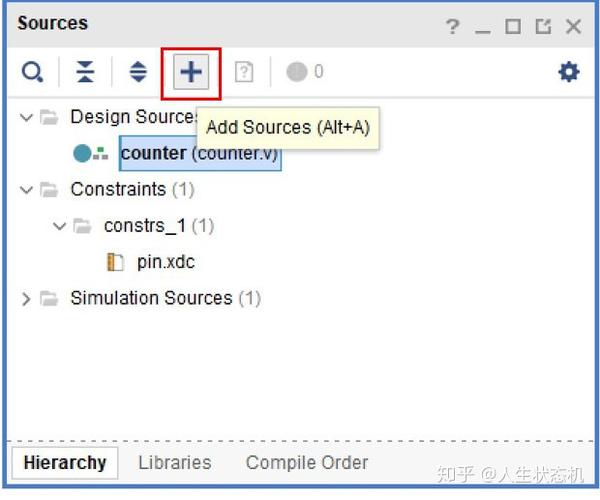

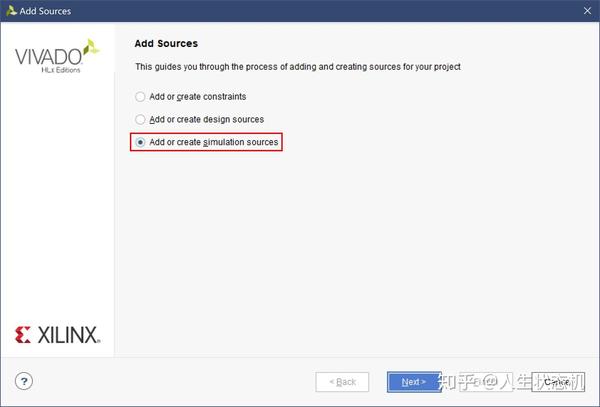

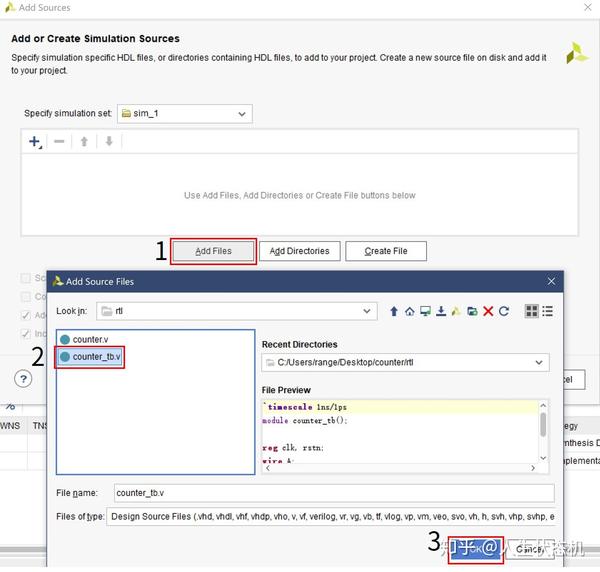

设置完成后,接下来便需要添加testbench文件到工程中,首先在文件管理区点击Add Sources添加文件,在弹出的窗口中选择Add or create simulation sources。

在弹出的窗口中选择Add Files,然后选中testbench文件,点击OK添加到工程中。

添加testbench到工程中

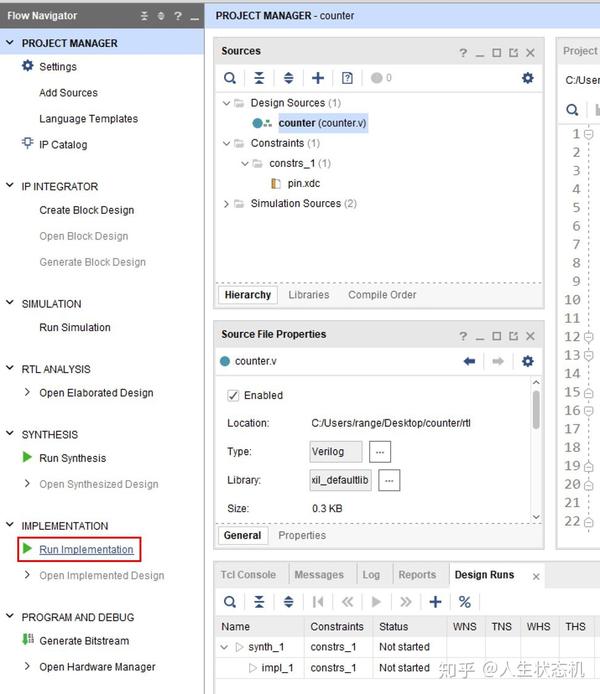

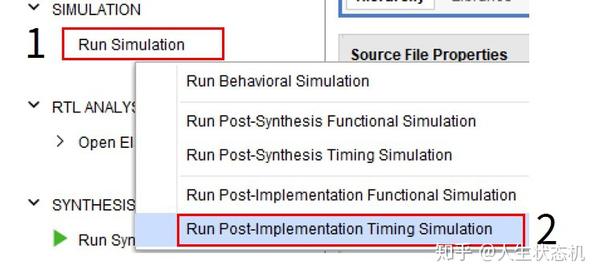

点击左侧工具栏中的Run Implementation开始综合实现,完成后点击Run Simulation然后点击Run Post-Implementation Timing Simulation(实现后时序仿真)开始时序仿真。

开始时序仿真

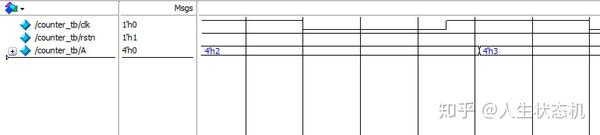

Vivado将会调用Modelsim软件,最后可以观察到如下图所示的波形图。时序仿真过程已经考虑到了实际电路中的延时信息,可以看到,信号A在时钟上升沿后经过了短暂的延时才发生变化。

时序仿真波形图

仿真的重要性

这里扯一点题外话,虽然本文的主旨是介绍仿真工具Modelsim的使用,但仿真的重要性往往被初学者忽视,所以想就这个话题简单谈一谈。上

老师的EDA课时,老师便经常强调仿真的重要性,结合老师上课讲的内容和个人实际的经验来看,如果(自信地)不进行仿真直接在FPGA板上进行验证,最后都得回归到功能仿真这一步来查错。一次功能仿真的时间不到一分钟,而一个比较简单的设计综合实现生成比特流的过程也需要几分钟,所以在上板之前先进行功能仿真查错,既节约了时间,又不会因为上板出现一堆低级错误而懊恼,何乐而不为呢?另外,在SoC设计实验中,如果忽视仿真过程,直接上板跑C程序,出现错误时比较难定位是硬件问题还是软件问题,如果先进行仿真,就可以先把硬件上的问题解决,之后再进行软件调试时效率会高很多。

END

知乎:https://zhuanlan.zhihu.com/p/159451972

推荐阅读

更多内容请关注其实我是老莫的网络书场专栏