开发板概述

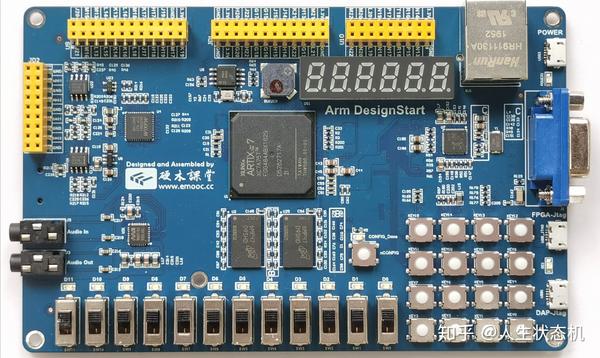

在走近FPGA预告篇中,我们已经提到了系列文章使用的开发平台,硬木课堂Xilinx Artix 7 FPGA板,如下图所示。它使用的FPGA芯片型号为Xilinx Artix-7 XC7A75T,具有电平开关、LED、矩阵键盘、数码管等基本外设,同时还有高速ADC/DAC,音频Codec,SD卡,32位DDR3L(共1GB)外设用于SoC设计的进阶实验,另外,上方的I/O插槽可以直接插入特定型号的LCD屏幕与摄像头,极大地方便了图像处理相关应用的实现。

硬木课堂 Xilinx Aritx 7 FPGA板

FPGA 芯片

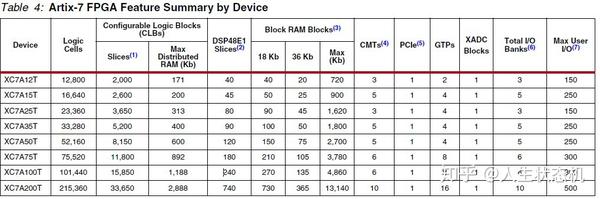

该FPGA板采用的芯片型号为XC7A75T,从Xilinx官网的数据手册中可以找到7系列FPGA芯片的资源对比,可以看出75T在所有Artix-7系列的FPGA中资源量属于中上,虽然相比于100T和200T而言资源量还是少了许多,但是完成基础的FPGA实验和进阶的SoC设计实验(包括图像处理相关)是足够的。75T和100T, 200T的FPGA芯片是兼容的,硬木课堂同时还提供有200T的FPGA板,以应对更复杂的应用场景需求。

FPGA芯片资源(图源数据手册)

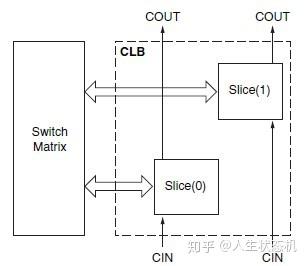

Artix-7系列FPGA芯片采用下图所示的基本可配置逻辑块(CLB),其中包括6输入查找表、可选的双向5输入查找表、分布式存储、移位寄存器、高速进位算术逻辑功能以及大量多路复用器。基本可配置逻辑块(CLB)是用于实现时序电路和组合电路的主要逻辑资源。每个CLB都连接到一个交换矩阵(Switch Matrix),以访问通用路由矩阵。每个CLB内部包含两个slice。7系列FPGA中的LUT可以配置为具有一个输出的6输入LUT,也可以配置为具有独立输出但共享地址或逻辑输入的两个5输入LUT。每个5输入LUT输出都可以选择在触发器中寄存。每个slice由4个这样的6输入LUT、8个触发器、多路复用器和算术运算单元构成。每片四个触发器可以选择配置为锁存器。但在这种情况下,该片中其余的四个触发器必须保持未使用状态。

基本可配置逻辑块结构(图源数据手册)

更多关于FPGA内部原理结构的介绍,可以阅读《FPGA原理与结构》[日]天野英晴主编,赵谦译 这本书,这本书对FPGA的内部原理阐释得比较清楚,对于初学者也比较友好。另外,如果能够找到《FPGA设计指南-器件、工具和流程》 [美] Clive "Max" Maxfield 著, 杜生海 邢闻 译 这本书也不错,感觉作者的语气比较幽默,但是似乎已经买不到新书了(略有遗憾)。在《FPGA原理与结构》中文版出版之前我就是看的《FPGA设计指南》一书,都很好地帮助理解FPGA的原理结构,从而更好地利用FPGA学习电路设计。

下载器+调试器

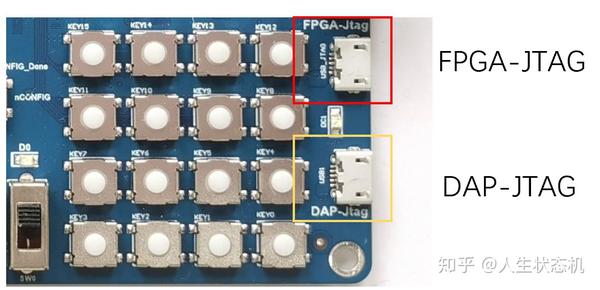

在本系列文章使用的FPGA板上的右下方有两个接口,如下图。其中上方的接口(FPGA-Jtag)为FPGA下载接口,通过该接口下载比特流到FPGA中进行配置,功耗较小时,供电也是PC机通过该接口给板卡供电。如果功耗较大,则需要使用FPGA板右上角的辅助供电接口(POWER),可以使用手机5V充电器给板卡供电。

下载器和调试器接口

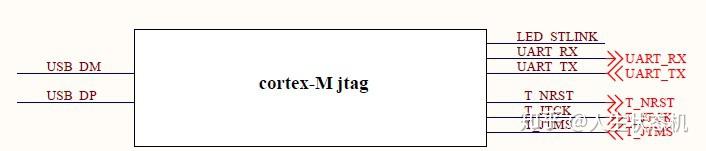

图中下方的接口(DAP-Jtag)为CMSIS-DAP接口,用于Cortex-M系列内核调试,在搭建基于Cortex-M0的SoC时,调试系统是必不可少的,关于调试系统的更多内容在后续的文章中有详细介绍。为了方便使用,FPGA板在设计之初便将调试电路封装在板上,预留出来一个JTAG口用于和PC机通信,这样做不仅简化了对调试器内部原理的理解需求,而且方便了连线。调试器部分的端口需要约束的有一个时钟信号和一个双向的数据信号,结构如图所示。

调试器接口原理图

电平开关和LED

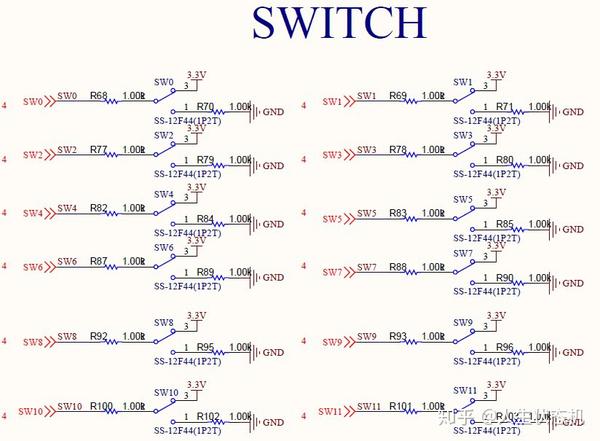

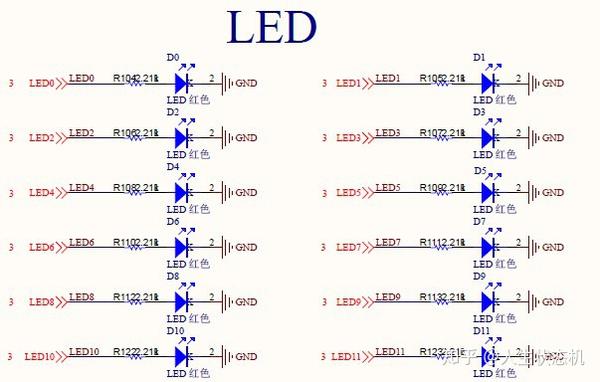

本系列所使用的FPGA板提供了12个直接由FPGA控制的LED灯LED11-LED0,每一个LED灯都由FPGA芯片的一个引脚直接驱动,如图所示。当FPGA的引脚输出高电平时LED灯点亮,反之则熄灭。在LED灯旁边也有12个电平开关,可以作为输入信号,当电平开关处在DOWN位置(靠近开发板边缘)时向FPGA相应引脚输入低电平,当电平开关在UP位置时向FPGA相应引脚输入高电平,如图。

电平开关(SW11-SW0)和LED(D11-D0)

开关原理图

LED原理图

一个简单的流水灯示例如下(之后的文章也会讲到)。

一个简单的流水灯

4x4矩阵键盘

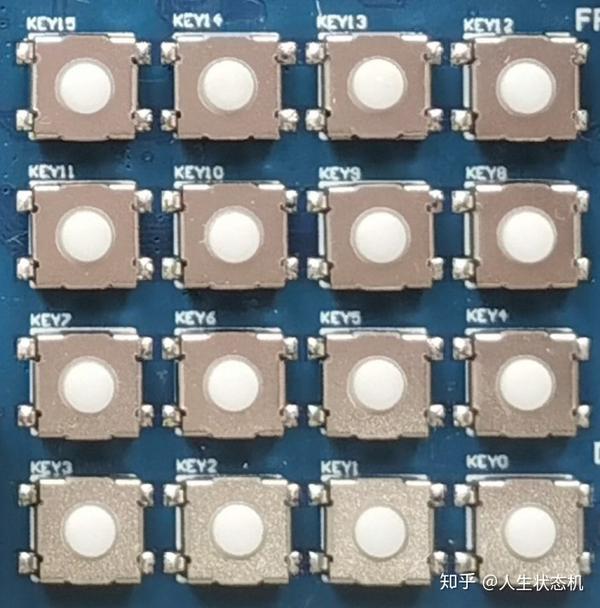

FPGA板带有一个4x4的矩阵键盘,可以用于一些外界的控制交互,如图所示。

矩阵键盘

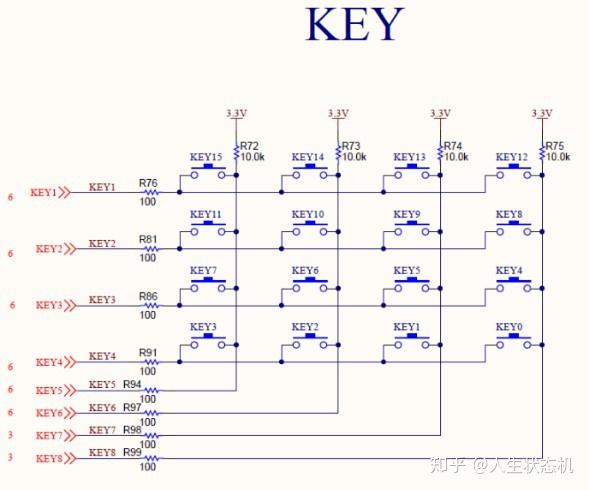

矩阵键盘原理图

左侧的KEY1-KEY8信号分别代表横竖的4个端口,分别与FPGA上的4个输出端口连接。矩阵键盘的工作原理可以举个例子说明,如果将KEY1设置为低电平,KEY2-KEY4设置为高电平,则按下KEY15按键后,KEY5端口输出低电平,松开KEY15按键后,KEY5端口输出高电平。唯一需要注意的是,按下按键时信号存在抖动,所以需要设计按键消抖模块以免按键抖动带来未预期的系统错误。

一个简单的键盘控制流水灯的示例。

键盘控制流水灯

数码管

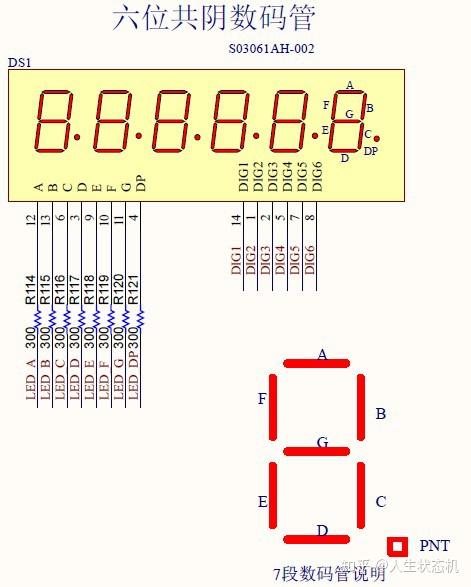

FPGA板上配有配有6个七段数码管DIG1-DIG6(当正放FPGA开发板时,从左至右为1-6),每个数码管都由一个专用片选信号(DIG1- DIG6)控制,如图所示。七段数码管的每个引脚均通过共阴模式连接到 FPGA芯片上,当FPGA输出高电压时,对应的字码段点亮,反之则熄灭。数码管的片选信号也直接与FPGA引脚相连,当FPGA输出低电压时,对应的数码管选中,反之则不选中。

数码管

数码管原理图

一个简单的计数器,使用数码管显示。

计数器(数码管显示)

直插摄像头和屏幕的IO口

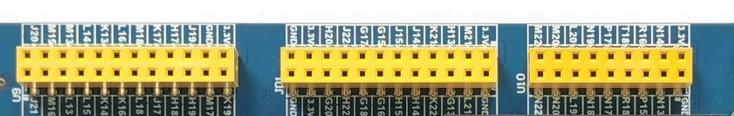

FPGA板上方有3组IO接口,可以用于LCD显示屏和摄像头的直插。

3组IO接口

对于示例中用到的摄像头和LCD显示屏,分别可以直接插到右边和左边的IO接口组,效果如图。在我之前写过的一篇专栏文章中对使用摄像头和LCD显示屏进行开发的过程有更多的描述,另外,在后续系列文章中也会对相关的实验进行详细的介绍。

摄像头+显示屏直插

另外,如果需要连接扩展显示,也可以通过FPGA板右边的VGA接口连接扩展显示设备,VGA接口共有15针,分成3排,每排5个孔,接口原理图如下。VGA接口具有分辨率高、显示速率快、颜色丰富等优点。VGA接口不但是CRT显示设备的标准接口,同样也是LCD液晶显示设备的标准接口,具有广泛的应用范围。

通过VGA接口连接扩展显示设备

VGA接口原理图

高速ADC/DAC

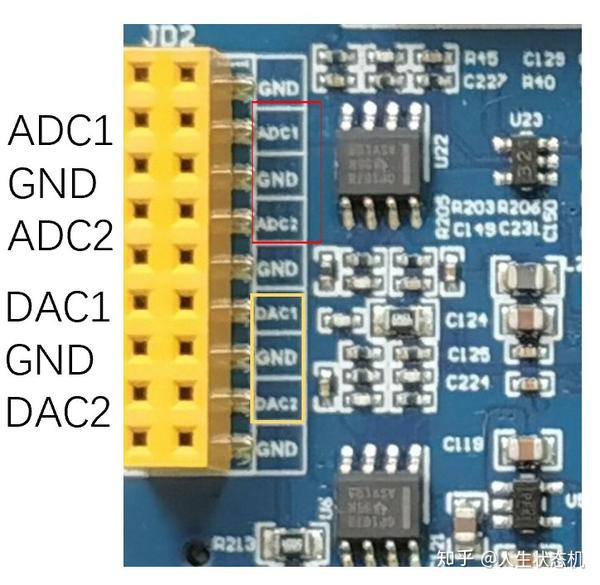

FPGA开发板的左上方是高速ADC/DAC芯片,该芯片是来自 MAXIM公司的超低功耗模拟前端,最高工作频率达到20MHz,芯片型号为Max5865。Max5865集成了双路的8位ADC以及双路的10位DAC,其数字输出电平为+1.8V至+3.3V(TTL/CMOS兼容),且该芯片的ADC和DAC既可以同时工作也可以独立工作。其关断与工作模式由三线的串行接口来控制。高速ADC/DAC芯片左侧的一组黄色贴片排母IO接口包含两组ADC输入接口,分别标识为ADC1和ADC2,还包含两组DAC输出接口,分别标识为DAC1和DAC2,可通过导线与示波器、信号源等仪器相连进行实验。

ADC DAC接口

音频和SD卡

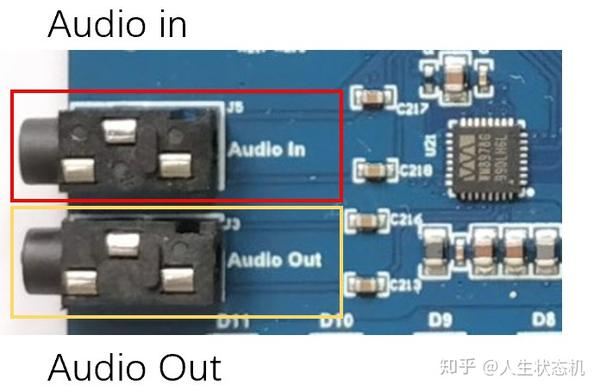

FPGA开发板的左下侧载有立体声多媒体数字信号编译码器芯片WM8978。WM8978是Wolfson推出的一款全功能音频处理器,带有一个HI-FI级数字信号处理内核,支持增强3D硬件环绕音效,以及5频段的硬件均衡器,可以有效改善音质。在音频编译码芯片的左侧有两个音频接口,位于上侧的是音频输入接口,可通过音频连接线连接音频播放设备(如手机)来输入音频信号,位于下侧的是音频输出接口,可以连接耳机播放音乐。另外,在FPGA开发板相同位置的背面,还有一个Micro SD卡的插槽,可放置SD卡。

音频接口

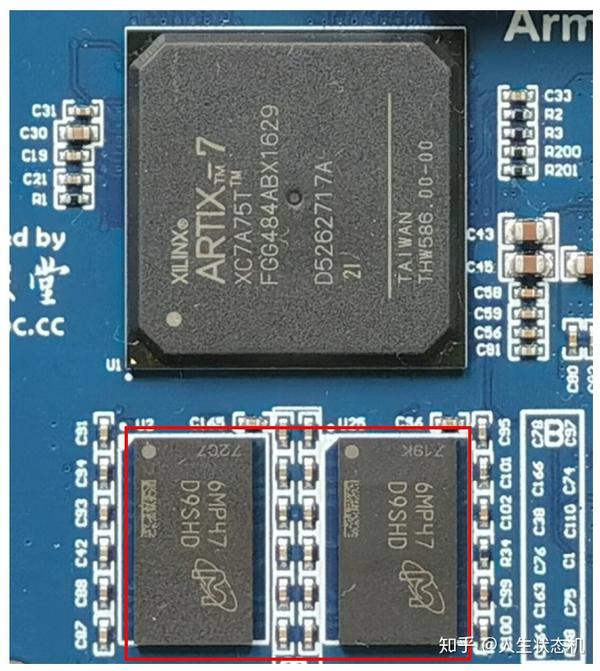

DDR3L

开发板上FPGA正下方是两片DDR3L SDRAM存储器芯片,产自Micron公司。DDR SDRAM的全称是双倍速率同步动态随机存储器(Double Data Rate Synchronous Dynamic Random Access Memory),其在时钟的上升沿和下降沿都能进行数据传输。DDR3是DDR2的后继者,提供了相较于DDR2 SDRAM更高的运行效能与更低的电压。而DDR3L的L是Low Voltage的缩写,DDR3的工作电压为1.5V,而DDR3L工作电压为1.35V。

DDR3L SDRAM存储器芯片

开发板上DDR3L SDRAM芯片的型号为MT41K256M16TW,即一片该DDR3L SDRAM存储器芯片的深度为256M,宽度为16bit (2Byte),故存储器容量为512MB(256M×2Byte),两片DDR3L芯片地址线已经连在了一起,相当于一片深度不变但数据宽度翻倍(32bit)的DDR3L SDRAM,两片存储器芯片构成的存储器总容量为1GB。

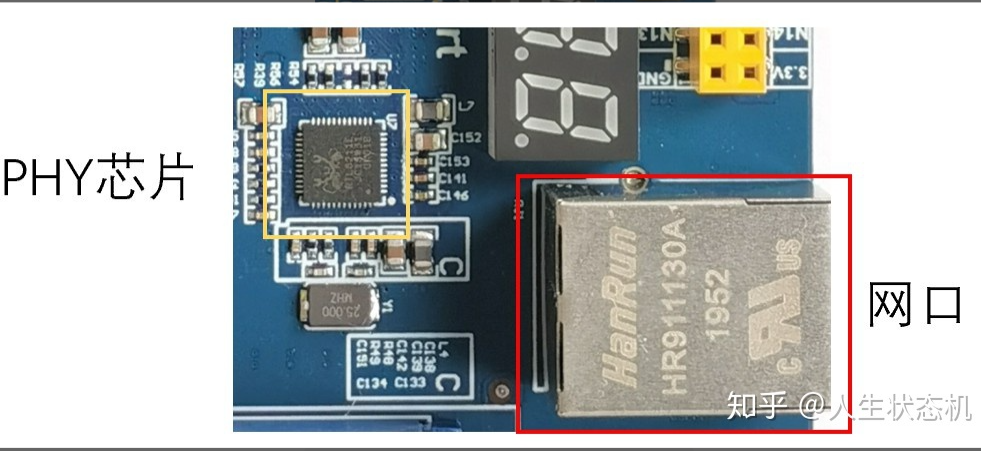

千兆以太网

在FPGA开发板的右上侧载有千兆以太网PHY芯片以及网口。该芯片为Realtek公司的RTL8211E,支持1000Mbps的网络传输速率,通过RGMII接口与FPGA进行数据通信,传输时钟为125MHz,4bit的发送数据TXD与接收数据RXD在时钟的上升沿和下降沿采样。开发版上板载的RTL8211E已配置好RX与TX延迟,工作电压为3.3V。

千兆以太网

下期预告

本期文章介绍了[走近FPGA]系列所使用的开发平台,点击链接即可获得板子内容,下期文章将介绍相关开发工具的使用,敬请期待。

知乎:https://zhuanlan.zhihu.com/p/151347370

更多内容请关注其实我是老莫的网络书场专栏