聆思大模型 AI 开发套件(CSK6-MIX)不仅提供了完善的多模态大模型调用功能,还提供了丰富的本地外设接口,可以通过端侧结合大模型来实...

什么样的人能称为“老司机”?是秋名山车神,还是路怒症十级患者?“道路千万条,安全第一条”,不管车技多牛、驾龄多久,安全意识应该是一...

我们可以看出,实际上有四组表,每组表有四个异常入口,分别对应同步异常,IRQ,FIQ和serror。

思考:1、这里有没有按照armv8定义的异常向量表排列?不是每一个offset只有128bytes地址空间吗,如何做到的?2、Linux Kernel arm64体系...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈软件中定义的向量表,是否和ARM文档中的向量offset一致向量表的基地址是否写入...

有人说,中断就包含IRQ和FIQ,其实这是不准确的,准确的说法应该是:产生到aarch64的异步异常(包括IRQ, FIQ, SError) 可看作中断。官方...

快速连接👉👉👉【精选】ARMv8/ARMv9架构入门到精通-目录 👈👈👈1、gic的版本GIC是一个为Cortex-A和Arm Cortex-R设计的标准的中断控制器2、GICv...

引流关键词:armv8, armv9, gic,gicv2,gicv3,异常, 中断,irq,fiq,serror,sync,同步异常,异步异常,向量表,向量表基地址,VBAR,vbar_...

清除(Clean) 整个高速缓存或者某个高速缓存行。相应的高速缓存行会被标记为脏,数据会写回到下一级高速缓存中或者主存储器中。

AT指令的语法格式:有了上面的语法格式后,就非常好理解armv8的MMU提供了14条AT指令了:MMU的地址翻译一般都是自动进行的,在当前的linu...

Inner shareable cache: 这是ASIC在设计的时候,会把离cpu进的cache定义成Inner shareable cache,软件可以通过读取CLIDR_EL1.ICB比特...

思考:1、cache coherence和memory consistency的区别?2、cache一致性和barrier指令有什么关系?

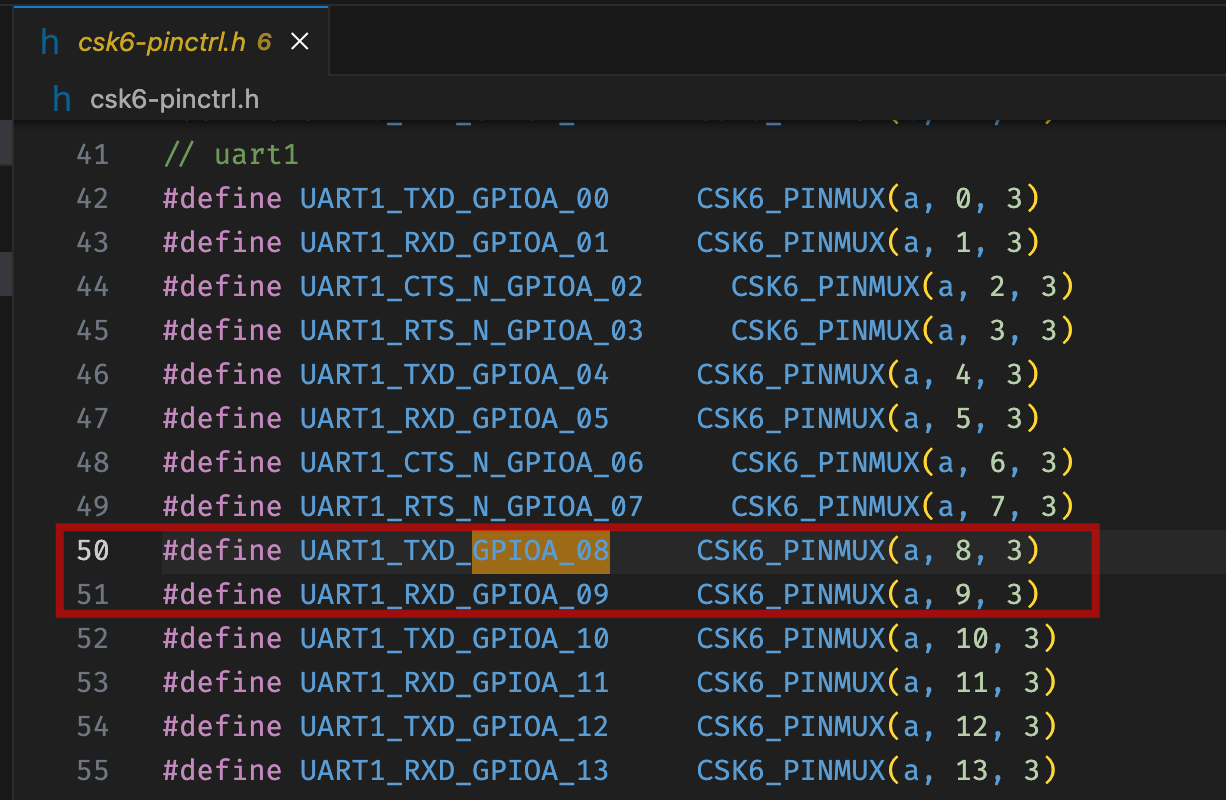

前段时间拿到了一个AI套件的试用,最近正好赶上智谱也有免费TOKEN的活动,就打算看看两者结合起来效果如何。今天只是简单的一个流程上的...

毫无疑问,受宏观经济的影响,当下众多企业正普遍遭受冲击,可以说过去企业“野蛮”生长的时代已经过去。如今,企业以降本增效的方式实现...

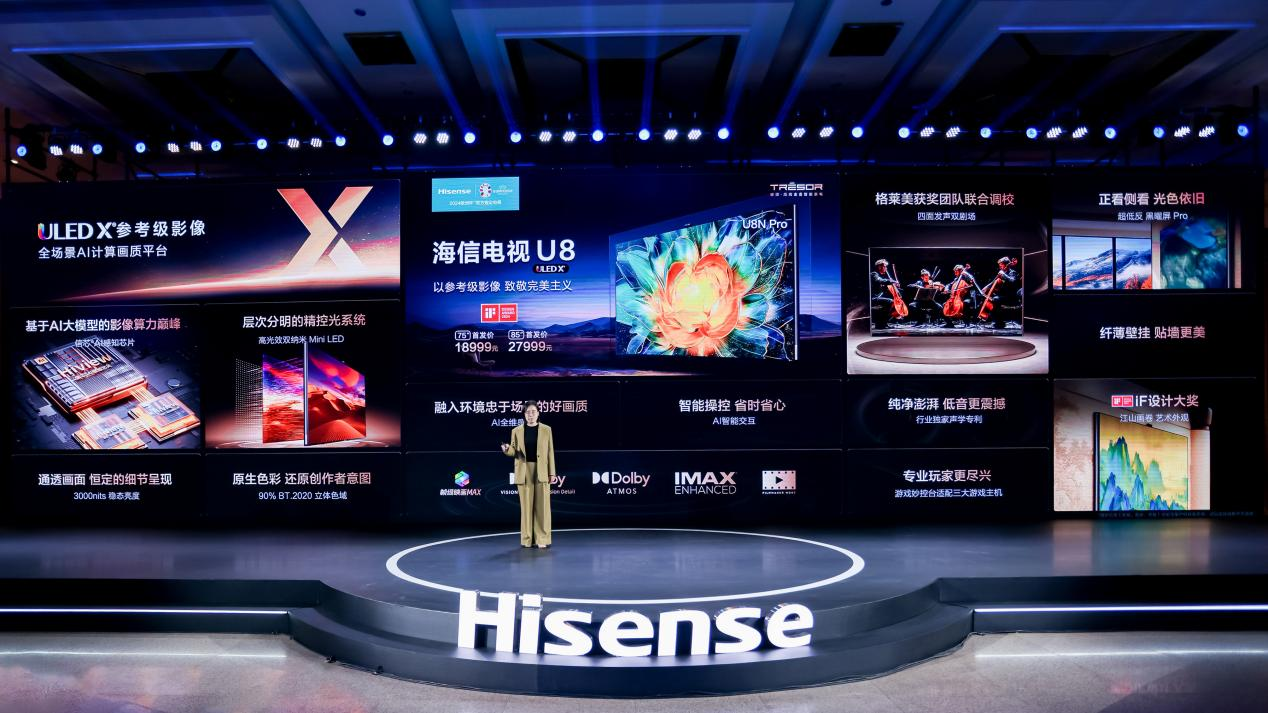

最近上映的科幻大片《沙丘2》,大家都看过了吗?不少影迷奔赴电影院,理由很有意思:大屏幕可以看到最多的沙子。

Cortex-A720核心提供一种机制,通过IMPLEMENTATION DEFINED系统寄存器可以读取L1缓存、L2缓存和Translation Lookaside Buffer(TLB)。...

Cortex-A720核心的L2内存系统通过CPU bridge连接core与DynamIQ Shared Unit-120,其中包括私有的L2缓存。L2缓存是统一的,每个Cortex-A7...

思考:L1 System memory和L1 Cache是什么关系?L1指令cache禁用时,指令cache就真的不会缓存了吗?此时还会出现缓存不一致的情况吗?L1 ...

结构化的思想很普遍,结构化内容也很普遍,我们日常写作的文章,看到的书籍都在使用标题、子标题、段落、句子等语法结构。结构化 Prompt...

关键词: DynamIQ cluster、DSU-110、DSU-120、DSU、cache、mmu、缓存、高速缓存、内存管理、MPAM

思考:在页表的Descriptors中的Lower attributes中的AttrIndx中指向的MAIR_EL1寄存器中有配置cacheable属性, 在TCR_EL1寄存器中有cachea...

思考:在页表的Descriptors中的Lower attributes中的AttrIndx中指向的MAIR_EL1寄存器中有配置cacheable属性, 在TCR_EL1寄存器中有cachea...

缓存替换策略是用于确定在缓存空间已满时应该替换哪些缓存项。Pseudo-LRU(Pseudo-Least Recently Used)和LRU(Least Recently Used)...

内存屏障(Memory Barrier)和缓存(Cache)之间有密切的关系。它们都是计算机系统中用于确保内存操作顺序和一致性的重要概念。

我们知道每一个Arm core的L1/L2/L3的cache是多大的,要么是IP定死的,要么是ASIC可配置的。那么从性能角度来说,是不少配置的越大越好呢...

思考:REE刷TLB时会把安全的TLB刷掉吗?TEE刷TLB时能否刷安全的TLB?例如页表管理着的共享内存,它的翻译缓存到了TLB.

在人工智能的淘金热中,英伟达吃肉,小型关键参与者喝汤。这次我们要说的是正发力在Retimer这个小型芯片的供应商。目前一台典型的配8块G...

3月20日,上海国际半导体展览会SEMICON China 2024盛大开幕。作为中国规模最大的半导体业界盛会之一,SEMICON China囊括了当今半导体制...

芯片是科技发展的核心关键和技术底座。当下RISC-V、Chiplet、AI、汽车电子等成为该行业的高频词。这两年的半导体行业,皆围绕着这几个技...

一直以来,我都认为算力网络是行业整合的过程,通过算力网络运营商把全国的算力资源统筹到一起,形成高效的统一算力供应。但与此同时,...