“DeepFaceLab”项目已经发布了很长时间了,作为研究的目的,本文将介绍他的原理,并使用Pytorch和OpenCV创建一个简化版本。

ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然而...

2023年的4月,伴随着疫情三年的封控结束,上海迎来了重新开放后的第一次线下大型国际车展,众多的整车集团在车展中集中展出了自己的品牌...

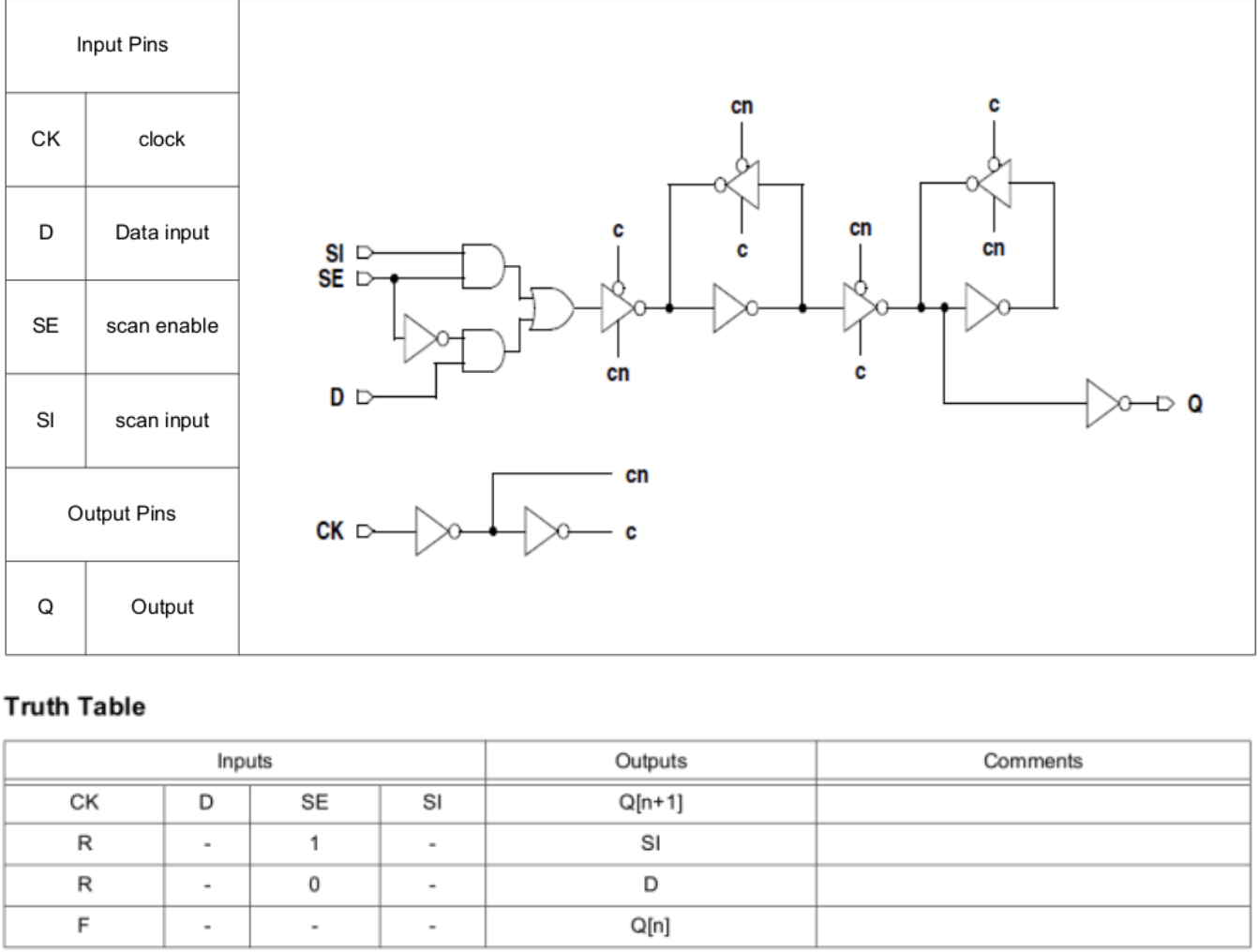

下图所示为上升沿触发的无复位静态D触发器,拥有扫描输入input接口SI和扫描使能SE,D端口是输入数据口,Q是数据输出口。忽略扫描链信号S...

精确的3D感知系统对于自动驾驶至关重要。经典方法依赖于激光雷达点云提供的精确3D信息。然而,激光雷达传感器通常花费数千美元,阻碍了...

分别在每个页面上中放置一个Label(最简单的显示组件),分别填入不同的字符串,例如Welcome,YOU,Hello等。

为了保证光伏储能系统的正常工作,往往通过采用两级结合的拓扑(DC-DC与DC-AC)来接入电网或供应负载,但功率级数增多,总效率下降,且硬...

随着数字光处理技术(DLP)和液晶显示器技术(LCD)的不断发展,市场上能实现4K@60Hz超高清投影的投影机型号日渐增加,对投影仪器性能的要求...

随着 ChatGPT 的爆火,强化学习(Reinforcement Learning)和语言生成模型(Language Model)的结合开始变得越来越受人关注。

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。

内容一览: 犬类嗅觉灵敏,是执行困难任务的得力助手。然而,工作犬选拔需要经过严格的筛选和训练,淘汰率极高。利用监督式机器学习和任...

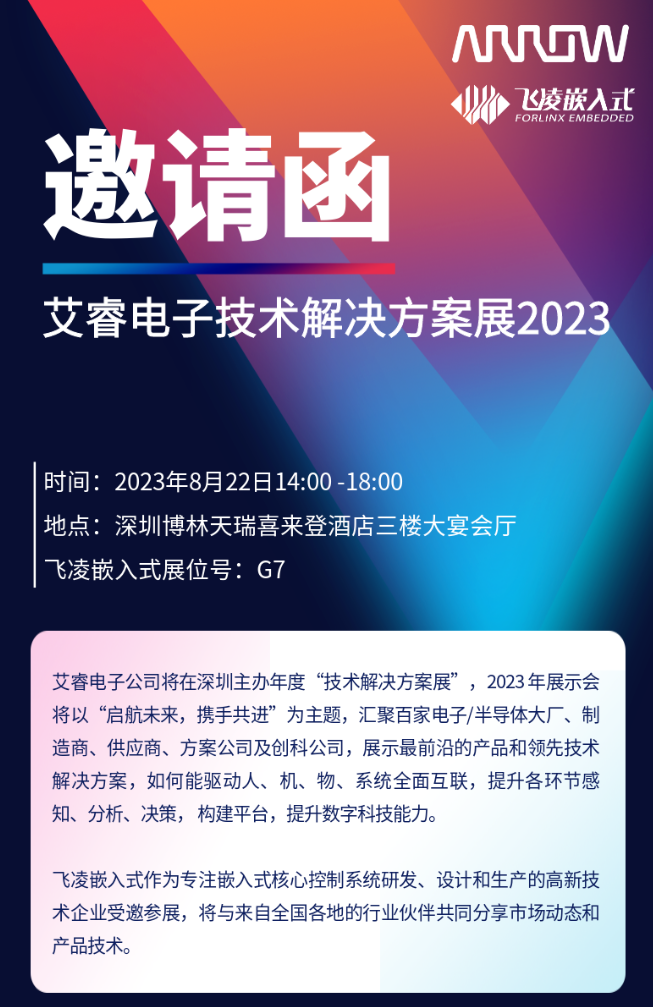

相约艾睿电子技术解决方案展,探讨科技无限可能相约艾睿电子技术解决方案展,探讨科技无限可能相约艾睿电子技术解决方案展,探讨科技无...

这篇文章的目的是详细的解释Flash Attention,为什么要解释FlashAttention呢?因为FlashAttention 是一种重新排序注意力计算的算法,它...

8月23日,由电子发烧友网主办的“智向远大,能者千面”第七届人工智能大会将在深圳会展中心举办。行业顶尖专家、学者和企业代表等将共同探...

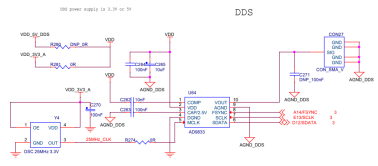

本节视频的目的是掌握EMIFA的使用,了解AD7606的芯片特性和使用,并实现基于AD7606采集正弦波。

正当人们还在讨论未来算力会朝哪个方向发展之时,2023年AI大模型就以迅雷之势掀起了新一轮热潮,为AI在自然语言处理、图像识别、语音识...

集微网消息,自ChatGPT爆红以来,生成式AI(Artificial Intelligence Generated Content,AIGC)已迅速成为ICT领域焦点。

驶过跌宕的三年,一个风起云涌的时代进入重塑期。幸运的是,在这个变革的年代,开发者们作为创新前沿的探索者,始终保持不变的激情。生...

集微网报道 (文/陈炳欣)AI大模型领域近来依旧热闹非凡。最新报道,谷歌或将于今年秋季推出Gemini大模型,重新争夺AI头把交椅位置。Met...

前置摄像头在现代汽车中扮演着关键角色,是车辆的"眼睛",支持着多种车内安全功能(自动紧急制动、陆地偏离警告、车道保持辅助、交通标...

集微网消息,两年前甜蜜的收购约定,随着英特尔与高塔昨日先后发表的终止声明化作泡影。外界解读原因,称反垄断监管未获通过,业内高谈...

集微网报道 (文/陈兴华)近几个月来,国内多家主流手机品牌以及汽车制造商等,都在印度遭遇到了税务及合规等方面的严格审查,而印度政...

...

在ASIC设计或者FPGA设计中,我们常常使用异步fifo(first in first out)(下文简称为afifo)进行数据流的跨时钟,可以说没使用过afifo...

引言LVGL中的timer对象基于timer对象实现仪表走针小结引言设计GUI的显示元素动起来,实际上是多张图按照一定的节奏和变化依次刷屏实现的...

在人工智能领域的不断发展中,语言模型扮演着重要的角色。特别是大型语言模型(LLM),如 ChatGPT,已经成为科技领域的热门话题,并受到...

集微网报道(文/林美炳)液晶面板行业刚刚经历最长下行周期之后,2023年上半年消费电子市场仍没有回暖,面板行业竞争进入白热化,老旧低...

神经网络量化旨在通过使用低位近似加速和修剪全精度神经网络模型。采用量化感知训练(QAT)范式的方法最近有了快速增长,但往往在概念上...

内容提要引言1. 车规芯片的四大行业标准(技术壁垒)1.1 汽车行业铁律--IATF-169491.2 车规芯片可靠性验证标准--AEC-Q1001.3 车规芯片功能...

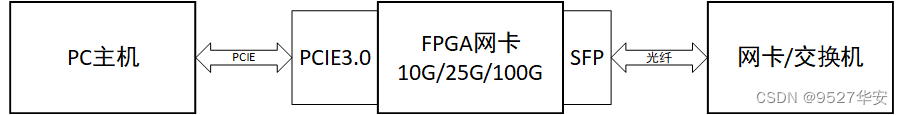

FPGA实现 NIC 100G 网卡,GTY+100G Ethernet Subsystem架构,纯verilog代码实现,提供2套工程源码和技术支持