本文首发于知乎。

写在前面

本文主要记录本人最近折腾的一些经历,总结近期学习心得。由于本人水平有限,文中不足之处欢迎指出。

为什么想写这篇文章

学过一门计算机系统结构相关的课(微电子专业),上过这课的同学应该都“深(yi)有(yan)体(nan)会(jin)”。我一直认为学习新事物需要从尽量简单的地方入手,但实验使用的硬件平台是Zynq,不知道厉害的同学是怎么做的,我只记得我做得很糟糕。但是,过了很长一段时间我才意识到自己对计算机系统结构的无知。幸得大佬指点,在不断摸索中,慢慢熟悉了cortex m0/m3,总线,各种外设,也慢慢解开了之前上系统结构相关的那门课时的很多疑惑......

直接用Zynq也许更适合一部分人的学习习惯,但对于我来说,从裸核开始一步步搭建出完整的SoC或许是更好的学习方式。有道是“纸上得来终觉浅,绝知此事要躬行”,如果想要理解SoC,自己搭建SoC可能是最好的方法。

对比两种亲身体会的学习过程后,深知正确的方法对于快速入门的意义,于是写下这篇文章,作为记录,也作为分享。

什么是Arm DesignStart

Arm DesignStart是Arm的一个项目,开放了一系列IP,包括Cortex-M0,Cortex-M3,Cortex-A5等,每一种IP也有不同的版本:Eval版,FPGA版,Pro版等。

Arm开放的Cortex M0/M3让我们有机会学习研究,在DesignStart官网上可以获取到。

https://developer.arm.com/ip-...

其中,Eval版本提供处理器核的网表形式的Verilog代码,学习时下载的Cortex M0 Eval版,其余部分版本需要申请License,具体申请事宜可以在网站上查询。

搭建SoC

在下载的Eval版文件资源中找到"cortexm0ds_logic.v"的文件,便是处理器核的网表形式的Verilog代码。

想要搭建出一个完整的SoC(如具有图像采集功能的SoC),从获取cortex m0开始,还需要完成以下步骤:

- 理解处理器核端口信号并进行正确的端口配置

- 学习AHB Lite总线协议,理解数据传输时序,编写总线互连模块

- 编写基本外设及接口-存储机器码和数据的RAM

- 编写扩展外设接口-如摄像头,LCD显示屏

- 学习中断控制,编写UART进行与PC间通信,或利用矩阵键盘交互,在显示屏上观察反馈

经过以上一系列看似简单实则到处都是坑的步骤后,就具备了继续研究更复杂的处理器、总线协议、外设的基础,而这种基础,似乎在做Zynq相关实验时我并没有获得(吐槽+1)。

扯远了。

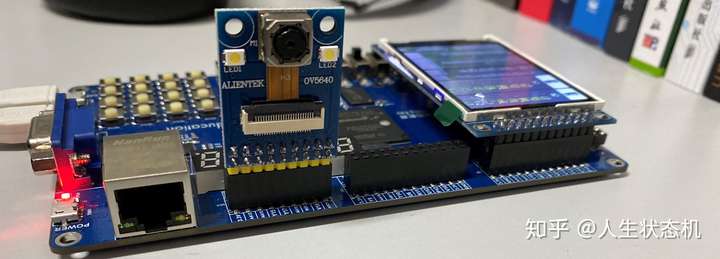

在加了显示屏和摄像头之后可以拍照显示了。

搭建SoC之后

在获得新知识的快感后,因为知道自己还是很菜,所以冷静下来继续深入研究:

- 更复杂的处理器(多核/众核)、更复杂的总线协议(如果有必要~

- 如何在SoC中嵌入硬件加速器(可以参考知乎用户 其实我是老莫 的系列文章《以软制硬,以硬助软:在芯片中嵌入处理器的两种形式》)

- 学习更多算法及其高效硬件实现方法,如卷积运算等

- 增强代码能力(雾

总结

我们可以用Arm DesignStart开放的处理器核搭建简单的SoC,并在这个过程中逐步学习处理器、总线互连、软硬协同的基础知识,同时增强代码能力(和抗压能力)。

敬请期待

使用Cortex M0搭建的SoC已经在github上开源:

https://github.com/liufengrui...

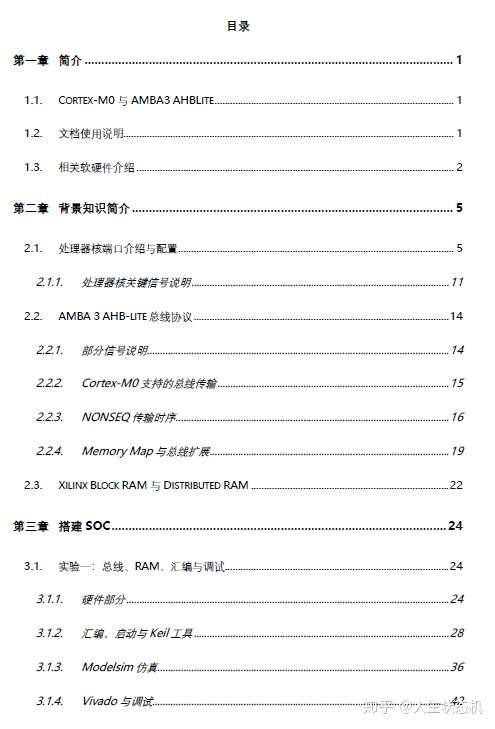

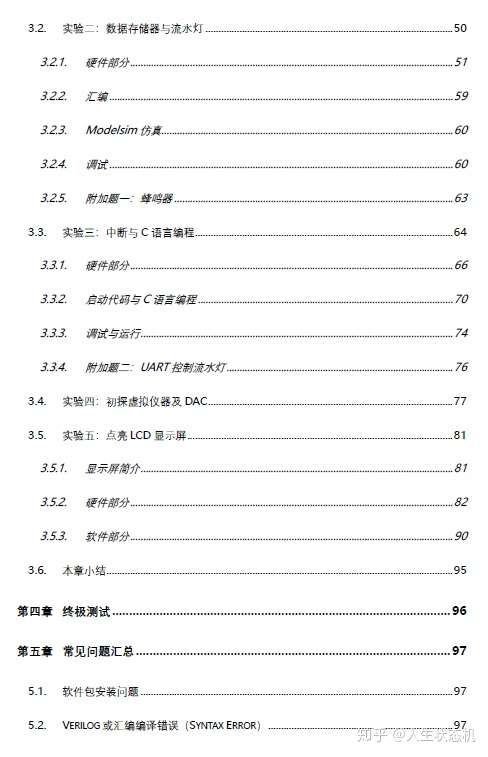

为了方便一步步地搭建SoC,还整理了一份将SoC搭建分为多个Task的版本(以下简称Task版)。Tianjin Zhao和我针对Task版写了一本简单的教程,从获取处理器核开始,一步一步搭建SoC,对FPGA及相关软件的使用也有必要的提示。本教程将于2020年在电子工业出版社出版,敬请期待。下面附上目录。

参考书目

《ARM Cortex-M0与Cortex-M0+权威指南》第2版,Joseph Yiu

《计算机组成与设计硬件软件接口》第5版ARM版,David Patterson and John Hennessy