2018年第23届Asia and South Pacific Design Automation Conference(ASP-DAC)的Tutorial-3的题目为_Machine Learning for Reliability Monitoring, Mitigation and Adaptation_[1]_,_即使用机器学习来监测、缓和与自适应成电路中的各种可靠性问题。在此Tutorial中,集成电路可靠性的相关技术被机器学习分割为了两个部分...

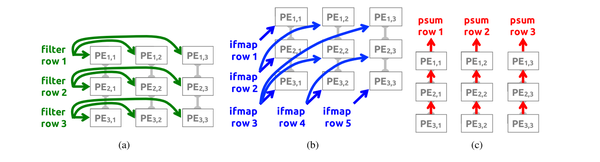

Eyeriss是一种高能效、可重配置的神经网络加速器,有两篇相关的文章[1][2]。针对当时深度神经网络面临的问题:数据搬运带来的时间和能耗开销大,作者提出了两种方法,RS(row stationary)和压缩(利用数据的特点进行)。

2018年已经到了最后一个月了,回顾去年底写的计划,发现还有好多没做。在接下来的一个月里面得抓紧时间得把没有完成的工作完成了。

而这个里面其中有一个重头戏就是得把新版的《数字电路与系统设计》这本书初稿给搞完了。这是一本新的书。要彻底改变过去那种数字电路只讲74,和EDA/硬件描述语言“两张皮”的现象,就意味着要彻底改变现有教材的体系结构,所以还真是不太好写。

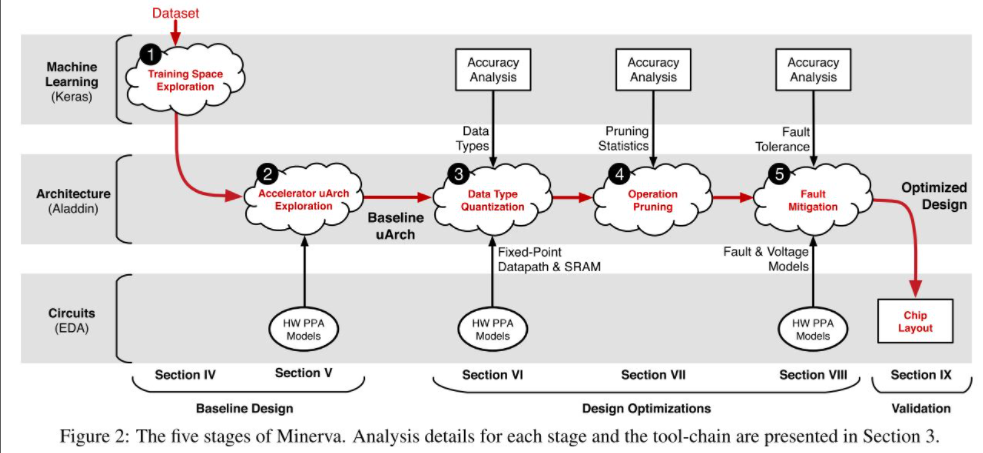

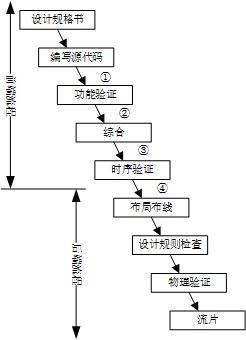

Minerva这篇文章介绍了一种当前低功耗神经网络加速器设计的方法。同时,本文结合该方法,利用当前设计低功耗神经网络的技术,设计了一个低功耗的神经网络推断加速器。Minerva给出的设计方法非常具有参考价值,它的设计流程是我们设计加速器时应该遵守的。Minerva的设计流程如图1(原文Figure 2)所示,把设计加速器的流...

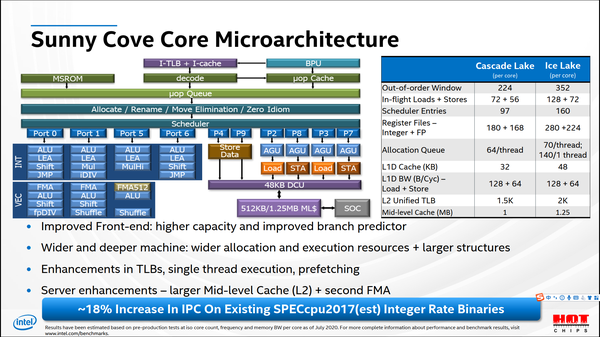

HotChips全称为A Symposium on High Performance Chips,每年8月份举行。不同于其他会议以学术研究前沿为主,HotChips是一场产业界的盛会,以各大处理器设计公司的最新产品或在研产品为主。IBM、Intel、AMD、ARM等都是HotChip会议的常客。HotChips能够让从业者了解产业发展趋势。

MPU和MCU是微处理器与嵌入式系统领域比较重要也比较容易混淆的两个概念。然而和很多技术名词一样,这两个技术名词长期以来在国内被混淆得比较严重。这一方面由于我国是技术后发国,这些概念本来也是从国外引进的,在引进过程中由于翻译和传播的问题有不到位的理解。另一方面是由于很多教材、资料编写过程中存在不严谨的...

学过一门计算机系统结构相关的课(微电子专业),上过这课的同学应该都“深(yi)有(yan)体(nan)会(jin)”。我一直认为学习新事物需要从尽量简单的地方入手,但实验使用的硬件平台是Zynq,不知道厉害的同学是怎么做的,我只记得我做得很糟糕。但是,过了很长一段时间我才意识到自己对计算机系统结构的无知。幸得

要想深入理解Verilog就必须正视Verilog语言同时具备硬件特性和软件特性。在当下的教学过程中,教师和教材都过于强调Verilog语言的硬件特性和可综合特性。将Verilog语言的行为级语法只作为语法设定来介绍,忽略了Verilog语言的软件特性和仿真特性。使得初学者无法理解Verilog语言在行为级语法(过程块、赋值和延迟)背后...

在每年找工作的时候,在校学生就会分割成软件岗位和硬件岗位两大阵营。心仪软件岗位的同学就是专注于各种算法和语法宝典;而立志硬件岗位的同学则会专注于数字电路、模拟电路、单片机、FPGA。出现这样的情况,一方面是因为个人兴趣和工资收益使然,另一方面也是因为公司招聘岗位的刻意引导。

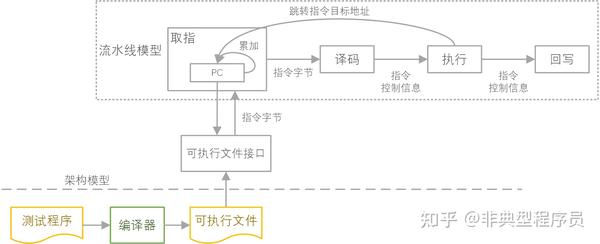

处理器架构模型用来在设计初期进行需求分析和设计方案评估,是架构设计阶段必须的工具。架构模型的开发也同样是一项严格的软件开发工作,也需要有严谨的架构设计和方案选择。这一次就探讨一下如果选择处理器架构模型的激励源。架构模型根据激励源模拟处理器执行测试程序的行为。首先需要说明的是,本文探讨的处理器不仅...

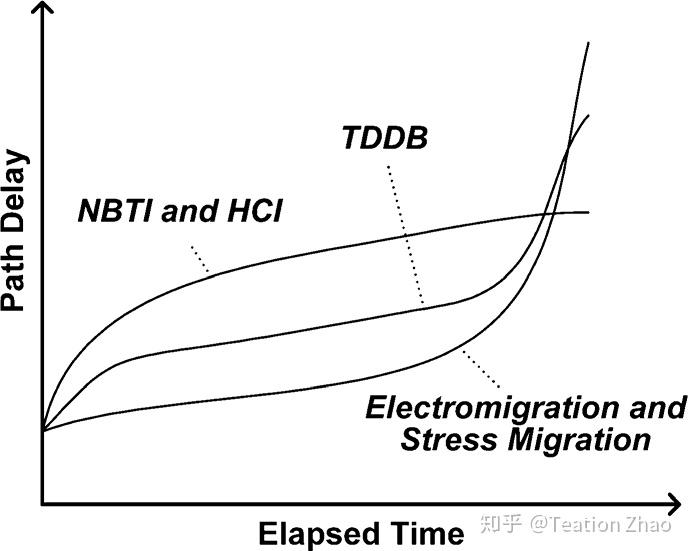

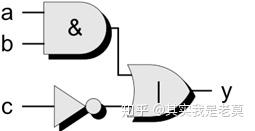

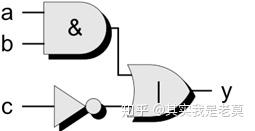

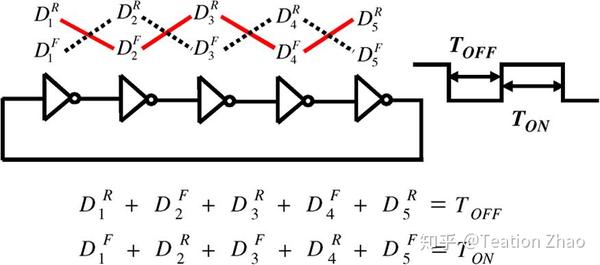

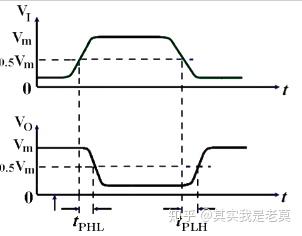

当一个单输入单输出的组合逻辑,满足输出与输入反相时,将输出与输入短接后便形成了一个环形振荡器,能够在没有外部时钟驱动的条件下自振荡,振荡频率一个重要的特性就是与电路延迟有关。因此针对其震荡频率进行测量,再对PVT进行修正,就能得到一个归一化的电路延迟信息,那么这个延迟信息就能作为电路老化表征的直接体...

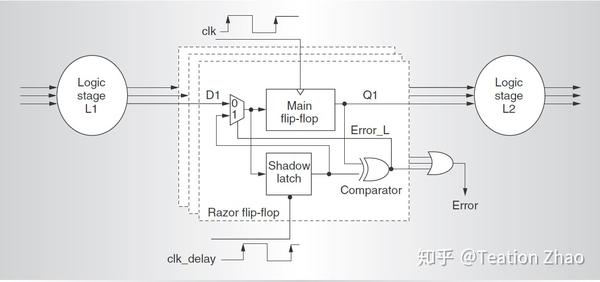

在前两篇专栏文章中介绍到了当前集成电路老化监测、缓和与自适应的手段,其中最主要的就是In-Situ Sensors(原位传感器)方法,通过在目标关键路径中插入原位传感器来实时监测电路参数,而Razor触发器则是原位传感器中时序违例监测的典型代表。

2014年3月,我曾经写过一篇文章:为什么不推荐为了找工作而学习FPGA里面讨论为什么我不建议一个没有基础的学生为了找工作而选择去学习FPGA。这篇文章和我最早写的为什么很多人觉得FPGA很难学一样被广泛的转(piao)发(qie)。很多个人博客、自媒体之类的转发的时候连个转发字眼都没有,更不要说把原文链接加上了。当然...

在网络模型中,物理层是信息传输的基础和载体,主要作用是实现信号在物理介质上的可靠传输。而要实现信号在物理介质上的可靠传输就涉及到了信号处理、编码原理、电子技术、电磁场与电磁波等多个领域的知识。这部分知识其实挺庞杂的,可以说通信工程这个专业四年大半时间都在搞懂这个问题。而剩下一小半时间则是在学习网...

说的网络分层模型,想必现在但凡有点网络常识的学生都应该知道。多年来通信专业的教育给我留下的最深刻的烙印就是我可以对ISO提出的OSI七层模型倒背如流:从底层到上层依次是物理层、数据链路层、网络层、传输层、会话层、表示层、应用层。当然,正着也可以背下来:应用层、表示层、会话层、传输层、网络层、数据链路层...

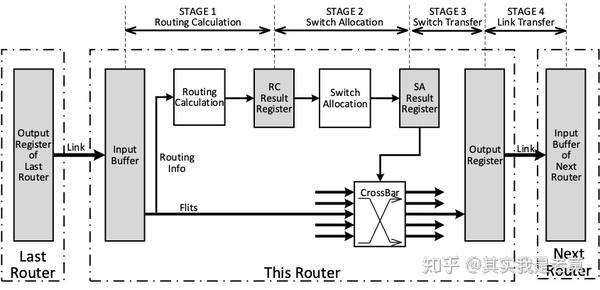

上一篇文章讨论了片上网络的研究需求,经过朋友圈转发以后引起了大家的一些热议和讨论。很多朋友急不可耐的催更,也有一些朋友提出了一些问题。这些问题有时候问得过于“简单直接”,比如有人问在什么时候应该用片上网络什么时候可以用交换矩阵。其实简单直接的问题往往没有简单直接的答案,这类问题的答案一般都有一个固...

为了不拖更,现在也只能把原来比较宏伟的写作计划往简化了去搞。(此处应该有一配图,但是找不到那张图了所以先暂时空在这里)目的呢还是能尽快的把片上网络的相关内容都给大家过一遍。

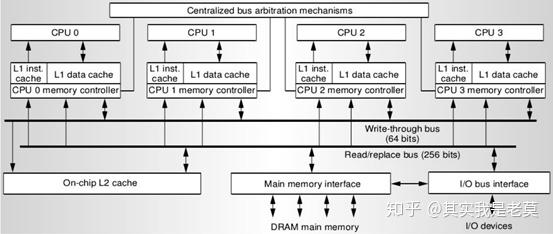

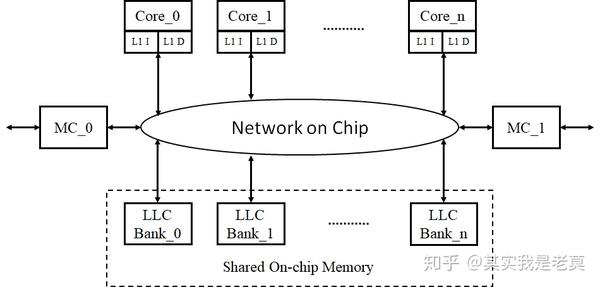

在第一部分我们已经阐述清楚了,片上多核系统分为CMP和MPSoC两种架构。CMP架构的特点是采用共享存储来交换数据,换言之就是每一个核心其实是可以“看见”完整的地址空间的。而MPSoC则更像是多个独立的子系统在单个芯片上的集成,一般是“按需设计”,多个系统之间的存储空间一般相互不可见。

系统级芯片也被称为片上系统,是指在单个芯片内部实现大部分甚至完整的电子系统功能的一种芯片。这种芯片是高端电子系统的核心,随着集成电路工艺技术的发展也逐步向中低端电子系统发展。如今,很多诸如腕表、手环之类的可穿戴设备以及智能玩具等低端嵌入式设备也都以系统级芯片为核心来开展设计。可以说片上系统已经成...