SoC的基本概念

SoC(System on a Chip)的维基百科词条中有如下解释:

A system on chip is an integrated circuit (also known as a "chip") that integrates all components of a computer or other electronic system. These components always include a central processing unit (CPU), memory, input/output ports and secondary storage – all on a single substrate or microchip, the size of a coin.

SoC是指集成了一个完整计算机系统(或者是其他电子系统)的芯片,通常由中央处理器(CPU)、存储器、输入输出接口组成。

在现代SoC设计技术的理念中,IP(Intellectual Property)是构成SoC的基本单元。这里的IP可以理解为满足特定的规范和要求,并且能够在设计中反复进行复用的功能模块,通常称其为IP核(IP Core)。SoC由于集成了一个完整的系统,通常具有非常大的规模,因此以IP核为基础进行设计,可以缩短设计所需的周期。

SoC示例

下图是Wu等人在2012年ASPDAC上发的一篇论文中介绍的SoC[1],文中有几句话对于理解SoC的原理有一定帮助。

The baseband processor including inner receiver and out receiver demodulates the received signal and stores the generated data streams of audio and video to share memory. When share memory is nearly full, an external interrupt from the baseband processor will be generated to inform the RISC processor to initial implementation of MAC layer. After MAC layer operation, 32-bit RISC processor transfers the data of share memory to SPI or SDIO interface, and then SPI or SDIO module is implemented to send data streams to video decoder.

这段话的意思是:下方的基带处理器经过一系列的运算处理后将数据存放在Share SRAM中(见Baseband Processor和32-bit RISC Processor之间RS Decoder to Share SRAM的箭头)。当SRAM快满时,baseband processor会产生一个中断信号,发送到RISC processor,启动对MAC layer的处理,处理完后RISC processor再把数据发送到SPI 或 SDIO接口输出到video decoder。

可以简单理解为基带处理器这个IP核对接收到的信号做预处理,外部产生了一个中断信号,CPU进行中断处理,去存储器中取数据,计算完成后将数据通过总线发送到外设接口,写入外设。这就是SoC常做的事,而这个图里的SoC采用了“通道”加速器形式。在系统中嵌入加速器有多种方法,更多内容可以详细阅读知乎用户其实我是老莫的《以软制硬,以硬助软》系列连载文章。

Block diagram of digital baseband SoC

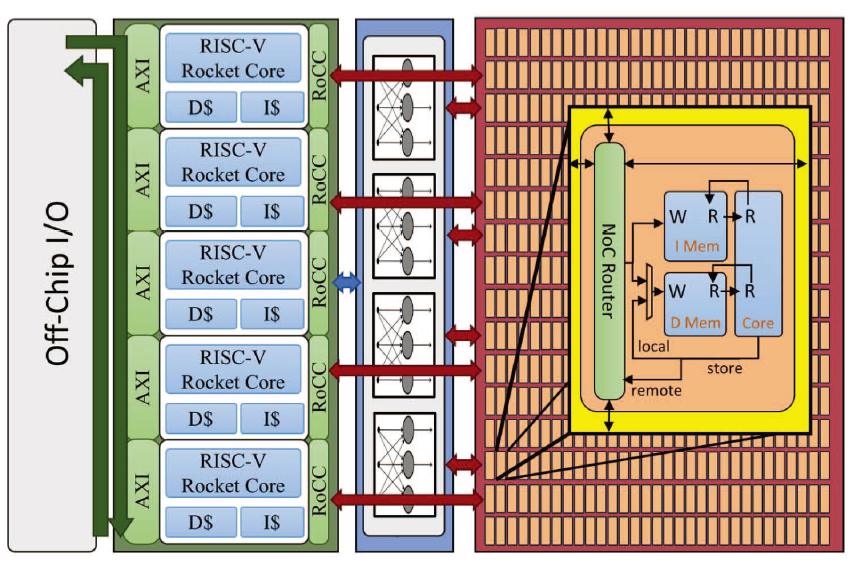

下图为一个更加复杂的SoC[2],主要由通用层(the general\-purpose tier)、专用层(specialization tier)、大规模并行层(the massively parallel tier)组成(从左到右)。通用层用于控制,专用层用于加速神经网络,大规模并行层用于高能效的大规模并行计算。

从Celerity的结构中我们也可以看出复杂SoC设计的要点便是合理地划分模块,让每个模块都做自己擅长的事情,当模块越来越多时,模块间的互连问题便显得非常重要,有关更多复杂模块互连的内容,请参考知乎用户其实我是老莫的《详说片上网络》系列连载文章。

Celerity block diagram

走近SoC系列预告

本文是走近SoC系列的预告篇,简要介绍了SoC的基本概念。走近SoC是为了普及SoC设计的基本概念和基础知识,支撑大学生集成电路创新创业大赛的Arm杯的顺利开展而撰写的一系列文章。我们之后会陆续更新走近SoC系列的更多文章,详细介绍SoC的设计思想,并在知乎同步更新。

参考文献

[1] Wu C, Cao J, Bao D, et al. A 60mW baseband SoC for CMMB receiver[C]//17th Asia and South Pacific Design Automation Conference. IEEE, 2012: 479-480.

[2]Davidson S, Xie S, Torng C, et al. The Celerity open-source 511-core RISC-V tiered accelerator fabric: Fast architectures and design methodologies for fast chips[J]. IEEE Micro, 2018, 38(2): 30-41.