本文是本系列第一篇,笔者最近在研究基于FPGA的算法加速,本系列将以 PPT 结合文字的方式,以实现相对简单的 SM3 杂凑算法为例,介绍一个基于 FPGA 的软硬结合的算法加速器的诞生。

本系列第一篇力争用简单的语言,在几张 PPT 里回答一个问题:什么是 SM3 杂凑算法?首发知乎

作者:李凡

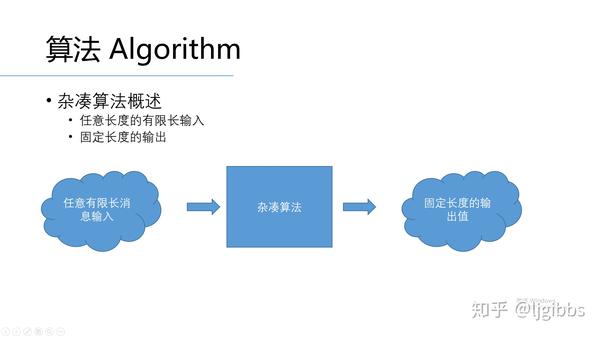

我们首先关注算法的输入输出。

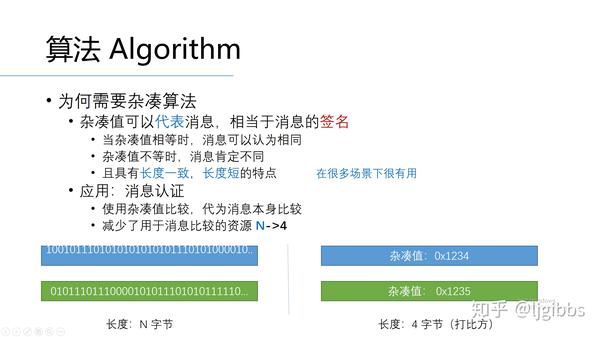

杂凑算法的输入是一组任意长度的消息,消息可以是数字,字符串等等任何二进制数据。长度可以任意,理论上不能超过 2^64 bit 。

输出时一组固定长度的杂凑值,这段杂凑值的长度不会太大,SM3 的杂凑值长度为 256 bit。

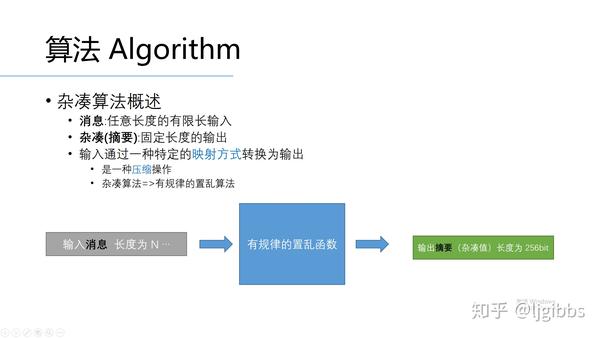

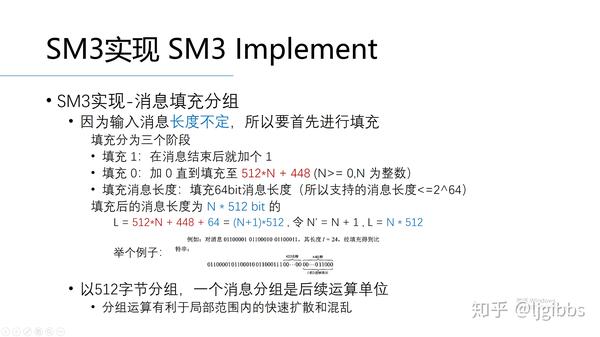

那么输入的消息经历了什么,从长度任意的二进制数据变成了长度特定的杂凑值?

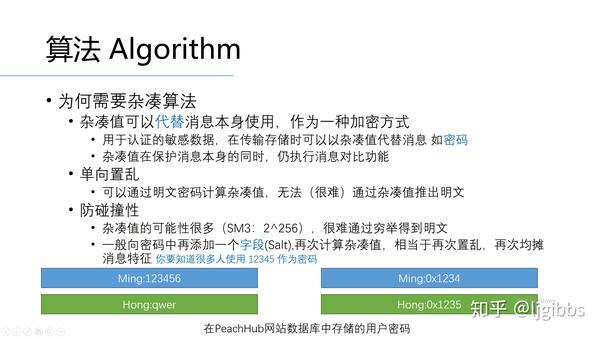

消息通过了一组特定的映射方式,映射的目的首先是进行了压缩,其次也是一种有规律的置乱算法。

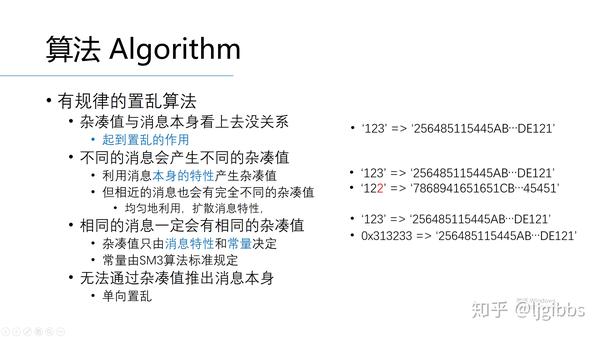

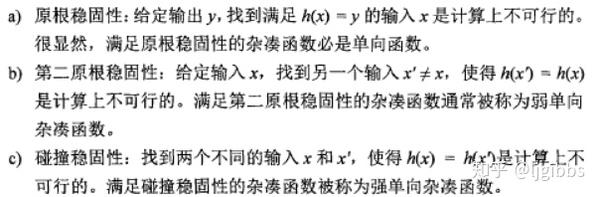

置乱算法有以上特性,从学术一点的角度可以概括为

满足这些特性可以保证其是一个强单向杂凑函数,SM3 满足这些特性

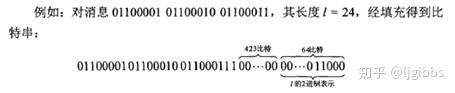

举个例子:

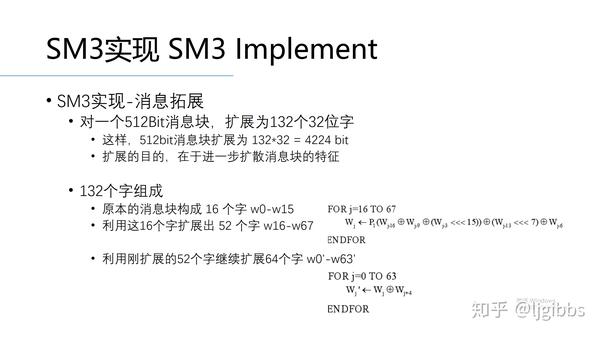

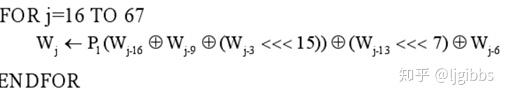

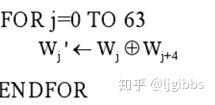

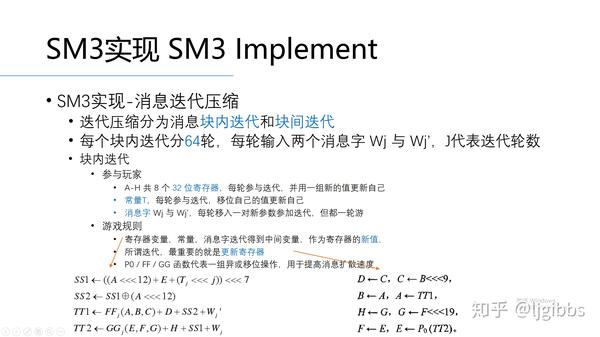

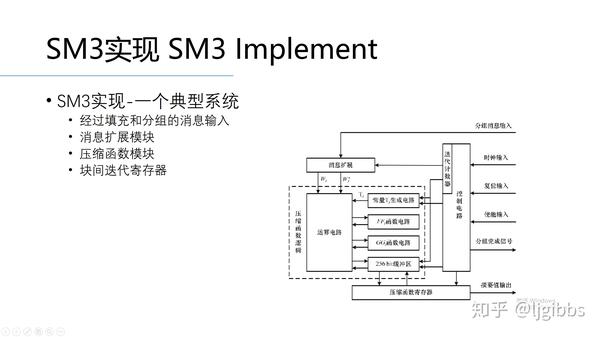

两次扩展的公式

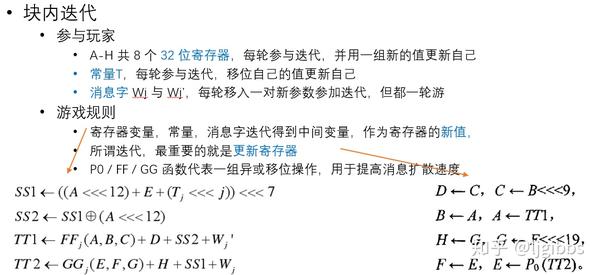

块内迭代

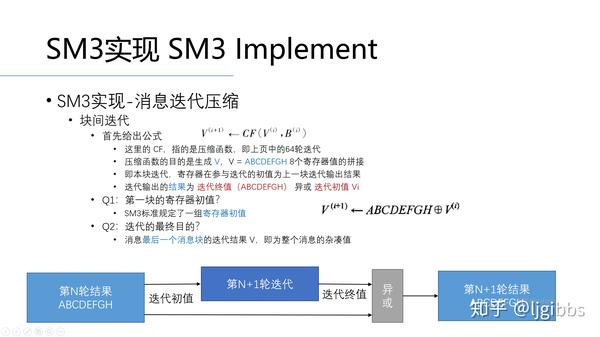

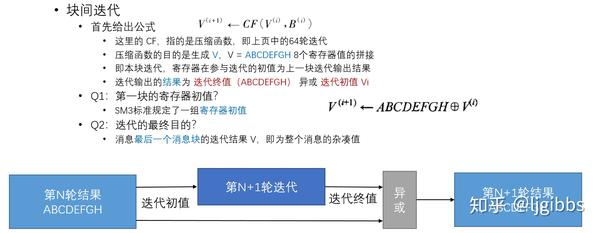

块间迭代

结语

在后续的系列文章中,我们将从软件实现与优化,硬件算法实现,外围通信系统搭建以及软硬协同整体平台几个方向来展开。

软件方面计划以 GitHub 上的开源代码来讲解,其代码兼具可读性,规范性以及性能,既然要硬件加速,肯定要找出最好的软件性能来对比。

硬件逻辑代码将结合学习开源代码以及自行实现。

外部通信系统将基于 UltraScale Zynq 打造一个 10G 以太网平台。

更多FPGA相关知识请关注我的FPGA 的逻辑专栏