目前,许多嵌入式 SoC 的 DDR 规格从 DDR4 升级到 DDR5。本系列设计须知文章是笔者参与一个 DDR5 SoC 项目时,总结的一些 DDR4 升级到 DDR5 的设计要点。

本期我们将讨论 DDR4 的 Gear-down mode (直译:降档) 特性,他是一种提高 DDR 系统兼容性、稳定性的特性

本期我们学习一篇讨论 DDR4 板级设计和信号完整性验证面临的挑战的论文,由来自西门子、富士通以及美光等公司的作者联合完成。

本系列连载于 OpenIC SIG,除了 DDR 学习时间专栏外,OICG 目前正在陆续上线 HDLBits 中文导学的优化版本,欢迎关注/支持/加入我们

本期我们学习一篇关于 DDR IP 硬化(Hardening)的文章,讲述了在 DDR IP 后端实现中的一些建议。笔者在 AI 翻译的基础上对译文进行修正润色,并添加了部分个人见解。

JEDEC 透露其即将推出的针对 DDR5 MRDIMM 内存模块和 LPDDR6 的 CAMM 内存模块标准中的关键细节。

本期我们学习新思的一篇关于 LPDDR4 多通道体系结构优化的白皮书。原文有官方的中文译文版本,本文在此基础上做一些翻译优化(原中文版本不太流畅)和内容调整,并附上少量作者的个人见解,作为原文的导读文章。

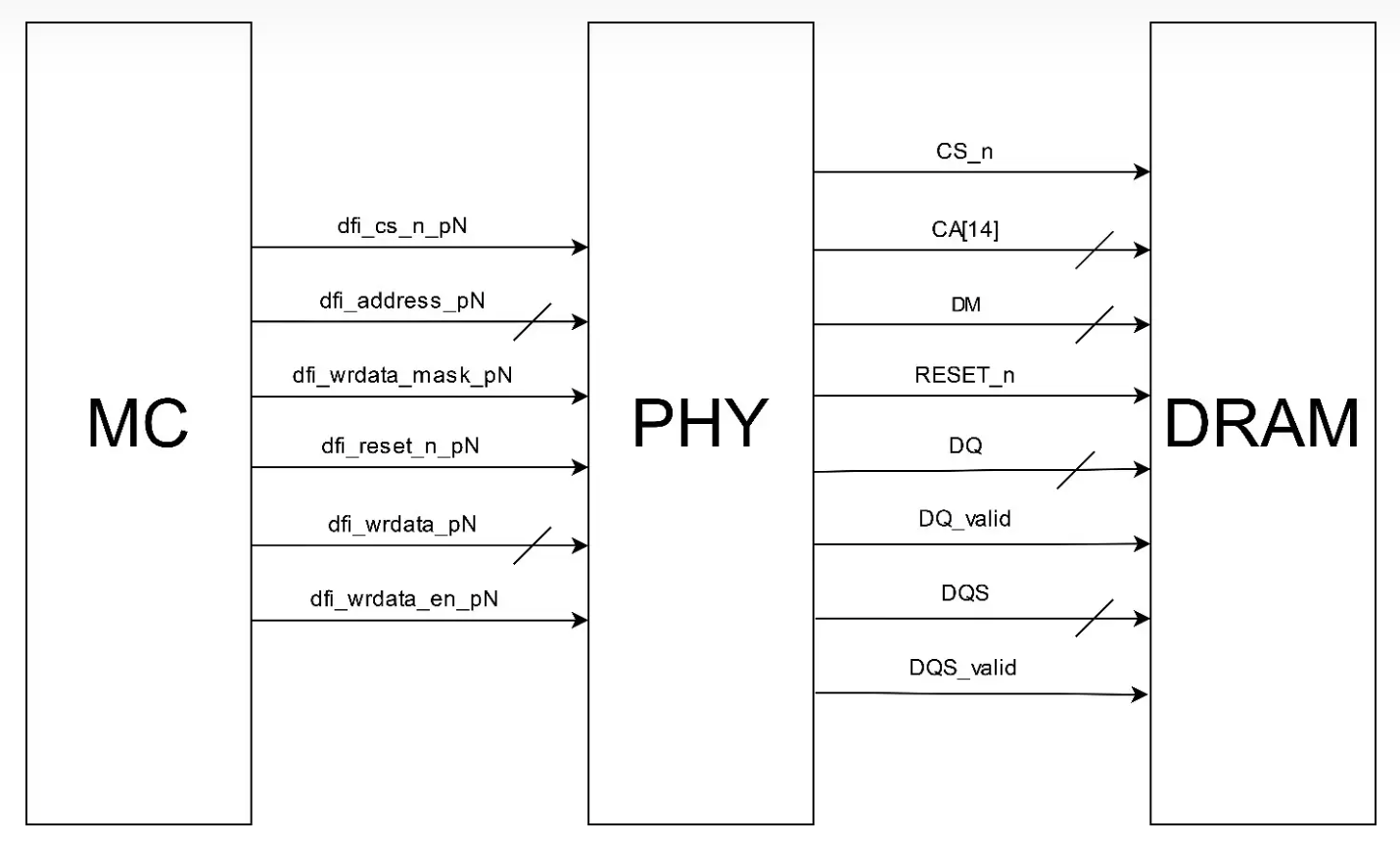

DFI 协议中的写传输(Write Transaction)定义为 MC 通过 DFI 总线向 PHY 写入数据的过程,PHY 随后负责将数据转换为 DRAM 总线形式,发送给 DRAM 颗粒。

我们知道 LPDDR4 相比 DDR4 一项重要的改动是在单个颗粒上支持独立的双通道(Channel),单个通道位宽 16 比特。这样一来,系统可以在 DDR 数据位宽不变的情况下,支持更多的通道,从而提高 DDR 访问效率。

针对芯片设计中 DDR 控制器-PHY 集成相关问题,与芯片 DDR 相关硅前硅后奇怪问题 Debug,开设咨询窗口。如果你有相关问题,或者 debug 中的疑难杂症,可以通过知乎私信咨询/知乎付费咨询。简单、概念类问题免费,如果涉及到细节、具体问题的分析解决,或者协助参与 debug 过程,就是另外的价钱具体再谈。报酬不是重点,...

工程师读上市公司年报,移除宏观叙事与财务细节,关心一些我们打工人关心的内容。注:本文含有 AI 辅助创作(Kimi.ai)

工程师读上市公司年报,移除宏观叙事与财务细节,关心一些我们打工人关心的内容。注:本文含有 AI 辅助创作(Kimi.ai)

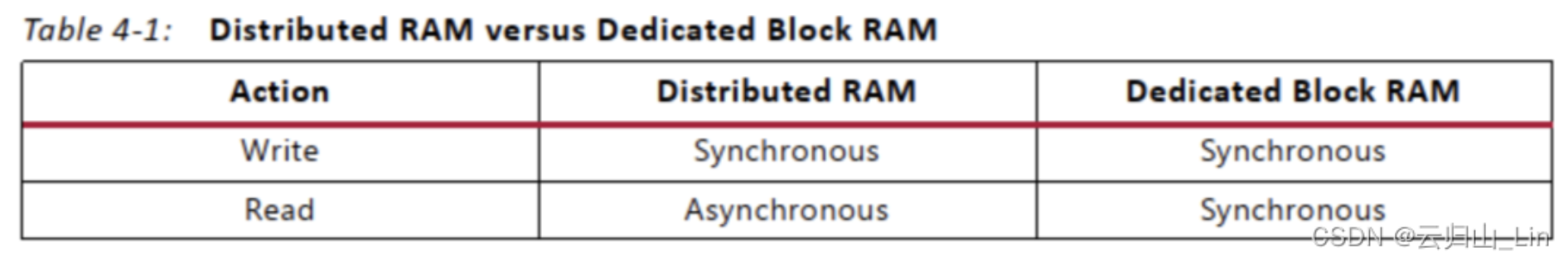

背景手写Multiport RamMultiport RAM 代码方案资源评估Multiport RAM 资源利用的优化资源评估防止读写冲突的组合逻辑设计(写优先)仿真和时序单口写数据单端口读数据多口读相同数据多口同时读不同数据背景在多端口交换机的设计中,交换机的每个端口都会各自维护一张查找表,数据帧进入到交换机后,需要进行查表和转发。...

今天有朋友问我,22nm比28nm面积小多少。我说30%吧。他说,这么小?我说,30%都说多了。注:以下资料来自公开信息,仅做一个与28nm大致的比较。1-22FDX工艺分一下几个flavor。2-与28nm相比,功耗更低,性能更强。还能通过正负偏压来进行功耗和性能的这种,但是采用偏压的话也不是没有成本。要有额外的IP来提供偏压所需的...

如果你是在一个成熟的公司,那么在timing signoff的话,那么可能需要check很多东西。其实很多内容是与工艺以及设计相关的一些特殊的check list。换一种工艺或者设计,或者ip的话,内容也就不同了。那么我们略过这些设计以及工艺相关的东西。对于一个我们不熟悉的设计以及工艺,我们在进行timing signoff的时候,至少需要...

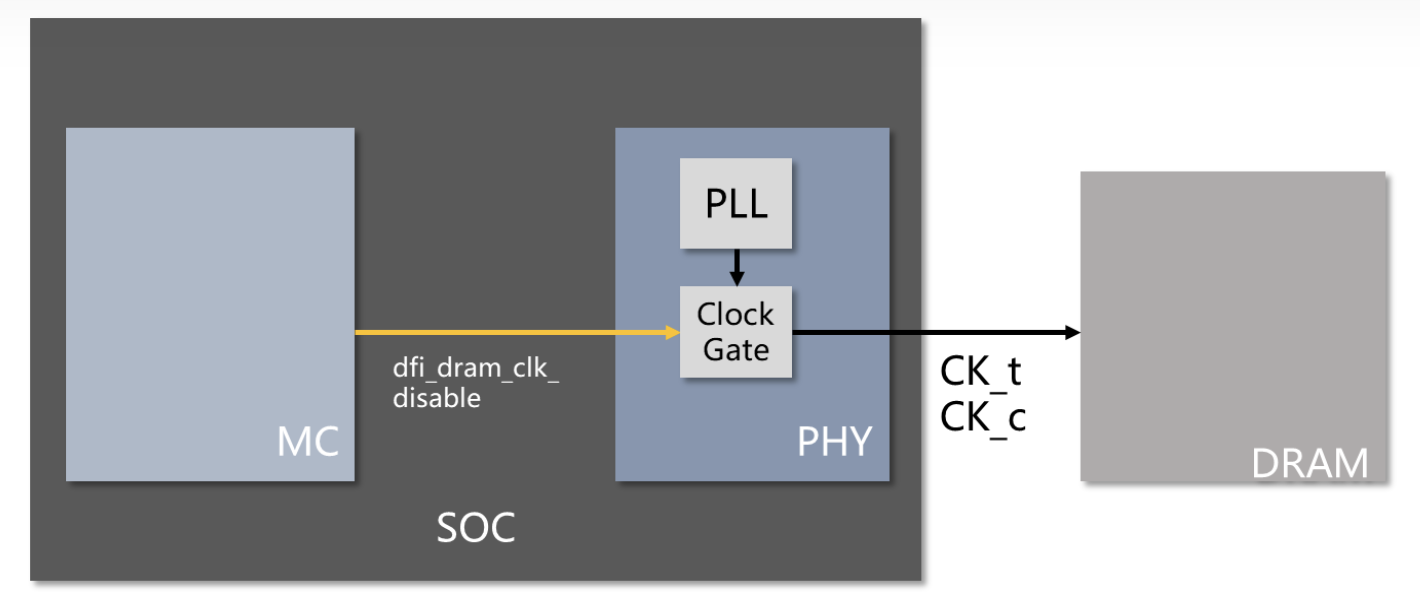

当 DRAM 处于自刷新状态时,系统可以保持提供给 DRAM 的 CK 时钟,或者关闭时钟供给。一般来说,停止 CK 时钟能够进一步降低 DRAM 和系统的功耗,毕竟 CK 时钟是一组高频的差分时钟对(DDR4-3200 为 1.6GHz )。

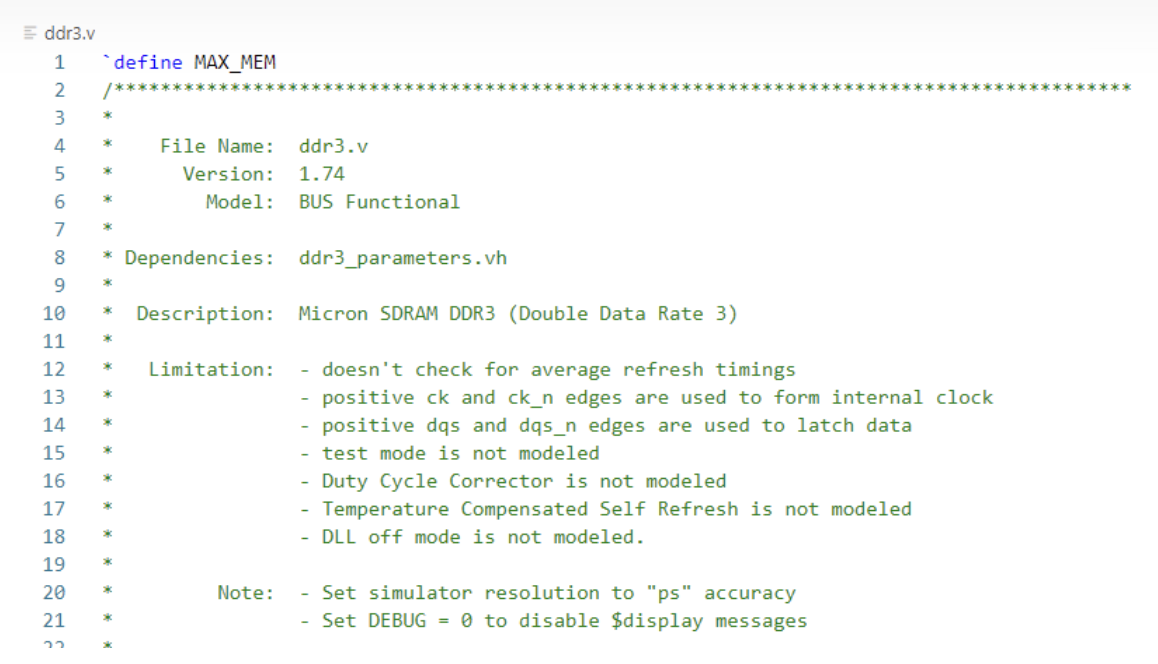

本期以 Micron 的 DDR3 Model 为例,介绍模型如何下载和如何仿真,以及对模型中的各个文件进行解析。

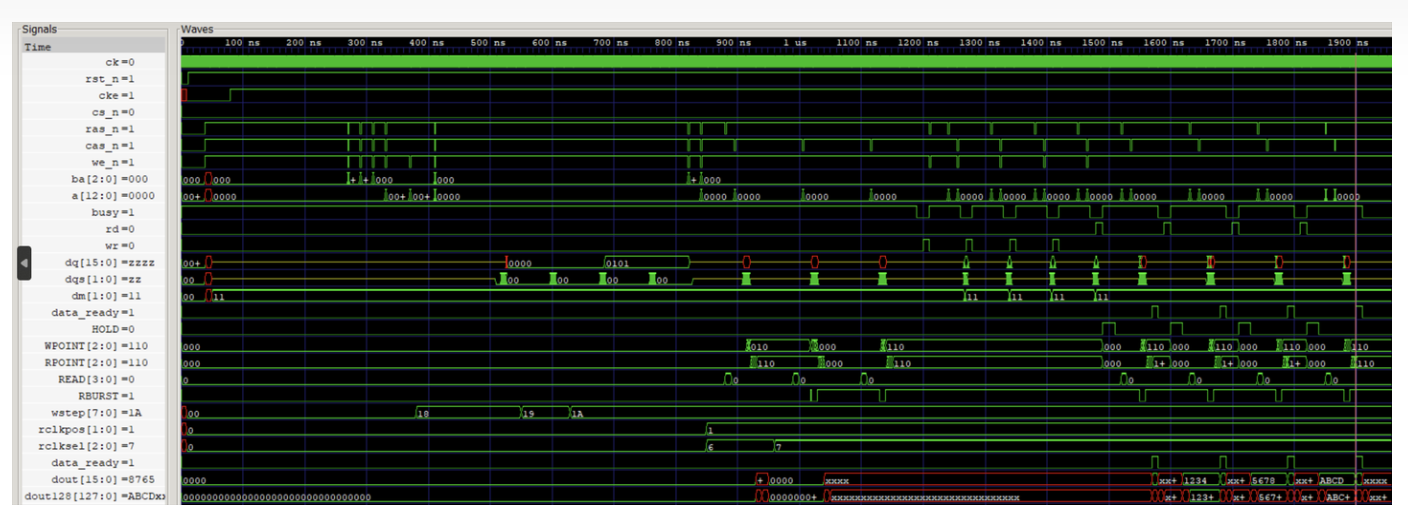

本期写的是一个 Github 上的开源项目,基于 Tang Primer 20K 开发板和高云 GW2A FPGA 的 DDR3 控制器 IP。

本期写的是一个 Github 上的开源项目,实现的是 DDR5 PHY 的数据通路的数字部分,准确地说是 PHY 的写数据通路,看上去是一份埃及开罗 Ain Shams University (ASU) 学生的作业或者毕业设计,由企业进行了赞助(Si-Vision)。

工程师读上市公司年报,移除宏观叙事与财务细节,关心一些我们打工人关心的内容。注:本文含有 AI 辅助创作(Kimi.ai)