【嘉德点评】思瑞浦的此项发明,通过将BOOT参考电压单元的下端连接到第二输出端SW,解决了轻载情况下自举电容CBOOT无法充电问题。思瑞浦的产品不仅满足了通信系统中部分关键芯片的严格要求,而且还应用在5G基站模拟集成产品中。

集微网消息,近日上交所正式受理了思瑞浦科创板上市申请。思瑞浦在模拟芯片领域积累了大量的技术经验,并以此开发了涵盖电源管理领域的多品类模拟芯片产品,而且其中多款产品都已经进入了如中兴、海康威视等龙头企业的供应链体系。

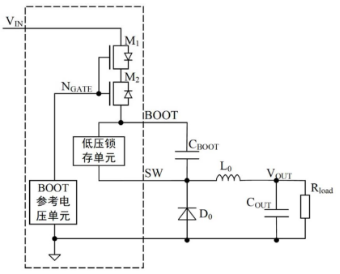

图1 现有技术中基于异步降压DCDC芯片的自举电路

图1为现有技术中基于异步降压DCDC芯片的自举电路,异步降压DCDC芯片需要使用肖特基二级管D0形成电感电流的续流路径,完成输入电压VIN到输出电压VOUT的转换。

异步降压DCDC芯片通常使用NMOS管作为高边的功率管,为了驱动高边NMOS管,需要芯片内部设计BOOT驱动电路,搭配外接自举电容CBOOT,以产生高边NMOS管驱动电路的电源BOOT。如果是在输入电压VIN接近输出电压VOUT、大占空比的工作条件,无论CCM模式(ContinuousConduction Mode,连续导通模式)还是DCM模式(Discontinuous ConductionMode非连续导通模式),OFF时间都很短,自举电容CBOOT无法充分充电。虽然可以用外接二极管和假负载改善,但是这种方法损害了轻载效率。

因此,思瑞浦申请了一项名为“异步降压DCDC芯片及基于异步降压DCDC芯片的自举电路”的发明专利(申请号:201911413532.7)申请人为思瑞浦微电子科技(苏州)股份有限公司。

此专利提供了一种异步降压DCDC芯片及基于异步降压DCDC芯片的自举电路,以解决轻载情况下自举电容无法充电的问题。

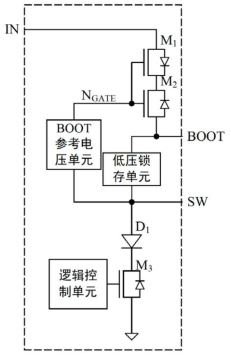

图2 异步降压DCDC芯片的电路原理图

上图是该发明中提出的一种异步降压DCDC芯片的电路原理图,DCDC芯片包括输入端IN、第一输出端BOOT及第二输出端SW,输入端与输入电压VIN相连,第一输出端BOOT和第二输出端SW之间的电压差为VBOOT。其中,输入端IN和第一输出端BOOT之间设有若干个第一MOS管,第一MOS管的栅极与第二输出端SW之间是BOOT参考电压单元。另外第二输出端SW和基准电位之间为第二MOS管M3,且第二MOS管M3通过逻辑控制单元进行驱动。

第一输出端BOOT和第二输出端SW之间设有低压锁存单元,低压锁存单元用于监测第一输出单和第二输出端SW间的电压差VBOOT,以控制第一MOS管的导通或截止。

在第二输出端SW和基准电位之间增加第二MOS管M3,并通过逻辑控制单元进行驱动。当输入端IN和第二输出端SW之间电压差小于或等于预设阈值电压时,逻辑控制单元驱动第二MOS管M3导通,第二输出端SW的电压拉低至基准电位;当输入端IN和第二输出端SW之间电压差大于预设阈值电压时,逻辑控制单元驱动第二MOS管M3截止。

而且在第二输出端SW和第二MOS管M3中间,我们可以放置第一二极管D1,D1的正极与第二输出端SW相连,负极与第二MOS管M3相连。第一二极管D1的设置可以阻断电流的倒灌路径。

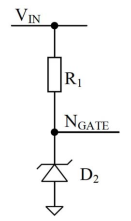

图3 BOOT参考电压具体电路结构示意图

BOOT参考电压单元可以采用如上所示的电路结构,该结构主要包括串联于输入端IN和基准电位之间的第一电阻R1及第二二极管D2,其中,R1和D2之间的电压NGATE为第一高边NMOS管M1和第二高边NMOS管M2的栅极驱动电压。

思瑞浦的此项发明,通过将BOOT参考电压单元的下端连接到第二输出端SW,解决了轻载情况下自举电容CBOOT无法充电问题。思瑞浦公司是少数实现通信系统模拟芯片技术突破的本土企业之一,其产品不仅满足了通信系统中部分关键芯片的严格要求,而且还应用在5G基站模拟集成产品中。

作为国内领先水平的模拟信号链和电源管理芯片供应商,思瑞浦用实力做到了“进口替代”,填补了国内相关技术的空白。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。