【嘉德点评】亚科鸿禹发明的基于FPGA的虚拟IO片间互连电路,通过采用深度可变的第一异步FIFO和第二异步FIFO,从而发送FPGA端电路和接收FPGA端电路可以根据IC设计和异步FIFO读写协议在很大的范围内随意改变第一异步FIFO和第二异步FIFO接口时钟的频率和数据的位宽,不仅大大增大了数据传输的速率和带宽,降低了数据传输的误码率,而且还大大增强了IC设计验证的灵活性!

集微网消息,由中国半导体投资联盟和集微网合办的“芯力量·项目‘云路演’闭门沙龙”IC设计专场中,亚科鸿禹电子带来了其领先中国的IC仿真验证平台!

自1985年推出全球第一款FPGA(现场可编程门阵列)产品以来,FPGA便开始占据IC(集成电路)设计验证的主流,并依赖其特有的优势开始逐渐替代单独的定制芯片。

与此同时,随着微电子行业的急速发展,IC设计验证所需的逻辑资源也在急速增加,单独的FPGA所具有的逻辑资源往往不能满足IC设计验证的需求,这时就需要将2片甚至多片FPGA进行互联来拓展资源,但是由于FPGA片间互联占据过多的接口IO(输入/输出),又严重局限了IC设计验证的发展。

随着serdes(串行器/解串器)接口技术的出现,开始出现了一些采用时分多路复用(TDM)技术的虚拟IO方案。但是由于低频率的标准时钟和固定的数据位宽所造成的低带宽、低速率、高误码率传输,严重局限了该技术方案的应用环境,这给IC设计验证提供的帮助并不是很大。

为了解决这些问题,亚科鸿禹电子在15年6月18日申请了一项名为“一种FPGA虚拟IO片间互连电路”的发明专利(申请号:201510342599.1),申请人为北京亚科鸿禹电子有限公司。

根据目前公开的专利资料,让我们一起来看看这项IC设计验证方案吧。

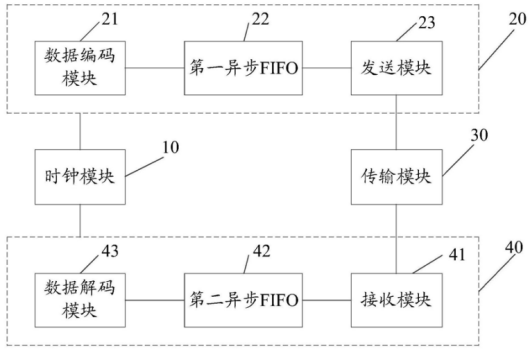

如上图为该专利中FPGA虚拟IO片间互连电路实施例的结构示意图,其中包括时钟模块10、发送FPGA端电路2、传输模块30和接收FPGA端电路40,其中时钟模块用于提供时钟。发送FPGA端电路20与时钟模块相连,发送FPGA端电路包括:数据编码模块21、第一异步FIFO22和发送模块23。

数据编码模块用于对输入的初始数据、数据控制信号以及数据有效信号进行统一编码,并生成编码数据。第一异步FIFO(异步FIFO的写时钟和读时钟可具有不同的频率和相位)用于缓存数据编码模块根据时钟模块提供的编码时钟和异步FIFO写协议写入的编码数据。发送模块用于根据异步FIFO读协议和时钟模块提供的并行时钟从第一异步FIFO读取至少两位数据,以及同时根据并行时钟产生差分串行时钟,并发送至少两位数据和差分串行时钟,直至发送全部编码数据。

传输模块与发送FPGA端电路相连,传输模块用于传输编码数据和差分串行时钟。接收FPGA端电路与传输模块和时钟模块分别相连,接收FPGA端电路包括:接收模块41、第二异步FIFO42和数据解码模块43。

接收模块用于接收至少两位数据和差分串行时钟,直至接收全部编码数据。第二异步FIFO用于缓存接收模块根据异步FIFO写协议和差分串行时钟写入的至少两位数据,直至写入全部编码数据。数据解码模块用于根据异步FIFO读协议和时钟模块提供的解码时钟从第二异步FIFO读取编码数据,并将编码数据同步解码成初始数据、数据控制信号以及数据有效信号。

其中接收模块41包括解串器、IBUFGDS和串并转换模块,串行器和解串器分别包括serdes接口,从而FPGA虚拟IO片间互连电路可以采用serdes的时分多路复用技术的差分传输方法进行数据传输,不仅减少了接口IO数量,而且降低了数据传输的误码率。

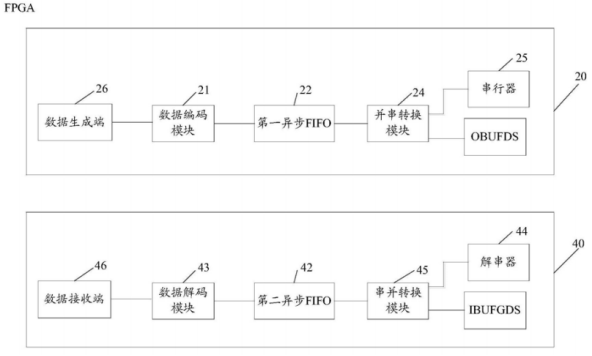

接下来我们再看看这里反复提及的FPGA的结构:

如图所示,FPGA既包括发送FPGA端电路20,又包括接收FPGA端电路40。其中发送FPGA端电路包括数据生成端26、数据编码模块21、第一异步FIFO 22、并串转换模块24、串行器25和OBUFDS,发送FPGA端电路对外发送数据。

接收FPGA端电路40包括解串器44、IBUFGDS、串并转换模块45、第二异步FIFO42、数据解码模块43和数据接收端46,接收FPGA端电路接收外部输入的数据。

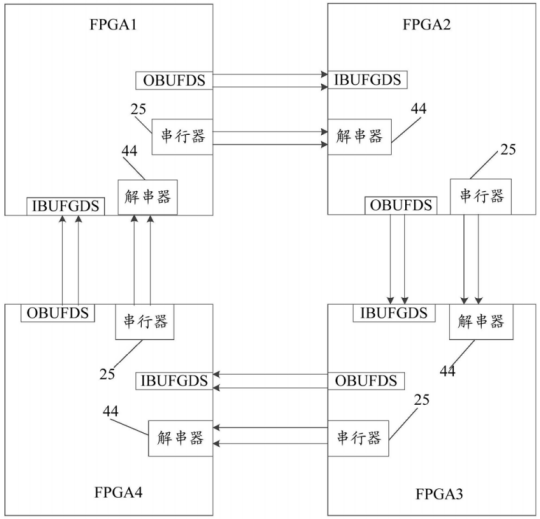

如上图所示,FPGA可以进行虚拟IO片间互连,四个FPGA分别为FPGA1、FPGA2、FPGA3和FPGA4,FPGA1、FPGA2、FPGA3和FPGA4相互连接。

当FPGA1作为发送FPGA端电路时,FPGA1将数据和时钟通过LVDS差分传输通道传送至FPGA2,此时FPGA2为接收FPGA端电路;当FPGA2作为发送FPGA端电路时,将数据和时钟通过LVDS差分传输通道传送至FPGA3,此时FPGA3为接收FPGA端电路。

当FPGA3作为发送FPGA端电路时,将数据和时钟通过LVDS差分传输通道传送至FPGA4,此时FPGA4为接收FPGA端电路;当FPGA4作为发送FPGA端电路时,将数据和时钟通过LVDS差分传输通道传送至FPGA1,此时FPGA1为接收FPGA端电路。

以上就是亚科鸿禹发明的基于FPGA的虚拟IO片间互连电路,通过采用深度可变的第一异步FIFO和第二异步FIFO,从而发送FPGA端电路和接收FPGA端电路可以根据IC设计和异步FIFO读写协议在很大的范围内随意改变第一异步FIFO和第二异步FIFO接口时钟的频率和数据的位宽,不仅大大增大了数据传输的速率和带宽,降低了数据传输的误码率,而且还大大增强了IC设计验证的灵活性!

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)