【嘉德点评】上海瞻芯该项专利中所提供的半导体结构和制备方法,相较于同种器件而言,其电场强度能够大幅降低,提高了半导体器件栅氧化层的可靠性。同时栅漏之间的电容也被大幅降低,从而极大的减少了开关功率的损耗。

集微网消息,近几年,国内的碳化硅市场增速非常快,越来越多的企业开始使用碳化硅器件来替代传统硅器件方案,上海瞻芯就是其中之一。上海瞻芯是一家由海归博士领衔的碳化硅高科技芯片初创公司,致力于开发以碳化硅器件为核心的高性价比功率芯片和模块产品。

传统的平面型碳化硅金属氧化物半导体场效应晶体管(Planar SiC MOSFET,例如垂直双扩散金属氧化物晶体管VDMOS)由于器件尺寸较大,影响了器件的特征导通电阻,这会增加开关损耗,导致器件性能较差,并且,传统的平面型碳化硅器件成本较高,不利于推广利用。

为了解决上述问题,上海瞻芯申请了一项名为“半导体器件结构及其形成方法”的发明专利(申请号:201911217030 .7),申请人为上海瞻芯电子科技有限公司。

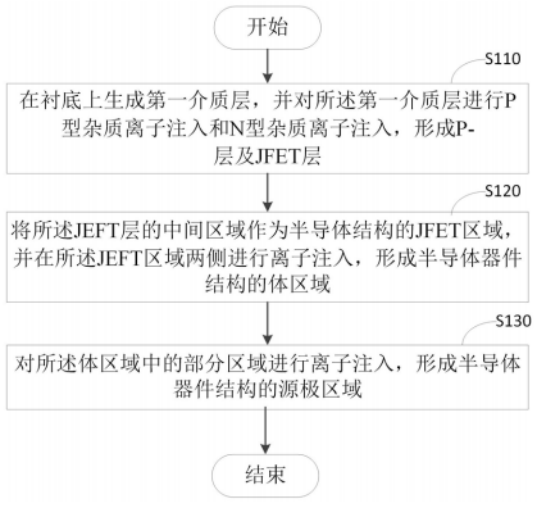

图1 半导体器件结构形成流程图

图1示是此专利提出的一种半导体器件结构形成方法的流程图,通过以上流程可以在衬底上生成第一介质层,并对第一介质层进行P型杂质离子注入和N型杂质离子注入,进而形成P-层及JFET层。然后将JEFT层的中间区域作为半导体器件结构的JFET区域,在JEFT区域两侧进行离子注入,形成半导体器件结构的体区域。接着再对该区域中的部分范围内进行离子注入,这样就会得到半导体器件结构的源极区域。

通过在半导体器件结构设置JFET区域,可以降低半导体器件的特征导通电阻,从而增加导通速度并减少开关功率损耗。而且我们在JFET区域上设置P-区域之后,还可以提高器件的栅氧化可靠性,有效降低器件的栅漏电容,同时又能进一步降低开关功率损耗。

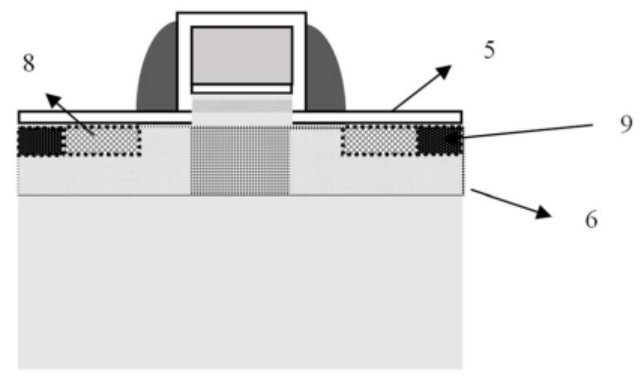

图2 半导体器件结构的工艺流程示意图

上图是本专利提出的半导体器件结构的工艺流程的示意图。我们可以从图中看到,在凸起的表面会生成保护层5,并通过保护层5对未被凸起部覆盖的JFET层进行离子注入,进而能得到体区域6。

源极区域的P+区域9与N+区域8相邻,在注入N型离子时,可以通过第三介质层中未被墙覆盖的区域(即N+区域8上方的区域)进行N型离子注入,以形成源极区域的N+区域8。在形成源极区域的N+区域8后,又能对相邻(靠外)一侧(与注入N型离子的区域不重叠,即P+区域9上方的区域)进行P型离子注入,进而形成源极区域的P+区域9。

采用上海瞻芯此专利中的方法得到的半导体器件,相较于同种器件而言,其电场强度能够大幅降低,提高了半导体器件栅氧化层的可靠性。同时栅漏之间的电容也被大幅降低,从而极大的减少了开关功率的损耗。

在过去的一年中,全国半导体总投资达到700多亿元,其中SiC材料相关项目涉及65亿。国内SiC产业阵容不断扩大,无论是衬底、外延,还是器件和模组,国内都涌现了一批如上海瞻芯一样的优秀企业。希望在不久将来,能够将产业链扩展到全球,争取在全球市场占有一席之地。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)