本系列中我们将一起探寻 Xilinx FPGA 的硬件开发环境 Vivado,发现 Vivado 的 Design Flow,使用 Tips...或许再来一些 BUG?Happy Design in Vivado!

- 注:我好像不怎么想去翻 UG xxx 来写这系列文章 -\_- ,有错欢迎大家翻着 UG 指出。

- 注2:如无意外,本系列将持续使用 2018.3

- *

当你完成了一个设计之后,查看原理图,可以了解工具如何将你的代码转换成了电路。方便你铆足了劲死磕一个小小的加法器来优化 200ps 的关键路径。

当你要查看一个开源设计,查看原理图,可以快速掌握项目设计的架构图。方便你用轮子或者,恩,造个更好的。

那么如何在 Vivado 中查看原理图?

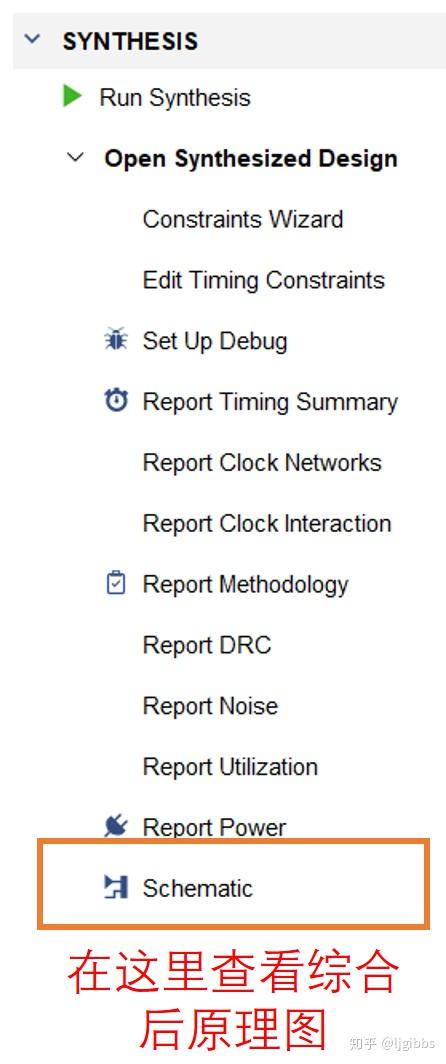

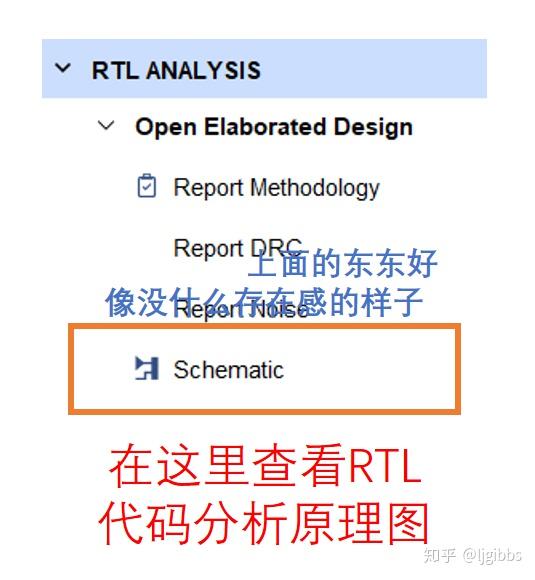

答案是通过 Vivado 左侧的 Flow 栏。

在 Flow 栏中可以查看综合或者布局布线后的原理图。

也可以在完成 RTL 编码后查看 RTL 分析 (RTL ANALYSIS) 的原理图。

在综合后的原理图中电路已经被映射到器件的 LUT 和 FF 中,并且经过了综合器的优化。相比原先的代码,可以说"面目全非”了。

这种情况下,不适合想要看看自己的跑马灯有几个模块组成的愉悦心情。适合那些想要对着加法器,逻辑门拼命优化的朋友,他们总觉得综合器没能很好领会自己的代码精神,要视察下工作 -,- \`\`。

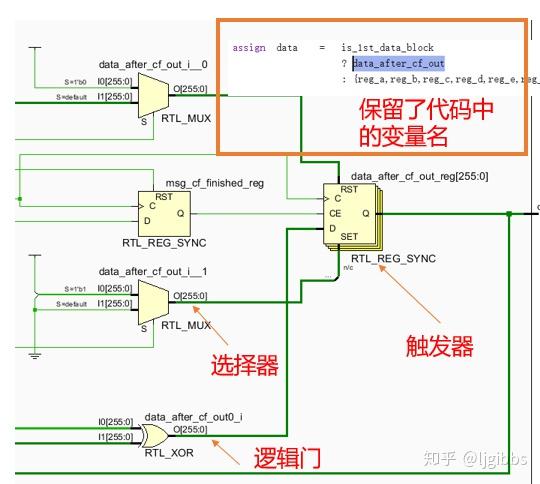

而 RTL 分析的原理图用逻辑门,选择器以及触发器来表示电路,并尽量使用代码中的变量名表示,可以更清晰地和代码对应。

这样一来,就知道自己的代码会变成怎样的电路器件,与门,非门,选择器,加法器等等。尽管我保证他们哪个在 FPGA 上都不存在。

不过,我们可以将他们映射到 LUT 上实现—— 一种 FPGA 上有的是的东西。

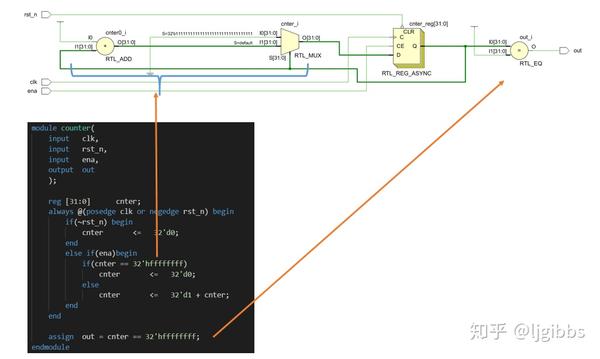

举个例子

一个计数器的电路就跃然纸上了,其实计数器和 CPU 都是一样的(真的)。

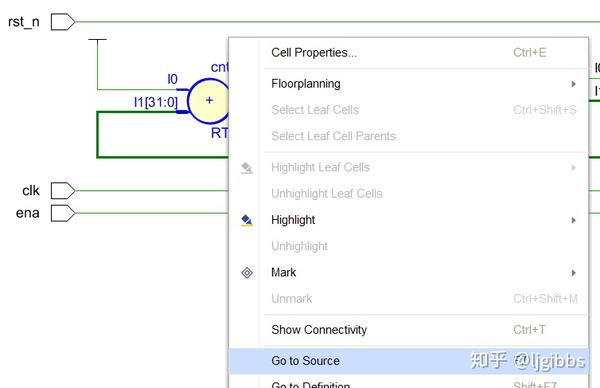

右键某个元件,在菜单中选择 Go to Source, 可以跳转到你代码中的相应部分。

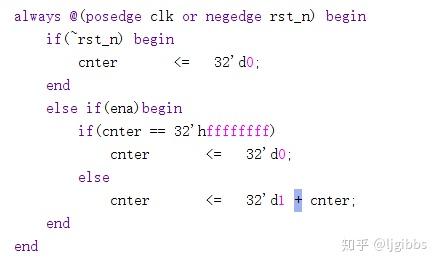

比如这个加法器,就跳转到了代码中的那个加号。

我向你保证,在你综合之后“面目全非”的代码里,跳转到代码可不是那么容易的。

Happy Design in Vivado!

关于 Vivado 你有什么想了解的?我会的话,就会写成下一期文章。

我不会的话,可以学,可以摸索下。

实在不行的话,我就只能去翻 UG xxx 了。Vivado User Reference 之类的东东吧。