对于ARM的处理器,中断给处理器提供了触觉,使处理器能够感知到外界的变化,从而实时的处理。本系列博文,是以ARM cortex-A系列处理器,来介绍ARM的soc中,中断的处理。

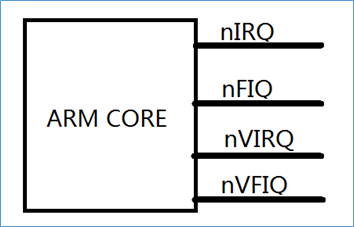

ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递。分别是:

◾nIRQ: 物理普通中断

◾nFIQ: 物理快速中断

◾nVIRQ: 虚拟普通中断

◾nVFIQ: 虚拟快速中断

如下图所示:

其中虚拟中断,是为了实现虚拟化而加入的,在这个系列中,不讨论虚拟中断,只介绍物理中断的相关知识。

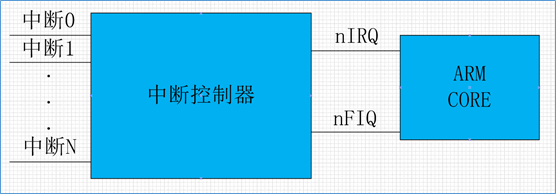

在arm的soc系统中,会有多个外设,均有可能会产生中断发送给arm cpu,等待cpu处理。

而arm cpu对中断,只提供了2根信号,一个nIRQ,一个是nFIQ。因此就需要有一个中断控制器来作为中间的桥接,收集soc的所有中断信号,然后仲裁选择合适的中断,再发送给CPU,等待CPU处理。如下图所示:

这中间的桥接器件,就是arm公司推出大名鼎鼎的gic,general interrupt controller。

gic其实是一个架构,版本历经了gicv1(已弃用),gicv2,gicv3,gicv4。对于不同的gic版本,arm公司设计了对应的gic IP。

◾gic400,支持gicv2架构版本。

◾gic500,支持gicv3架构版本。

◾gic600,支持gicv3架构版本。

gic的核心功能,就是对soc中外设的中断源的管理,并且提供给软件,配置以及控制这些中断源。

当对应的中断源有效时,gic根据该中断源的配置,决定是否将该中断信号,发送给CPU。如果有多个中断源有效,那么gic还会进行仲裁,选择最高优先级中断,发送给CPU。

当CPU接受到gic发送的中断,通过读取gic的寄存器,就可以知道,中断的来源来自于哪里,从而可以做相应的处理。

当CPU处理完中断之后,会告诉gic,其实就是访问gic的寄存器,该中断处理完毕。gic接受到该信息后,就将该中断源取消,避免又重新发送该中断给cpu以及允许中断抢占。

之后,会先介绍下gicv2的相关知识,然后介绍目前主流使用的gicv3。

系列其他篇

原文首发于骏的世界博客

作者:卢骏.

更多Arm技术相关的文章请关注Arm技术博客极术专栏,每日更新。