集微网消息,物联网的万亿级别市场正在逐步形成,超万亿级的设备和节点将通过物联网技术实现万物互联和万物智联。但是受限于体积、重量和成本等因素,物联网节点需要在微型电池或能量收集技术进行供电的情况下,能够持续工作数年乃至十年以上,这对芯片提出了苛刻的低功耗要求。

在低功耗、电池供电的物联网设备正处于爆发性增长态势的背景下,如何才能真正满足物联网设备的低功耗、低成本需求呢?为此,2020年5月27日(周三)上午10:00,集微网邀请芯原微电子(上海)股份有限公司副总裁汪洋做客第九期“开讲”,带来以《超低功耗物联网连接方案与先进半导体工艺技术的结合》为主题的精彩演讲。截至5月28日中午12:00,已有11488名观众通过爱集微APP直播平台观看了该节目。

芯原微电子(上海)股份有限公司副总裁汪洋

适用于物联网市场FD-SOI 22nm工艺

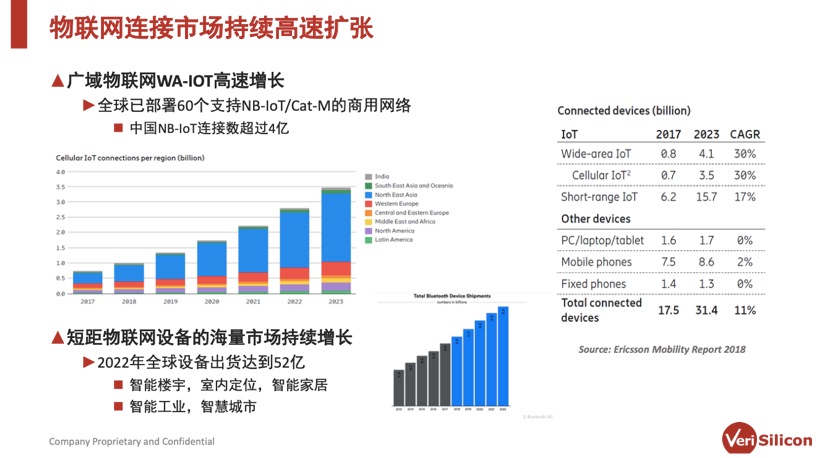

在汪洋看来,如今的物联网连接市场正持续高速扩张。物联网主要分为广域物联网和短距物联网,其中广域物联网主要包括NB-IoT和Cat-M,目前全球已部署60个支持NB-IoT/Cat-M的商用网络;而短距物联网包括WiFi、蓝牙BLE和LoRa等等,主要应用于智能楼宇、室内定位、智能家居、智能工业、智慧城市等海量市场,该市场正呈现持续增长趋势,预计2022年全球设备出货达到52亿。

“对于芯原而言,将主要选择以NB-IoT和蓝牙BLE为代表的IoT连接技术,并会根据5G场景下的不同应用进行持续演进。”汪洋说道。

实际上不管是广域物联网,还是短距物联网,对于IoT设备系统平台的需求都是相似的。其中基于IP的硬件平台,可以结合工艺的特点来满足其完整性和可靠性,而面向应用场景的软件平台则需要满足可扩展和场景化的需求。

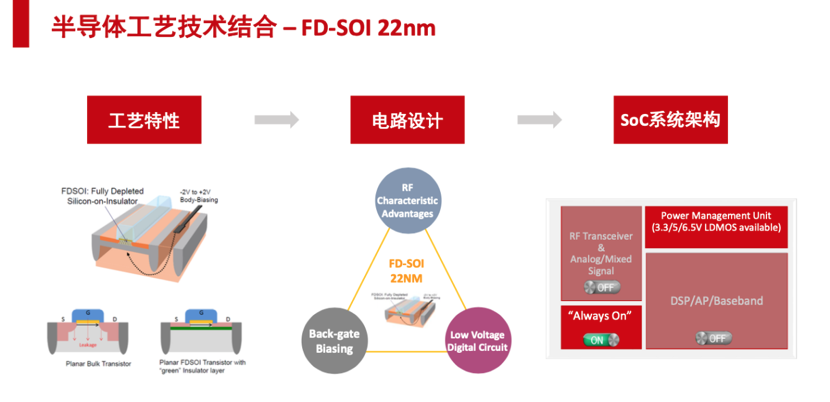

汪洋指出,基于IP的硬件平台需要与半导体工艺技术结合。“随着半导体工艺技术节点不断向前演进,对漏电控制的要求会越来越高,经过芯原的比较和选择,认为FD-SOI 22纳米是最合适的工艺技术。”

为什么FD-SOI工艺适用于物联网市场呢?这主要归功于它的三个特点:一是低功耗,FD-SOI独有的体偏压(body bias)可通过用软件控制体偏压在功耗、性能和漏电功耗之间实现动态平衡;二是FD-SOI更容易集成RF工艺,FD-SOI可以为射频设计提供超优的RF特性,可以支持更高的射频频段,包括毫米波频段,射频电路匹配性能更好;三是FD-SOI能够支持物联网超低电压芯片的实现。

汪洋表示,“将采用FD-SOI 22纳米工艺的芯原IP集成到SoC中,可以满足物联网设备对于低成本、低功耗、高集成度的三个需求。”

经过芯原的多方面测试,FD-SOI 22纳米工艺的射频优势主要体现在5个方面:一是高电流效率Gm/I,支撑低噪声高增益的射频电路设计;二是更优的器件匹配度可帮助减少电路面积;三是更低的漏/源极寄生效应;四是通过back-gate biasing可灵活调整MOS管阈值电压,支持更多射频电路新结构;五是通过控制back-gate 电压可简化实现射频电路校准和微调。

芯原的多种IP产品

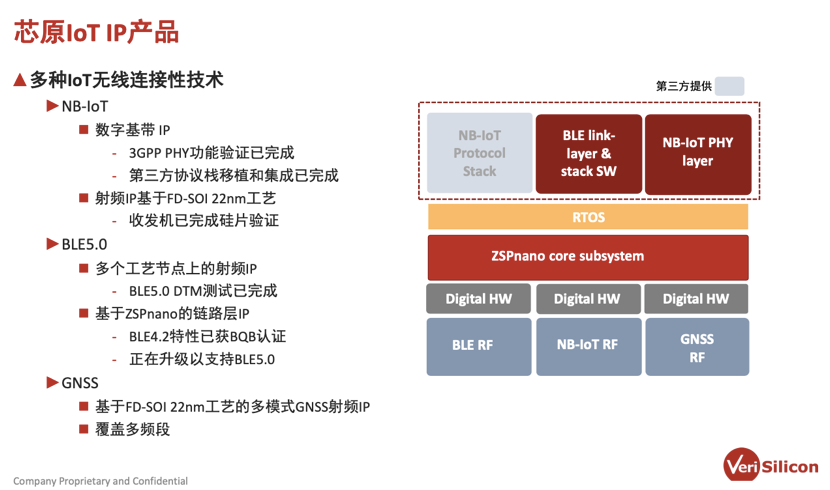

从芯原的布局来看,其拥有多种IoT无线连接性技术,IP产品主要包括NB-IoT数字基带IP和射频IP、蓝牙BLE5.0射频IP和基于ZSPnano的链路层IP、多模式GNSS射频IP。

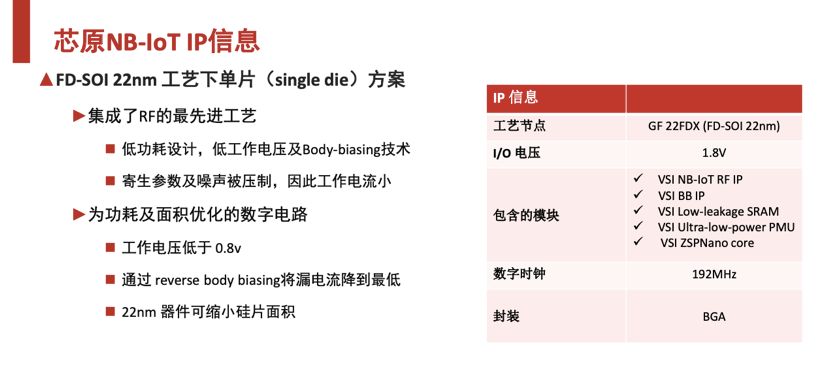

芯原NB-IoT IP

据汪洋介绍,在NB-IoT技术方面,芯原可以提供包括RF、收发器、基带、处理器和电源管理组件的高效单芯片集成。

芯原NB-IoT IP是FD-SOI 22纳米工艺下的单片方案,其集成了RF的最先进工艺,不仅采用低功耗设计,低工作电压及Body-biasing技术,同时由于寄生参数及噪声被压制,因此工作电流很小;此外其拥有为功耗及面积优化的数字电路,不仅工作电压低于0.8v,同时通过reverse body biasing将漏电流降到最低,22nm器件可缩小硅片面积。

值得一提的是,基于FD-SOI 22纳米工艺上的芯原NB-IoT射频IP是一个完整收发机,其拥有的几大亮点包括:无电感高增益 LNA、低 IF/zero IF 可配置 RX 架构、用于校准的TRX loopback、支持26MHz DCXO/VCTCXO和集成PMU。

而芯原NB-IoT 数字基带处理IP是基于ZSPnano core的单核基带处理,ZSPnano集MCU和DSP功能及特性于一身,其拥有低功耗、低成本的内核架构,以及全系统集成和验证。

从芯原NB-IoT 基带测试报告来看,在标准符合性测试方面,不仅使用第三方协议栈软件通过了PHY功能的系统测试,同时通过了R&S CMW500 测试仪的信令测试;此外在功耗测试方面,不仅内核电压可低至 0.65v,同时通过body-biasing技术将漏电流降至了最低。

芯原蓝牙BLE IP

据汪洋介绍,在蓝牙BLE技术方面,芯原BLE系统平台是可集成到SoC的完整蓝牙BLE系统解决方案。芯原BLE RF经多个测试芯片验证,多次迭代,可支持SMIC55和GF 22FDX FD-SOI 22nm工艺节点。此外,芯原BLE系统平台已通过BQB认证,具备高可靠性。

芯原BLE射频 IP具备高性能射频设计和低功耗优化,可以满足高集成度、高性能、低功耗、低成本这四大优势。在芯原BLE5.0 射频测试报告中,所有参数均符合BT5.0协议规范。

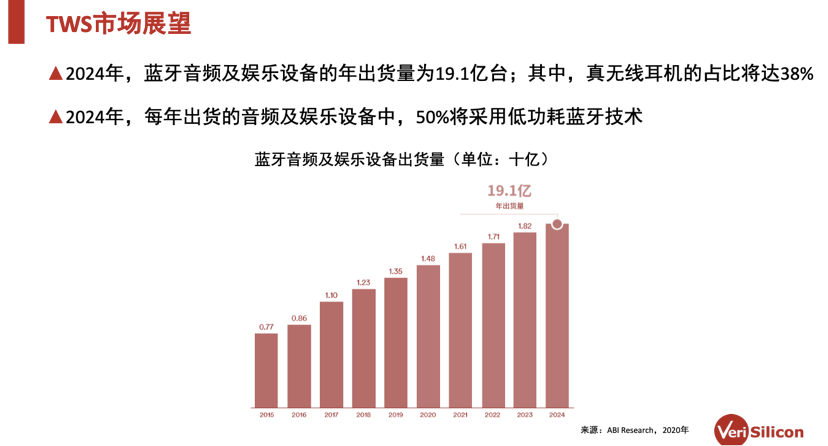

提到蓝牙,不得不提其最大的应用市场耳机。从有线耳机到无线耳机,再到真无线耳机(TWS),其市场发展也是日新月异。据调研机构数据显示,2024年,蓝牙音频及娱乐设备的年出货量为19.1亿台,其中,真无线耳机的占比将达38%;2024年,每年出货的音频及娱乐设备中,50%将采用低功耗蓝牙技术。

毫无疑问,TWS耳机占据着耳机市场中巨大的市场份额。汪洋认为,下一代 TWS 主芯片除了具备可靠连接、超低功耗、高音质的特点,还将具备主动降噪,AI辅助降噪,以及语音控制,智能控制的特点。

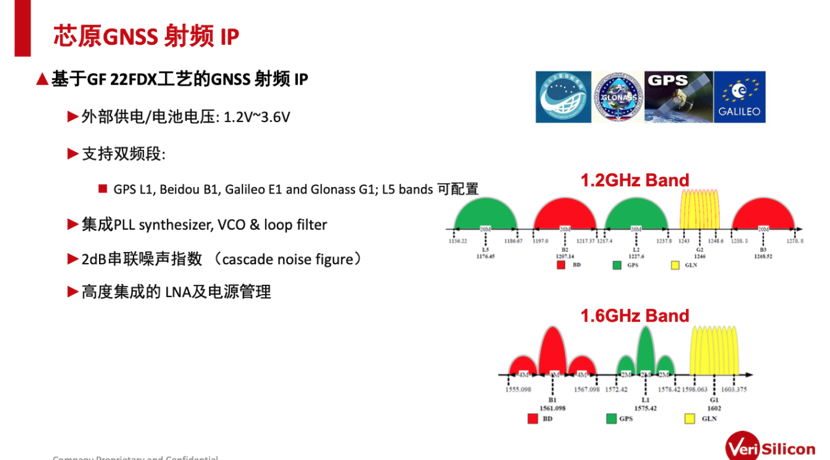

芯原GNSS射频IP

据汪洋介绍,基于GF 22FDX工艺的芯原 GNSS 射频 IP,其外部供电/电池电压为1.2V~3.6V,支持GPS L1、北斗B1、伽利略E1 和格洛纳斯 G1双频段,集成了PLL synthesizer, VCO & loop filter,同时拥有2dB串联噪声指数,以及高度集成的LNA及电源管理。

芯原GNSS 射频测试芯片是独立的射频芯片以供 IP 验证,其拥有完整的 Rx 通路,数字信号输出至基带处理,同时集成了集成 32K 振荡器及 LDOs。芯原GNSS 射频测试芯片可供 IP 评估,已经与基带方案合作方一起通过集成测试,测试结果显示 CN0 良好: ~40dB。

芯原的全球化布局

芯原成立于2001年,全球设有5个设计研发中心和10个销售与客户支持办事处。目前在全球有900多位员工,其中80%的员工在上海和成都,80%的员工专职从事研发。2018年12月,芯原集团完成了拆红筹重组,芯原上海已于2019年9月向上交所递交科创板IPO申请,目前已成功过会。

汪洋表示,芯原拥有独有的业务模式:芯片设计平台即服务(SiPaaS)。SiPaaS 模式具体是指基于芯原自主半导体 IP 所搭建的技术平台,为客户提供一站式芯片定制服务和半导体 IP 授权的一种商业模式。正如20年前台积电引领了芯片设计公司从“有制造”(IDM)到“无制造”(Fabless)的转变,芯原致力于帮助芯片设计公司从“重设计”到“轻设计”的转变。

坚持只做服务,不做产品,不与任何一家晶圆代工厂捆绑在一起,有着清晰定位的芯原正在正确的轨道上前进着。通过多年的自主研发及并购积累,芯原不仅可以提供世界一流的系统级芯片(SoC)和系统级封装(SiP)一站式解决方案,同时针对消费电子、汽车电子、计算机及周边、工业、数据处理、物联网等领域建立起自己的IP护城河,成功发展成为一流的“IP Power House”。

根据 IPnest 统计,芯原2019年度半导体IP销售收入在中国大陆排名第一、全球排名第七。芯原IP种类的齐备程度在全球半导体 IP 授权供应商中也具有较强竞争力。芯原至今已拥有高清视频、高清音频及语音、车载娱乐系统处理器、视频监控、物联网连接、数据中心等多种一站式芯片定制解决方案,以及自主可控的GPU IP、NPU IP、VPU IP、DSP IP 和ISP IP 五类处理器IP以及1,400多个数模混合 IP 和射频 IP。

汪洋最后强调,未来拥有多样化客户基础的芯原必将更好地应对日益增长的市场。

互动问答

Q:现在都在讲AIoT,但是很多IoT设备需要能够在路上,天空中,工厂内或海上平台上运行。这些位置的共同点是通常对电子设备不太有利的环境。怎么看物联网数据传输这块的环境困扰?

A:物联网连接技术主要包括广域物联网和短距物联网。其中功耗是核心的指标,不同场景下对于电源都有很高的要求,因此我们在设计物联网连接技术时,也对半导体工艺技术进行了考量。随着半导体工艺制程越往前演进,FD SOI工艺可以在不增加成本的同时,在功耗、性能和漏电功耗之间实现动态平衡,从而改善物联网芯片的待机功耗和电压功耗。

Q:BLE已经不少客户在往28nm演进,随着功耗要求越来越高,也有不少物联网传输芯片往先进制程迈进,大家对于制程的关注和演进会不会形成类似很多消费电子芯片那样的制程PK?

A:物联网芯片除了对功耗有特殊的要求以外,成本也很重要。不同的物联网连接技术对应不同的物联网设备,终端设备的成本肯定是越低越好,所以主芯片的成本尤为重要。随着半导体工艺制程不断往前演进至14nm、7nm、5nm,性能会很好,但是有两大挑战,一是技术漏电,二是成本。我认为对于物联网设备而言,对工艺节点的追赶没有像手机那样紧,需要综合考虑功耗和成本。

Q:今天我们讨论的是物联网连接IP,最近“万物智联”的概念很火,在“智联”方面,芯原可以为产业界提供些什么样的技术?

A:之前我讲的都是连接性技术,即怎么把数据从端传到后台,这是连接。连接带来了数据以及对连接的智能处理,从而引申出一个概念“万物智联”。在智联里面,智慧怎么体现呢?因此我们会加上AI技术,将实现本地化智能处理的芯原NPU技术集成到系统中。但是在通过AI技术实现智联的形势下,怎么才能不显著增加功耗和成本呢?这就需要做一些IP层面的集成,而芯原也一直在此领域布局。目前芯原大概有30多个AI客户,50几款芯片落地。

Q:芯原的IP营收目前中国排名第一,全球第七。芯原哪些IP是在业界具有领先优势的?

A:芯原IP产品有上千种,除了物联网连接技术IP,还有处理器IP。在一个完整的 SoC里面,除了CPU以外,还需要图像的处理、视频的处理、编解码、语音的处理、数据压缩、显示等等,这些模块在数字处理流程中也是不可或缺的,因此芯原除了模拟和RF以外,在其他关键处理器IP上也做了很多的工作。无论是GPU、视频转码方案、汽车中控、汽车仪表盘、桌面PC的显卡、智能家居AI处理等等,芯原其实都有技术提供,而这些技术都是芯原经过十几年的积累所得。

Q:ARM是目前低功耗蓝牙SoC的主流架构,RISC-V目前也在蓬勃发展,芯原也是RISC-V的核心会员,怎么看RISC-V的发展前景?芯原在这块有一些自己的打算吗?

A:RISC-V是一个很有发展前景的方向。在芯原的IP布局中可以看到,芯原没有CPU IP,因此在CPU方面芯原会跟整个产业合作,不管是传统CPU厂商,还是新兴的RISC-V厂商,芯原都是采取开放的心态。RISC-V对于物联网技术来说,也是很好的契合点,不光是商业模式,它的成本和功耗优势对于物联网设备供应商来说也是不错的选择,所以芯原会选择与全球众多的RISC-V厂商合作。

Q:物联网,对于网络传输制式,速度,功耗,距离等各不相同,比较碎片化,这对我们这样做IP的厂商而言会带来哪些困难或者挑战?

A:从IP角度来看,把连接技术做到极致就是挑战,在物联网连接技术上的每一个分支,不管是NB-IoT、蓝牙还是LoRa,做到极致就必须使得数字电路设计够小够稳,同时也要追求可靠性和完整性,因此里面的每一种模式包括芯片和IP都要打磨得很精致。芯原在做每一个RF 设计的时候,都要进行芯片的测试、迭代、调整,所以通过和FD SOI半导体工艺技术的结合,可以满足物联网连接技术所需的极致要求。

Q:从IP到芯片级解决方案,芯原可以再讲一下服务内容以及特点吗?

A:SiPaaS(Silicon Platform as a Service)模式具体是指基于芯原自主半导体 IP 所搭建的技术平台,为客户提供一站式芯片定制服务和半导体 IP 授权的一种商业模式。为包含移动互联设备、数据中心、物联网(IoT)、智能物联网(AIoT)、汽车、工业和医疗电子在内的广泛终端市场提供行业领先的、全面的系统级芯片(SoC)和系统级封装(SiP)解决方案。芯原的机器学习和人工智能技术已经全面布局智慧设备的未来发展。基于SiPaaS服务理念,芯原助力客户在设计和研发阶段领先一步,从而专注于差异化等核心竞争优势。芯原的一站式端到端的解决方案则能够在短时间内打造出从定义到测试封装完成的半导体产品。

(校对/kaka)