【嘉德点评】武汉新芯公司关于NOR Flash存储结构和擦除方法的专利内容介绍,相比于顺序执行,流水线形式的并行擦除方法可以显著提高擦除效率,从而进一步提高其闪存产品的竞争力。

集微网消息,在全球NOR Flash存储芯片领域,武汉新芯公司频频突破技术壁垒,此前公司在50nm闪存技术上取得突破,达到国际先进水平。而最近武汉新芯在NOR Flash的存储结构和擦除方法上,又带来了一个新的“惊喜”。

在半导体器件领域,闪存以其工作速度快、数据可靠的特性可大量替代其他存储器嵌入到电路中。相对于NAND结构,NOR结构的非易失性闪存凭借单元面积小且读写时间短的优势可在市场中得到大规模应用。

目前主流的NOR Flash主要基于浮栅闪存技术,存储区域在逻辑上分成多个存储块。擦除操作闪存读写之外的另一个重要特性,反映了器件本身性能的好坏,需要以存储块为单位进行顺次擦除,由于闪存集成了大量存储块,因此与读写操作相比,整体擦除非常耗时。

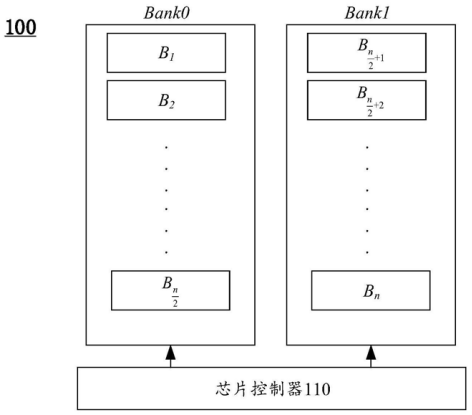

图1 常规存储结构示意图

图1展示了一种现有的闪存的存储结构图,该存储结构100包括两个存储体Bank0、Bank1,并平均分配有n个存储块,芯片控制器110耦合两个存储体,可执行读取,写入和擦除的操作。在对存储结构整体擦除的过程中,需要依次对各个存储块顺序执行擦除步骤。由于这种擦除方法需要对每个存储块单独进行操作,并且只有当上一个存储块完成擦除操作后才可以对下一个存储块进行擦除,导致完成整体擦除的效率非常低。

面对如何提高闪存整体擦除的效率问题,武汉新芯公司在2019年12月12日提出的一项名为“存储结构及其擦除方法”发明专利(申请号:201911215946.9)中提到了解决方案,此专利的申请人为武汉新芯集成电路制造有限公司。

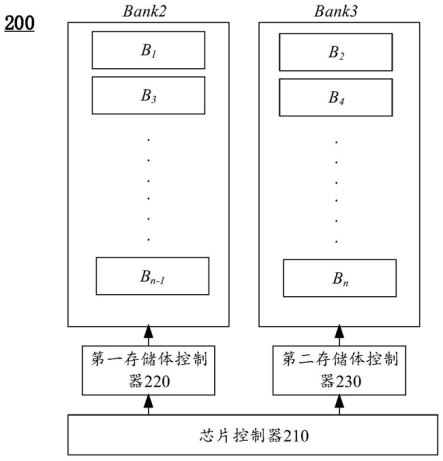

图2 专利中改进的存储结构示意图

图2展示了该专利中改进的存储结构,与传统结构相似,该存储结构至少包括两个存储体,分别记为第一存储体Bank2和第二存储体Bank3,并具有n个存储块。存储结构的控制器包括芯片控制器210、第一存储体控制器220及第二存储体控制器230,存储体控制器分别控制各自的存储体bank,同时受到总芯片控制器控制,实现基本的读、写、擦除操作。

与现有存储器件的顺序擦除方法不同,该专利中提出流水线并行擦除方式。当存储结构需要整体擦除时,控制器控制存储块B1、B2… Bn以设定的擦除方式按照编号顺次进行第一过程和第二过程的擦除操作,如存储块Bi在执行第二过程时,存储块Bi+1在执行第一过程,即对于编号相邻的两个存储块,存储块Bi执行第二过程和存储块Bi+1执行第一过程是同步进行的,当存储块Bi完成第二过程且存储块Bi+1完成第一过程之后,存储块Bi完成擦除;存储块Bi+1执行第二过程,同时存储块Bi+2执行第一过程……,这样以流水线的方式继续下去,直至存储块Bn完成擦除,从而存储结构完成整体擦除操作

以上就是武汉新芯公司关于NOR Flash存储结构和擦除方法的专利内容介绍,相比于顺序执行,流水线形式的并行擦除方法可以显著提高擦除效率,从而进一步提高其闪存产品的竞争力。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)