继上次使用VCS基础操作和makefile的书写,如果我们最后不使用vcs而是使用verdi该如何调用呢?和上次一样,我们同样要把我们的.v文件和tb文件的路径放到file\_list.f中(上次是file.list)之后写makefile,制作好以后就可以使用make语句完成。

作者:Trustintruth

来源: https://zhuanlan.zhihu.com/p/105863018

makefile如下

.PHONY: com sim cov clean debug

OUTPUT = simv

ALL_DEFINE = +define+DUMP_VPD

# Code coverage command

CM = -cm line+cond+fsm+branch+tgl

CM_NAME = -cm_name $(OUTPUT)

CN_DIR = -cm_dir ./$(OUTPUT).vdb

# vpd file name

VPD_NAME = +vpdfile+$(OUTPUT).vpd

#Compile command

#VCS = vcs +v2k -timescale=1ns/1ns

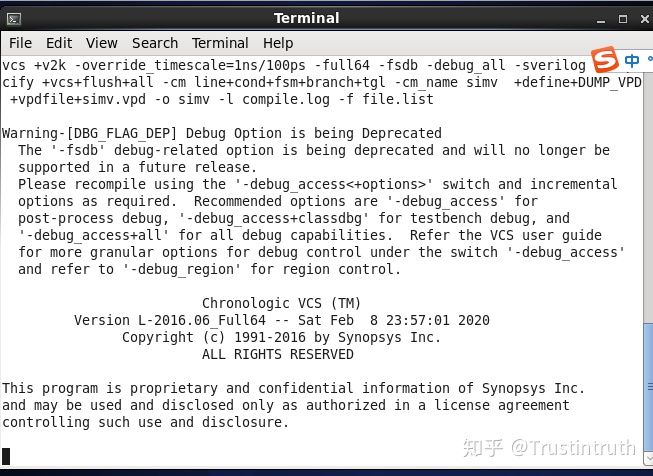

VCS = vcs +v2k -override_timescale=1ns/100ps \

-full64 \

-fsdb \

-debug_all \

-sverilog \

+nospecify \

+vcs+flush+all \

$(CM) \

$(CM_NAME) \

$(CM_DIR) \

$(ALL_DEFINE) \

$(VPD_NAME) \

-o $(OUTPUT) \

-l compile.log

#simulation command

SIM = ./$(OUTPUT) \

+ntb_ramdom_seend_automatic \

$(CM) $(CM_NAME) $(CM_DIR) \

$(VPD_NAME) \

$(ALL_DEFINE) \

-l $(OUTPUT).log

# start compile

com:

$(VCS) -f file_list.f

#Start simulation

sim:

$(SIM)

#show the coverage

cov:

dve -covdir *vdb &

debug:

dve -vpd $(OUTPUT).vpd &

#start clean

clean:

rm -rf ./csrc *.daidir ./csrc \

*.log *.vpd *.vdb simv* *.key \

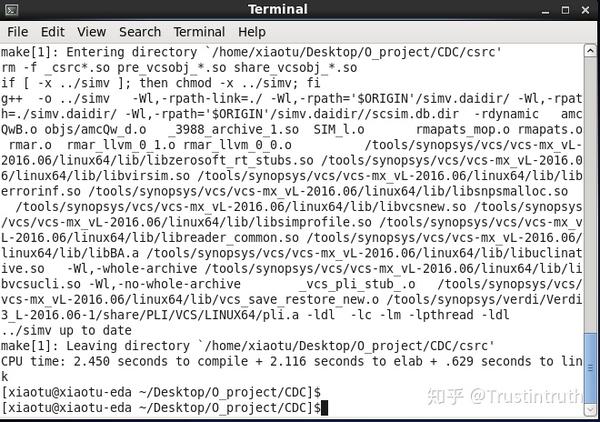

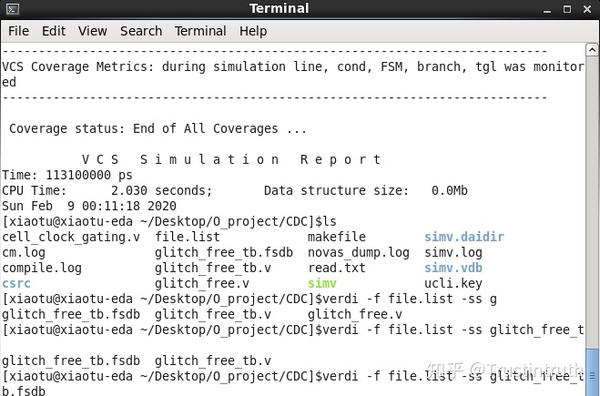

+race.out* novas* verdi* *fsdb apb2apb_async保存好之后,首先make com

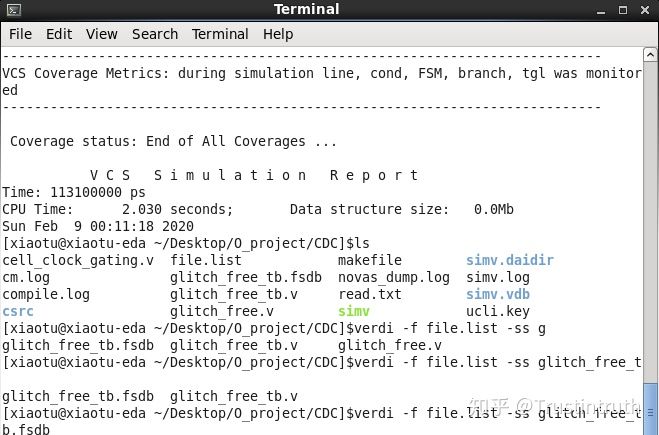

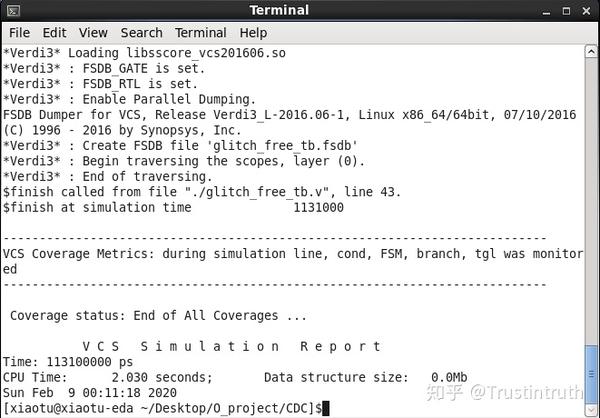

之后 make sim

之后ls一下,发现路径下出现一个.fsdb文件(我在makefile中是glitch\_free\_tb.fsdb,如果需要可以在makefile中更改文件名即可)输入指令

verdi -f file_list.f -ss glitch_free_tb.fsdb

在操作时我更改了file.list,按照文中的makefile制作的在此处按照上面的指令,不要按图里的

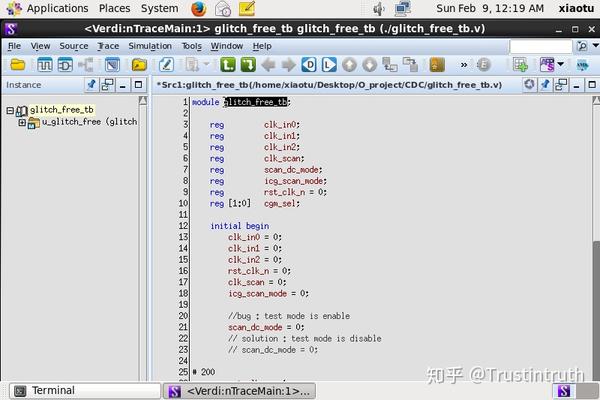

之后进入界面

点击最小化进入界面进行操作

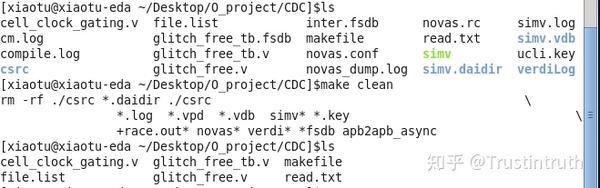

如果需要删除中间文件 输入make clean

获取更多代码与资料,欢迎关注我啊!

推荐阅读

关注此系列,请关注专栏FPGA的逻辑