作者:Trustintruth

来源: https://zhuanlan.zhihu.com/p/105165439

首先我们来看Makefile是什么,引一段CSDN博客中的文段

make命令执行时,需要一个 Makefile 文件,以告诉make命令需要怎么样的去编译和链接程序。

首先,我们用一个示例来说明Makefile的书写规则。以便给大家一个感兴认识。这个示例来源于GNU的make使用手册,在这个示例中,我们的工程有8个C文件,和3个头文件,我们要写一个Makefile来告诉make命令如何编译和链接这几个文件。我们的规则是:1.如果这个工程没有编译过,那么我们的所有C文件都要编译并被链接。

2.如果这个工程的某几个C文件被修改,那么我们只编译被修改的C文件,并链接目标程序。

3.如果这个工程的头文件被改变了,那么我们需要编译引用了这几个头文件的C文件,并链接目标程序。只要我们的Makefile写得够好,所有的这一切,我们只用一个make命令就可以完成,make命令会自动智能地根据当前的文件修改的情况来确定哪些文件需要重编译,从而自己编译所需要的文件和链接目标程序。

简单来说就是我们使用一个make指令来代替先前的许多命令。

再来说VCS,什么是VCS呢?

下面说基础操作(最最基础的)

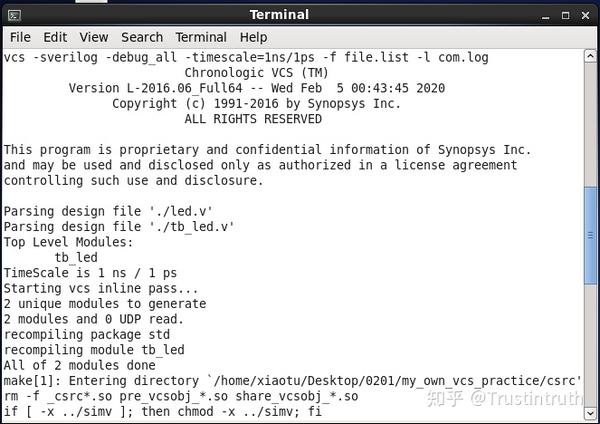

首先进入个人的目录中.v文件的路径下,对我们设计好的.v文件和tb文件首先进行编译,在终端Terminal中输入

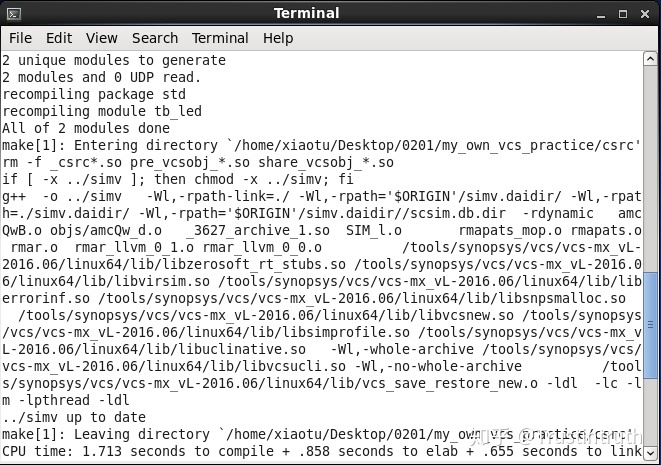

vcs -sverilog -debug_all -timescale1ns/1ps led.v tb_led.v -l com.log这样对源代码RTL和testbench进行编译。其中led.v是设计文件,tb\_led为测试文件。

跑完之后可以ls一下,看到在目录中出现了simv这个可执行文件

接下来输入指令来跑仿真

./simv -l sim.log

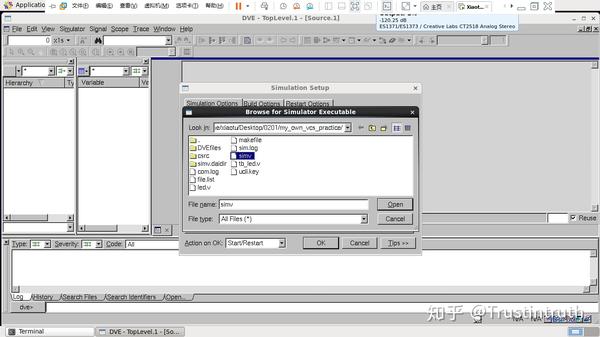

最后在dve中查看波形

dve -vpd vcdplus.vpd &其中这个&表示后台运行。这样我们就打开了dve界面,在图形化界面中选择simv进行setup 、run 即可

但是这样太过于复杂了,所以我们选择使用Makefile。首先我们的的要做的make指令包括:

- make all 进行上述所有的操作

- make com 编译

- make sim 运行sim

- make run\_dve 打开DVE

- make clean 删除仿真中间文件

我们在终端中有Makefile的目录下只需要输入上述make指令即可完成操作

在此之前我们首先将.v tb文件的路径生成为file.list,在中断中输入

find -name "*.v" > file.list打开file.list成这样

之后gvim makefile

all: com sim run_dve

com:

vcs -sverilog -debug_all -timescale1ns/1ps led.v tb_led.v -l com.log

sim:

./simv -l sim.log

run_dve:

dve -vpd vcdplus.vpd &

clean:

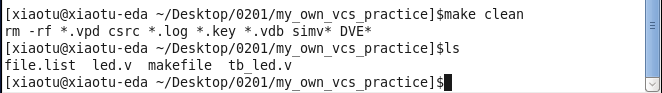

rm -rf *.log csrc simv* *.key *.vpd DVEfile coverage *.vdb保存后在终端中输入 make all 即可进行上述操作,出现的也和上面的都一样。最后做完可以make clean清除刚才仿真生成的文件,可以ls一下查看是否清除干净

推荐阅读

关注此系列,请关注专栏FPGA的逻辑