【嘉德点评】微电子所的该项专利,在形成了电介质侧墙之后,再进行各器件之间的电隔离操作例如切断或氧化,因此,电介质侧墙材料没有延伸进入相邻的单元器件的相对栅电极端面之间,从而避免由于切口处存在侧墙材料而出现孔洞等缺陷,并且可以减少器件间的最小电隔离距离,从而增大了器件的集成度。

集微网消息,在2018年2月,中科院微电子所因英特尔酷睿系列处理器侵犯其FinFET专利而提起侵权诉讼,而在今年7月底,英特尔却又对微电子所的此项专利进行无效申请,虽然之前英特尔在中美两地发起的无效申请,均以失败告终,但该专利到底有什么魔力呢?让我们一起来解密一下。

随着集成密度的日益提高,FinFET(鳍式场效应晶体管)由于其良好的电学性能、可扩展性以及与常规制造工艺的兼容性而倍受关注。但是,随着器件特征尺寸的日益缩小,要为鳍式晶体管形成栅电极变得越来越困难。而一些常规工艺还会要求非常精确的(棚电极)端到端间隔,这就使得光学近修正的难度变大。而且近年来为了使用高k棚介质/金属棚的结构而采用替代棚工艺,也导致切断掩膜的设计方法更加复杂。

为此,微电子所在2011年8月22日申请了一项名为“半导体器件结构及其制作方法、及半导体鳝制作方法”的发明专利(申请号:201110240931.5),专利权人为中国科学院微电子研究所。该发明专利提供一种半导体器件结构及其制作方法,以克服现有技术中的问题。

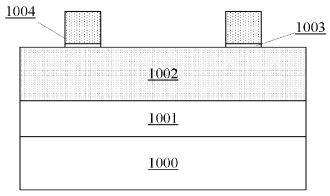

图1 半导体器件制作结构图1

如图1所示,在SOI衬底(包括两个Si层1000、1002以及嵌于它们之间的SiO2层1001)上形成鳍1002之后,依次形成栅介质层1003和栅电极层1004。然后,印制与将要形成的栅极线图案相对应的光刻胶线形图案。

在形成了线形图案之后,不使用切断掩模来形成切口图案,而是直接利用线形图案来刻蚀栅电极层,以形成平行的栅极线1004。同时,还刻蚀了栅介质层1003,以使栅介质层1003仅位于栅极线1004之下。

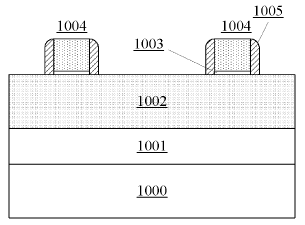

图2 半导体器件制作结构图2

通过在整个半导体器件结构上淀积一层或多层电介质材料,再通过反应离子刻蚀形成电介质侧墙层1005,得到如图2所示的结构图。

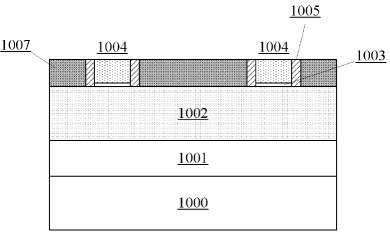

图3 半导体器件制作结构图3

接下来,可以在得到的结构上形成层间电介质层1007(参见图3)。为了进一步改善器件的性能,层间电介质层由带有应力的电介质材料制成。例如,对于NFET,层间电介质层可以由带有拉应力的电介质材料制成;而对于PFET,层间电介质层可以由带有压应力的电介质材料制成。

随后,按照将如上形成的栅极线1004、电介质侧墙层1005,在预定区域处切断,以实现各单元器件之间的电隔离。通常来说,在鳍1002之间的无源区域(field)上方进行切断,切口的宽度(沿图中竖直方向)一般为1-10nm。这种切断可以利用切断掩模,通过反应离子刻蚀或激光切割刻蚀等方法来实现。

这样,就基本上完成了本发明的半导体器件结构的制作,以上就是这项争议专利的全部内容。该专利中,在形成了电介质侧墙之后,再进行各器件之间的电隔离操作例如切断或氧化。因此,电介质侧墙材料没有延伸进入相邻的单元器件的相对栅电极端面之间,从而避免由于切口处存在侧墙材料而出现孔洞等缺陷,并且可以减少器件间的最小电隔离距离,从而增大了器件的集成度,降低了集成电路的制造成本,而且本发明还与替代栅工艺相兼容,从而实现多种工艺选择。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。