【嘉德点评】微电子的这项专利技术能够增强MOSFET沟道区应力,从而提高载流子迁移率,改善器件性能。

集微网消息,中科院微电子所作为国内半导体领域顶尖的科研机构,在集成电路、物联网等领域产出了5000余项专利。然而最近其申请号为201010269260.0的发明专利却被Intel发起无效挑战,原因在于微电子所用该专利起诉Intel酷睿i3微处理器侵权。

在半导体领域,随着摩尔定律的演进,场效应管(MOSFET)的特征尺寸不断减小,器件的饱和驱动电流变小、截止频率降低。而另一方面,为抑制短沟道效应,防止MOSFET的源极和漏极击穿造成驱动电流增大,必须提高沟道中的掺杂浓度。为此,现有技术通常采用应变沟道技术以提高载流子的迁移率,改善器件的电学性能。

然而,由于MOSFET器件有源区之间大多采用浅沟槽隔离(STI)结构,形成STI后的MOSFET器件要经过一系列例如侵蚀清洗、反应离子刻蚀等工艺,容易造成STI结构减损,应力经由侧向界面释放,导致应变沟道工程产生的性能改善效果减弱。

为解决这一问题,早在2010年8月31日,微电子所就申请了一项名为“半导体结构及其制造方法”的发明专利(申请号:201010269260.0),专利权人为中国科学院微电子研究所,这项专利提出的半导体结构可进一步增强MOSFET的沟道应力。

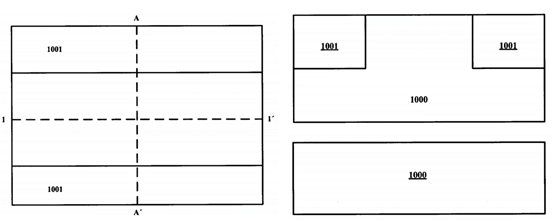

图1 半导体结构在衬底上形成第一浅沟槽隔离示意图

图1展示了在半导体衬底1000上以常规方法形成第一浅沟槽隔离1001的结构图,右侧两个图示分别为左侧半导体衬底1000沿A-A'线、1-1'线的剖视图,衬底1000可以是体硅或绝缘体上硅(SOI),也可以是其他半导体材料,如GaAs等III-V族化合物半导体材料。

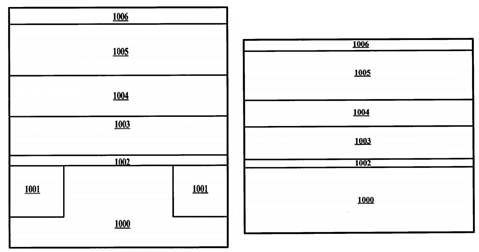

图2 半导体衬底生成层级结构示意图

紧接着,在半导体衬底1000上利用传统的淀积工艺顺次形成栅介质层1002、导电层1003(金属或多晶硅层)、氮化物层1004、第二多晶硅层1005、氧化物层1006。各层厚度分别为1~3nm、50~100nm、50~70nm、100~150nm、10~20nm。

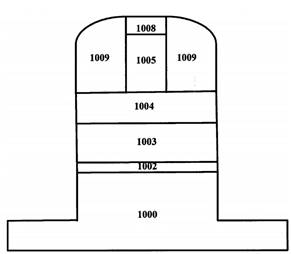

图3 第二浅沟槽隔离剖视图

随后需要图案化栅极,具体在氧化物层1006上旋涂光致抗蚀剂,并在一定温度下前烘,用栅极所需的掩模图形来曝光、显影,再次高温处理后在氧化物层上形成光致抗蚀剂图形。紧接着以光致抗蚀剂为掩模,刻蚀氧化物层1006和第二多晶硅层1005,然后去除光致抗蚀剂,淀积氧化物层,刻蚀形成覆盖第二多晶硅层1005顶部的氧化物盖帽层1008及侧墙1009,并选择性刻蚀氮化物层1004、第一多晶硅层1003、栅介质层1002及一部分半导体衬底1000,从而形成用于第二浅沟槽隔离的沟槽,如图3所示。

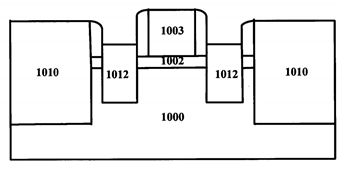

图4 生成完整半导体结构图

为抑制短沟道效应,通过离子注入形成针对源漏区的晕环和延伸结构,然后淀积氮化物隔离介质,并形成源漏凹槽,构成应力晶层。接着将外延形成具有应力的源漏区,通过选择性外延生长形成应力层以调节沟道应力,从而提高器件性能。最后通过反应离子刻蚀去除氮化物层,暴露栅极顶部和第一多晶硅层,并在源漏区和栅极导电层上形成金属硅化物,如图4所示。

以上就是微电子所在这项专利中关于MOSFET的全部内容,抛却专利权纠纷单从技术上看,这一发明能够增强MOSFET沟道区应力,从而提高载流子迁移率,改善器件性能。

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)