原作者信息:

Mark L. Chang

Electrical and Computer Engineering

Franklin W. Olin College of Engineering

来源: https://zhuanlan.zhihu.com/p/161302966

注:原文版权归作者所有,本翻译仅为爱好所作,与任职单位无关。

1.2 阵列与互连结构 The Array and Interconnect

通过 LUT 和 D 触发器,我们可以定义其上的逻辑层次—— FPGA 中的逻辑块(logic block)或功能块(function block)。我们在单个逻辑块的层面上,已经了解了 FPGA 如何执行计算,后面我们将重点放在如何在 FPGA 结构中放置这些逻辑块并将它们连接在一起。

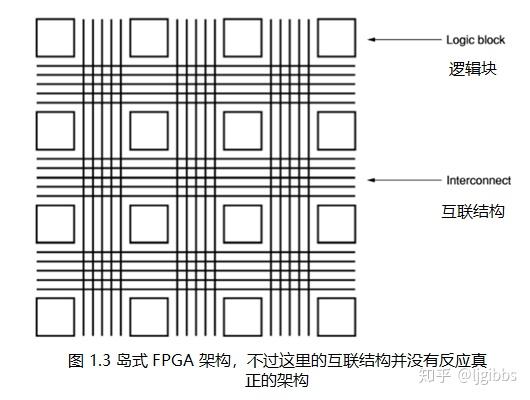

当前流行的 FPGA 实现通常被称为岛式架构(island-style architecture)。如图1.3所示,该架构中逻辑块被平铺在二维阵列中,并以某种方式互连。逻辑块好似“漂浮”在互联海洋中的岛屿。

在这种阵列结构中,计算分布在整个 FPGA 的空间结构上进行。大型计算分成以 4-LUT 大小为单位的小块,并映射到阵列中的物理逻辑块。通过配置互连结构,使其在逻辑块之间正确地路由信号。只有有足够数量的逻辑块,理论上就可以在 FPGA 上实现任何我们想要的计算。

1.2.1 互联架构 Interconnect Structures

图 1.3 并未完整地说明整个互联结构。所示的互连结构也并不代表实际 FPGA 设计中所采用的任何结构,只是一个示例而已。本节将介绍当今许多 FPGA 中实际存在的互连结构。首先从一个小面积的互连结构开始讨论,然后扩展到更大的结构中,以了解对不同类型互连的需求。我们从最简单的最近邻通信开始。

最近邻结构 Nearest neighbor

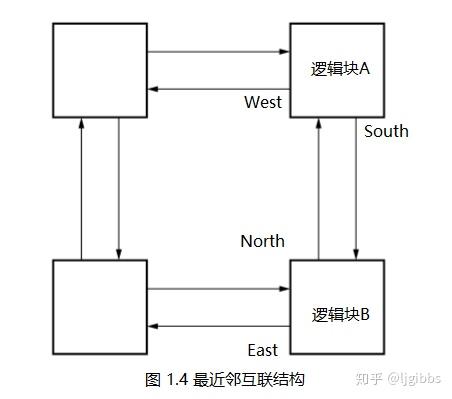

最近邻通信的实际结构和听上去一样简单。从图 1.4 中的 2×2 逻辑块阵列,可以看到某个逻辑块只需要四个方向上的输入或者输出端口:北、南、东和西,就可以与其相邻的逻辑块通信。

图 1.4 可能是一个最简单的路由体系结构的示例。虽然看起来十分地落后,但它确实曾经在一些(现在已经淘汰的)商用 FPGA 中被采用。即使在这样一个很简单的方案中,这种结构仍然存在严重的延迟和连接性问题。想象一下,假设采用这一结构实现大于 2×2 的阵列,比如 1024×1024 阵列。由于只在临近的逻辑块间存在连接,信号的延迟与距离成线性关系,因为信号必须经过多个逻辑块(和多个交换结构)才能到达其最终目的地。

从连接性的观点来看,由于在近邻结构中,信号没有绕过路由结构中逻辑块的能力,所有每一个信号跳数都需要经过一个逻辑块。再加之每个方向上只有一个双向信号对,这限制了通过逻辑块的信号数量。因为路由需要而途径逻辑块的信号无法与逻辑块本身产生与接收的信号并行。

由于这些局限性,最近邻结构很少单独使用,但它几乎总是存在于当前的 FPGA 结构中,并通常会与以下一些技术共同使用,以改善近邻结构的局限性。

分段结构 Segmented

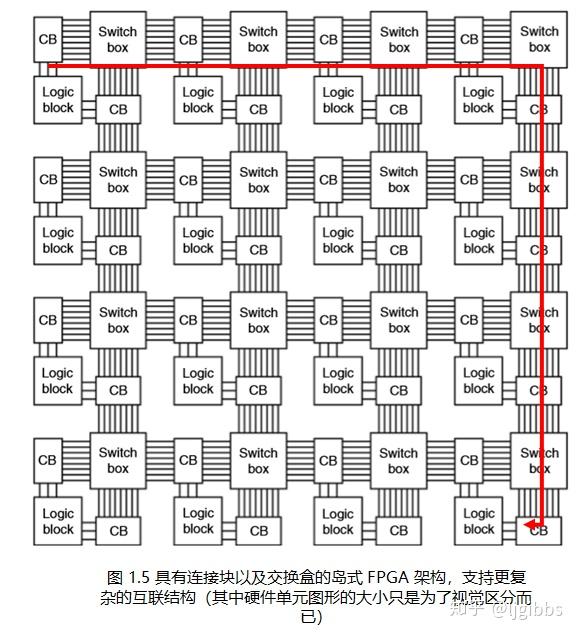

随着我们所探讨的互联结构复杂性的增加,我们开始不再局限于此前讨论的,只有逻辑块这一种硬件单元的情况。大多数当前的 FPGA 架构更接近图 1.5,包括逻辑块以外的硬件单元,而不是图 1.3。

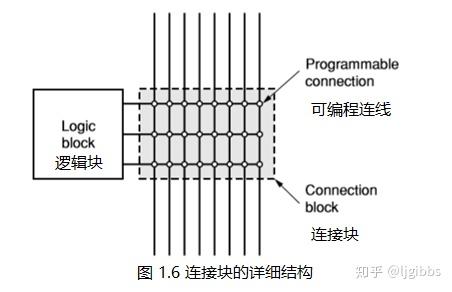

在图 1.5中,我们引入了连接块(Connect block)和交换盒(Switch box/block,或称交换块)两种硬件单元。其中的路由结构更具通用性并呈现为网状(meshlike)。逻辑块通过连接块访问附近的通信资源,连接块通过可编程交换结构或者多路复用器,将逻辑块的输入和输出信号连接到整体的路由结构中。连接块(详细结构如图 1.6 所示)允许将逻辑块输入和输出信号分配给任意水平和垂直方向上的路径,连接到相应单元,增加了布线灵活性。

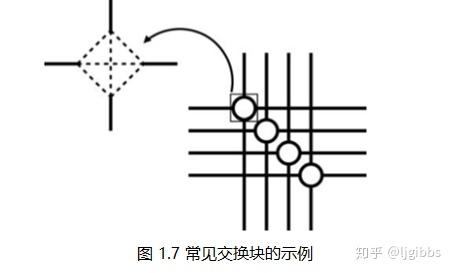

如图 1.7 所示,在水平和垂直布线路径的交汇处设置交换块。通常来说,它只是一个可编程矩阵开关,允许一条路径上的信号连接到另一条路径。取决于开关块的设计,这种连接可以通过不同路径间的开关实现,或者采用多条直连的路径。(译注:个人感觉类似于 bus 和 crossbar 的区别)交换模块的设计本身是一个完整的研究领域,产生了许多不同的设计,呈现出不同程度的连通性和效率[3-5]。不过,对这项研究的详细讨论超出了本书的范围。

分段互连的概念正变得更加清晰,其实是一种在最近邻结构上的改进,实质上进行的仍然是最近邻通信。但互联是通过一对连接块和交换块实现的,而不是逻辑块本身。此外,对于传输距离更长的信号,可以配置其所途径的所有开关块,将不同的段(segment)切换至直连状态,以将两个相隔较远的逻辑块直连在一起。可以看作是一种模拟实现跨越任意距离的长信号路径的方法,是一条实际上由较短的“段”组成的逻辑长导线。(译注:如图 1.5 中的红色箭头,将两个逻辑块跨越多个连接与交换块互联)

这种互连结构并不能从根本上改善最近邻互连结构的延迟特性。然而,连接块和交换盒的引入将互连结构与逻辑块相分离,可以在不消耗逻辑块资源的情况下完成长距离路由。

为了实际改进结构中长距离信号的延迟特性,引进了更长的直连物理导线。例如,将跨越一个逻辑块的导线的长度设为 L1。在一些分段布线架构中,更长的导线能够更有效地长距离传输信号。包括可以跨过4、8个逻辑块(L4/L8),甚至更多逻辑块的导线。交换块(包括嵌入式的交换单元等)成为信号的中间节点,使信号能在各种距离的导线间进行交换。此功能允许信号延迟小于O(N),N 代表传输距离跨越 N 个逻辑块,通信延迟通过减少信号传输路径中的中间交换节点的数量实现。

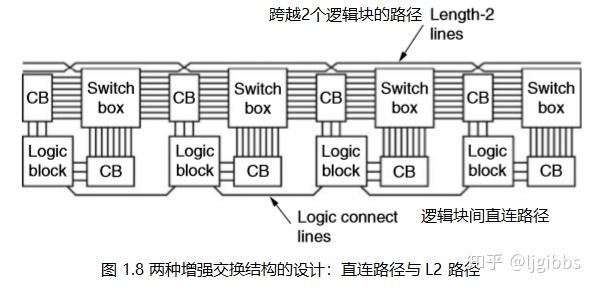

图 1.8 说明了两种增强互联性的设计:一是逻辑块之间的直接连接路径,二是长度为2(L2)的连接路径。直连路径可以节约路由资源留给其他用途,L2 路径允许信号在大致相同的交换延迟下,传输更长的距离。这种互连架构与 Xilinx XC4000 系列商用 FPGA 比较接近。

层次化互联结构 Hierarchical

层次化结构采用稍微不同的方法来减少长距离信号的传输延迟。考虑图 1.9 中的结构。在层次结构的最底层,2×2 个逻辑块阵列被组合成一个簇(cluster)。在这个簇的 4 个块中,只能进行本地路由或者最近的邻居路由。4 个簇形成一个更大的、包含 16 个逻辑块的 2×2 簇集群。在这个层次结构中,在各个较小的 2×2 簇边界上,布置较长的导线将簇集群内部的 4 个逻辑簇连接到该层次中的其他簇集群。这样的模式在更高层次中反复使用,构成更大的簇,并设置更长的导线连接各个部分。

上文描述的层次化互连模式利用了这样一个假设:一个设计良好的(并且布局良好的)电路,主要与相邻块连接,只需要有限数量的长距离信号传输。通过在更高层次上提供更少的跨区域路由资源,这种互连体系结构保持区域效率的同时,保留了一些较长的布线路径,以最大限度地减少长距离传输信号的延迟。

在分段体系结构中,连接不同路由层次的连接点可以位于互连结构中的任何位置。可以在现有的交换块中创建新的跨层次连接点,也可以布置完全独立的跨层次交换站点,以便在不同层次结构级别之间连接逻辑块。

1.2.2 可编程性 Programmability

与典型商用 FPGA 中的逻辑块一样,互连结构中的每个交换点都是可编程的。在连接块内部,可编程多路复用器选择每个逻辑块的输入,决定输出映射的路由路径;在交换块中,垂直和水平路由路径之间的连接同样通过可编程开关进行切换;最后,通过可编程交换结构,在不同长度和通往不同层次结构的路由路径之间进行切换。对于所有这些可编程点,如同在逻辑块中一样,现代 FPGA 采用 SRAM 数据比特来保存用户定义的配置值。本章后面的部分将对这些配置比特进行更多的讨论。

1.2.3 总结 Summary

可编程互联路由资源自然与 FPGA 的逻辑计算资源对应,其中逻辑用于算术和逻辑计算,互连结构接收逻辑块的输出结果,并将其作为输入路由到其他逻辑块。通过防置逻辑块,并通过一系列可编程互连结构将它们连接起来,FPGA 可以实现复杂的数字电路。空间分布计算(spatial computing)的本质是将计算分布到整个 FPGA 的物理空间来实现的。

今天的商用 FPGA 通常使用混合使用上述的互连架构中,来提供顺畅与灵活的路由资源。在实际实现中,分段和层次结构可能并不总是如本文的示例中那样,面积与连接数呈现对数缩放的结构。在现代 FPGA 中,所消耗的芯片面积主要由互联结构的面积决定。顺便一提,90% 的硅片面积由互连结构使用,而只有 10% 是由逻辑所使用。在这种不平衡之下,互连体系结构变得越来越重要,特别是从延迟的角度来看。

推荐阅读

关注此系列,请关注专栏FPGA的逻辑