集微网消息 集微直播间自开播以来获得了大量来自行业的关注与好评。其中“集微公开课”栏目联合行业头部企业,通过线上直播的方式分享精彩主题内容,同时设立直播间文字提问互动环节。集微网希望将“集微公开课”栏目打造成中国ICT产业最专业、优质的线上培训课程,深化产教融合,助力中国ICT产业发展。

第34期“集微公开课”于8月25日(周二)上午10:00直播,邀请到成都锐成芯微科技股份有限公司副总经理杨毅,带来以《物联网芯片发展趋势及ACTT低功耗射频IP平台》为主题的精彩演讲。

近几年,随着物联网行业的高速发展,物联网芯片正超过PC、手机芯片领域,有望成为未来最大的芯片市场。“未来30年到50年会是物联网时代。”成都锐成芯微科技股份有限公司副总经理杨毅在公开课中这样说道。

万物互联时代需要怎样的物联网芯片?

杨毅预测未来数十年,物联网将和互联网一起,成为马斯诺第一需求。杨毅介绍,物联网的连接方式主要有蓝牙,Wi-Fi和5G NB-IoT三种。

杨毅表示,以上三种连接方式分别满足物联网时代不同的应用需求。他认为,未来一定时期内,蓝牙、Wi-Fi、5G(NB-IoT)将形成三足鼎立的格局。

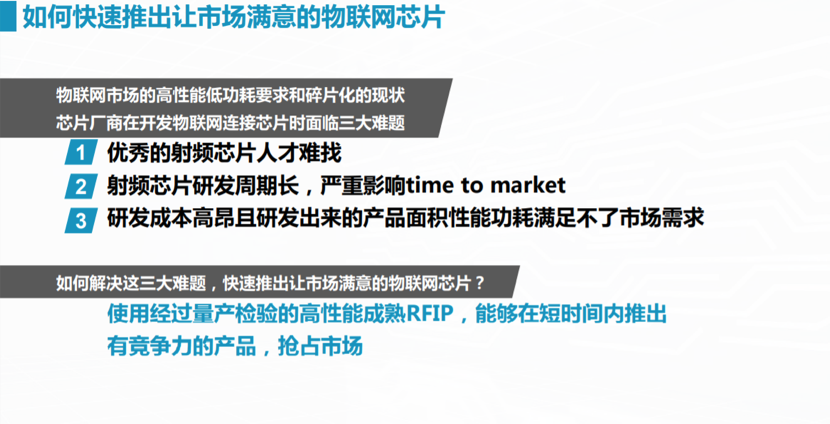

万物互联的时代,连接需求不断增长,也对芯片设计也提出了更高的要求,包括低功耗、低成本与高性能等,加之物联网碎片化的现状,使得芯片厂商在开发物联网连接芯片时面临三大难题:第一是优秀的射频芯片人才难找;第二是射频芯片研发周期长,严重影响上市时间;第三是研发成本高昂且研发出来的产品面积性能功耗满足不了市场需求。

在此背景下,怎样才能快速推出让市场满意的物联网芯片?对此,杨毅表示,使用经过量产检验的高性能成熟RFIP(射频IP),搭配自己差异化的一些特性,能够在短时间内推出有竞争力的产品,抢占市场。

成都锐成芯微通过在2019年收购RF芯片厂商成都盛芯微,成为大陆第一家蓝牙RFIP供应商,并针对物联网痛点,推出三大系列物联网RF IP,包括蓝牙、5G NB-IoT、和Wi-Fi。

如何研发一款超低功耗高性能物联网RFIP?

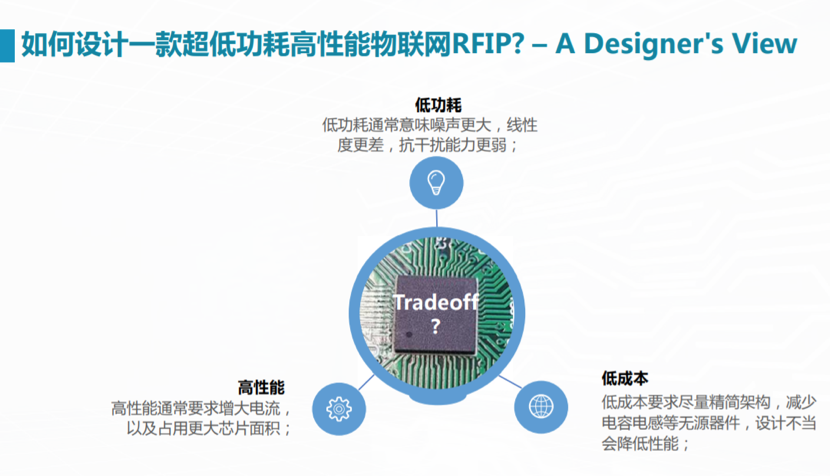

那么,如何才能研发一款超低功耗高性能物联网RFIP?针对这个问题,杨毅从工程师的角度进行了详细介绍。

他指出,低功耗通常意味噪声更大,线性度更差,抗干扰能力更弱;高性能通常要求增大电流,以及占用更大芯片面积;而低成本则要求尽量精简架构,减少电容电感等无源器件,设计不当会降低性能。

相互之间有矛盾的地方,需要有大量的Tradeoff来确保芯片实现最优性能。

对此,杨毅以BLE RFIP芯片为例,主要从发射机和接收机的架构选择,具体电路设计方面进行讲解。

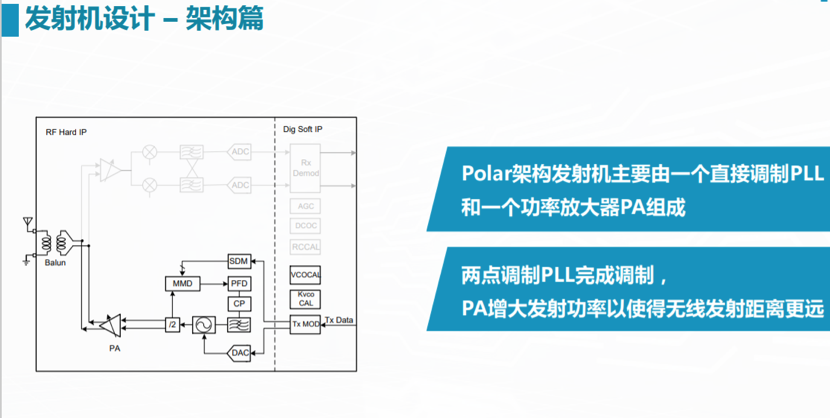

成都锐成芯微在发射机架构层面选择Polar架构,从而在架构层面实现低功耗和低成本。

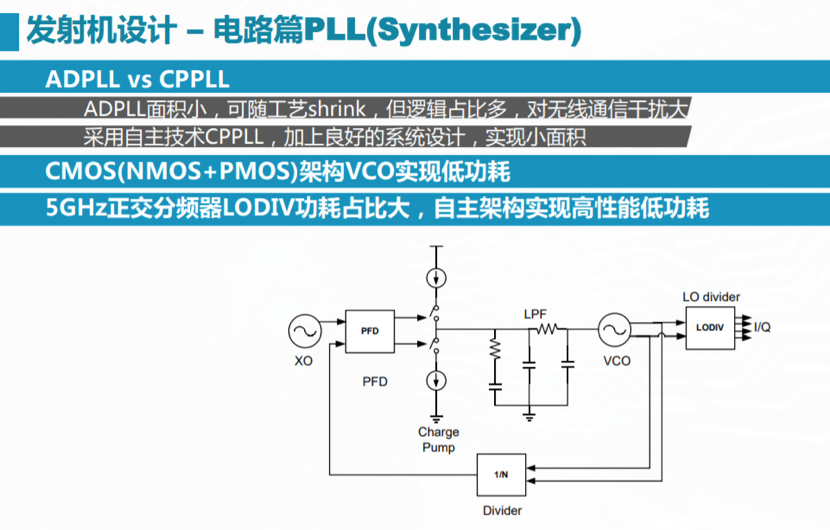

具体到发射机电路设计方面,其中PLL(锁相环)分为全数字锁相环ADPLL和电荷泵锁相环CPPLL两种。

ADPLL可随工艺shrink,环路滤波器数字化实现面积小,但缺点是逻辑电路占比多,会对无线通信造成很大干扰。

成都锐成芯微选择CPPLL,加上良好的系统设计,采用自主技术,实现小面积。

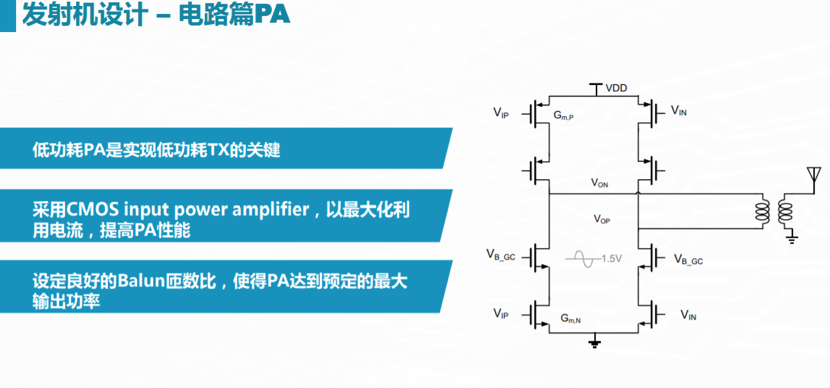

PA设计方面,成都锐成芯微采用CMOS input power amplifier,可以最大化利用电流,提高PA性能。

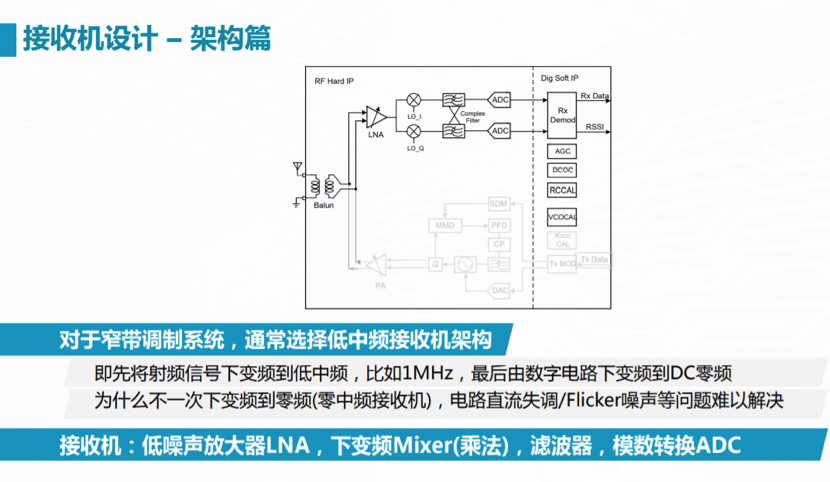

接收机设计方面,主要从低噪声放大器LNA、下变频Mixer(乘法)、滤波器、模数转换ADC四部分进行优化。

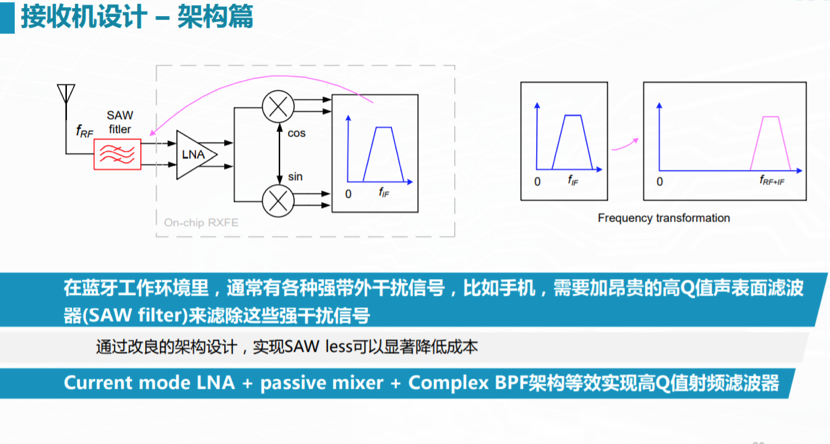

在架构选择方面,通过改良的架构设计,成都锐成芯微在几乎不牺牲性能的情况下移除SAW filter实现SAW-less可以显著降低成本。

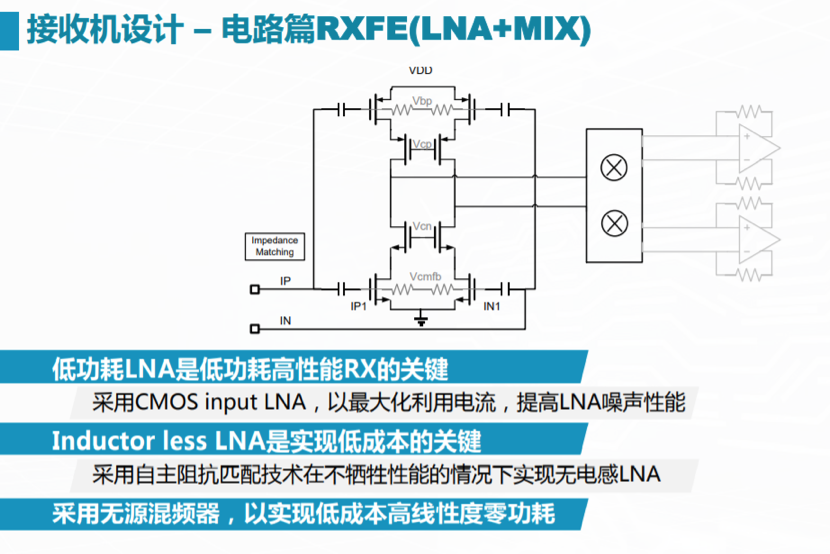

在接收机电路LNA部分,成都锐成芯微采用CMOS input,以最大化利用宝贵的电流,提高LNA噪声性能。采用自主阻抗匹配技术在不牺牲性能的情况下实现无电感LNA。除此之外,ACTT采用无源混频器,以实现低成本高线性度零功耗。

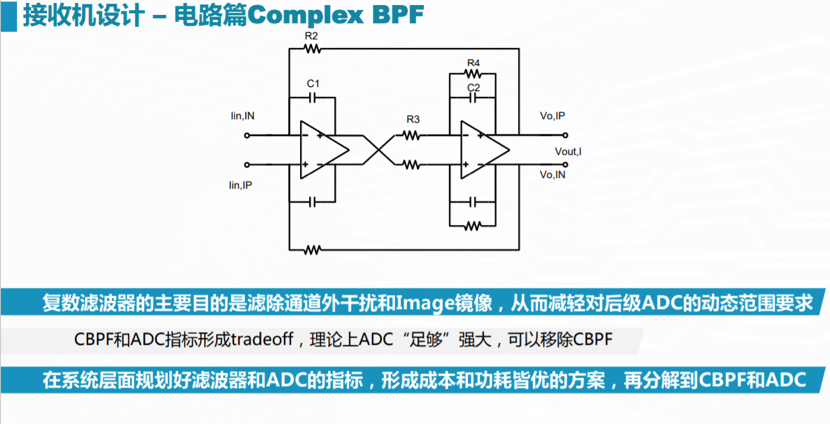

在BPF部分,CBPF和ADC指标形成tradeoff,系统层面规划好滤波器和ADC的指标,形成成本和功耗皆优的方案,再分解到CBPF和ADC。

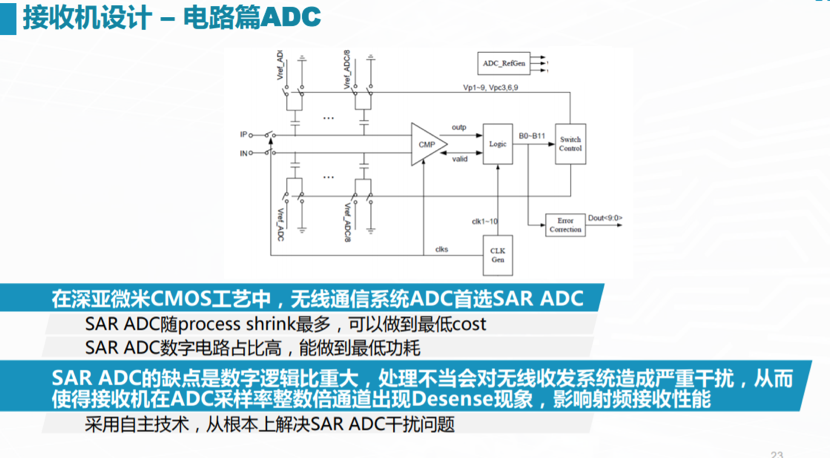

在ADC部分,据杨毅介绍,在深亚微米CMOS工艺中,无线通信系统ADC首选SAR ADC,

但是SAR ADC的缺点是数字逻辑电路比重大,处理不当会对无线收发系统造成严重干扰,从而使得接收机在ADC采样率整数倍通道出现Desense现象,影响射频接收性能。

针对这一情况,成都锐成芯微采用自主技术,从根本上解决SAR ADC干扰问题。

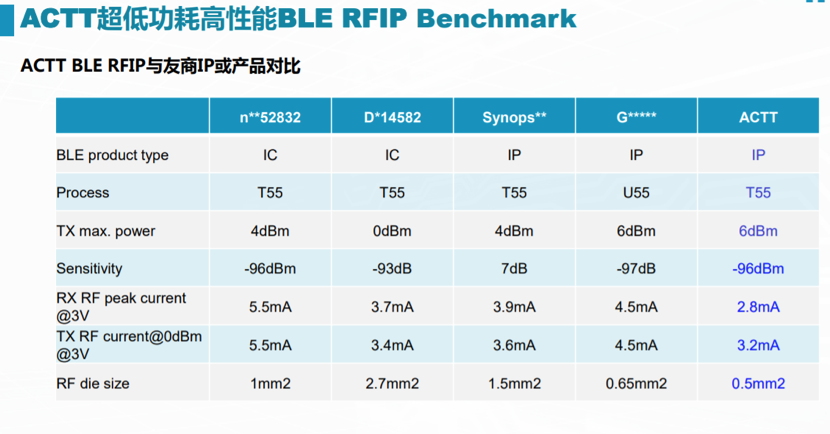

通过以上一系列的优化设计,功耗低、性能优良,且面积低于0.5mm^2的物联网RFIP设计完成。对此,杨毅将成都锐成芯微BLE RF IP与友商IP或产品对比,从表格中不难看出,成都锐成芯微产品极具竞争优势,尤其在功耗方面,比竞品低很多。

归纳而言,在低功耗方面,成都锐成芯微采用优化的系统级架构设计和电路设计,实现一流的操作功耗;通过采用自主专利技术,实现比常规设计低2/3以上的睡眠功耗。

在低成本方面,高度集成、片上balun、LDO免电容;最小面积RFIP,BLE低至0.5mm2以下;采用普通逻辑工艺,无需特殊器件或Deep nwell,最低1P5M。

在高性能上,采用自主专利技术,确保射频性能良好,所有收发通道无Desense;-40~125C温度范围;成熟量产4年,已被国际Tier1厂商大批量量产检验。

如何又好又快地开发物联网无线SoC芯片?

开发出超低功耗高性能物联网芯片只是抢占物联网市场的第一步,而抓住需求窗口,让产品快速面市能才获得更多市场占有率。

成都锐成芯微用“搭积木”式的运用低功耗射频IP来又好又快地开发满足市场需求的物联网无线SoC芯片。

为某上市客户提供RFIP,以及RFIP+BB IP整合服务,最终实现的芯片兼具高性能、低功耗、低成本优势。

目前,通过ACTT RFIP搭出来的产品通过完整的BQB、FCC/CE、ESD等认证测试在终端市场已出货到国际一流终端厂商。

为了减小客户整合RFIP和基带数字IP的难度,ACTT RFIP完全兼容CEVA Baseband数字IP。此外,ACTT也可提供ACTT RFIP和CEVA Baseband数字IP一站式integration服务。

(校对/kaka)