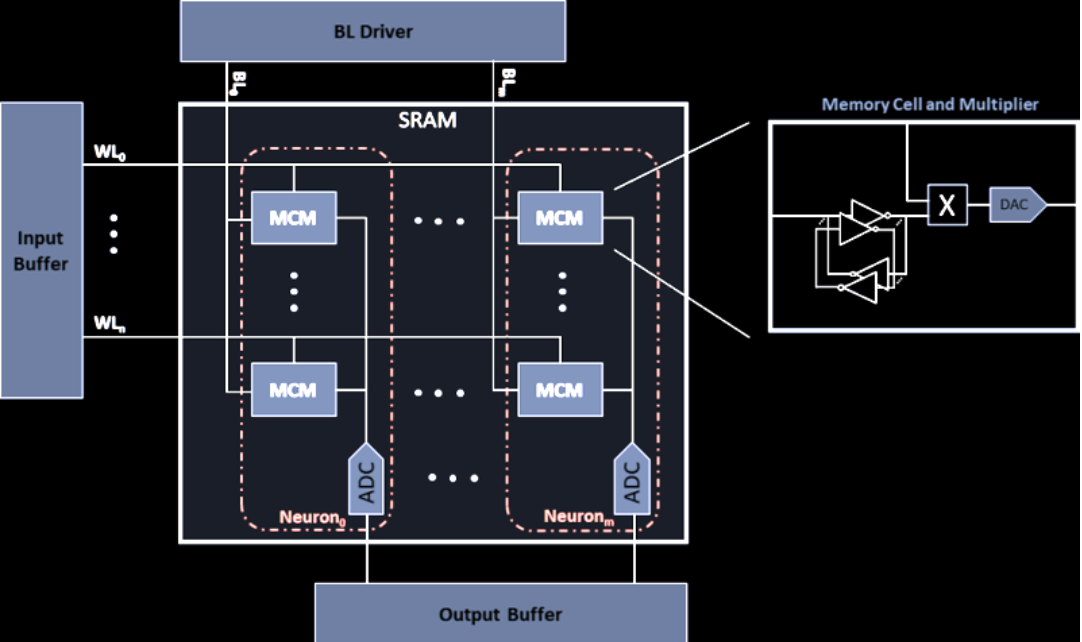

一种新颖的深度学习加速器。专用单元定义了一个SRAM,该单元可以处理矩阵乘法,量化,存储以及推理处理器所需的其他工作。

在Spice仿真中,当使用8位整数数学识别手写数字时,该设计可提供100兆次操作/秒/瓦(TOPS / W)。它的计算密度可以击败Google的TPU一个数量级。

该设计是使用内存中计算方法的加速器产品线中最新的一种。设计使用40纳米NOR闪存单元的深度学习处理器,其目标是为监视摄像机等设备使用低功耗芯片。

设计时使用了很少的模拟电路,因此可以扩展到精细的工艺节点。它可能成为低功耗处理器中引擎(从边缘到云)的引擎。

独特的方式操纵SRAM单元以处理深度学习任务

这个设计使用户可以为从权重到神经网络层甚至单个神经元的所有内容创建自定义参数。这种灵活性可以使将来设计用于训练处理器的设计成为可能。但是尚无用于对该设计进行编程的软件堆栈,可能会在以后解决或留给将来的客户使用。