首发:嵌入式客栈

作者:逸珺

导读

前面总结了UART/I2C的技术要点,SPI相对I2C而言,比较简单。本文来总结一下SPI总线个人认为比较重要的一些技术要点。

什么是SPI?

SPI(Serial Peripheral Interface) 是一种嵌入式系统中应用广泛的同步串行通信、主从架构式总线接口。80年代由摩托罗拉开发,已成为事实标准。

这句话里有几个关键要点:

- 同步

- 串行

- 通信

- 主从

- 总线

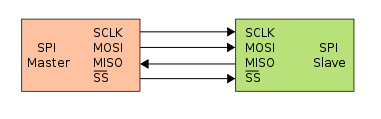

要理解这些要点,先上图,一图胜千言:

常见的SPI接口有这样几个引脚:

- SCLK: 串行时钟,总是主端负责输出(Master)。总是由主端控制该信号,从端为输入采样。

- MOSI:主出从入(Master Output Slave Input)。总是由主端控制该信号,从端为输入采样。

- MISO:主入从出(Master Input Slave Output)。总是由从端控制该信号,主端为输入采样。

:从选择信号(Slave Select)。总是由主端控制该信号,从端为输入采样。

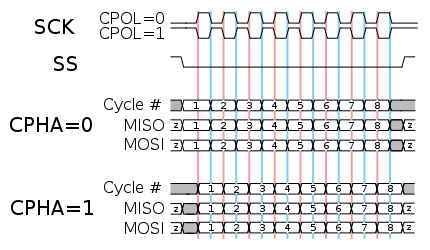

要理解上面这几个信号引脚的内涵,结合时序图,就比较容易理解了:

数字电路中,同步电路是一种通过时钟信号同步存储元件状态变化的数字电路。

- 主端>从端:

:主端发送低电平先选通从芯片,上面加帽表示低有效。啥意思呢?就是这个脚低电平期间选中从设备,主设备发送的时序报文对选中的从设备有效,其他挂载在总线上的设备忽略总线报文。

- SCLK/SCK:发送同步移位时钟。

- MOSI:将数据按照SCLK移位时钟周期,将数据移位发送至该引脚。被选中的从设备依照SCLK/SCK上升沿或者下降沿,按位采样,一般字节的高位在前,具体须遵从芯片手册时序定义。从端依赖SCK/SCLK对MOSI上的信号逐位采样,采样的位依次进入接收移位寄存器,完成对字节的重组。当字节接收完成,再由后续数字电路进行处理。后续处理芯片实现各异,如是一个单片机则可能引发中断请求,如是特定功能数字芯片,则依据接收报文完成相应的功能处理。

- 从端>主端:

:主芯片发送低电平先选通从芯片。

- SCLK/SCK:发送同步移位时钟。

- MISO: 类似MOSI发送位流,依赖SCLK/SCK将位流依次发送至引脚上,主设备在同步时钟的跳变边沿采样该引脚,进而移位接收位流。

- 采样沿:SPI采用边沿触发采样,对MOSI/MISO上的位序列进行采样,实际芯片有下面两种方式勘误见置顶留言,字数限制改不了,抱歉:

- CPHA=0,表示上升沿采样

- CPHA=1,表示下降沿采样

经过这些描述,解释了串行、同步、主从的概念。

什么是通信?

众所周知,计算机是一个二进制系统,所有的信息都是基于0/1进行编码、进行运行管理的。由0/1编码进而表示字符、文本、文件。那么SPI实现了底层的0/1码流的传递机制,能传递0/1,通过应用控制、很自然就能交换信息。

这是否有种一生二、二生三、三生万物的意思呢?

所以在研究各种通信总线的物理层时,就其本质而言都是界定如何对信息流的基本单元0/1进行编码、解码、收发的。

什么是SPI总线呢?

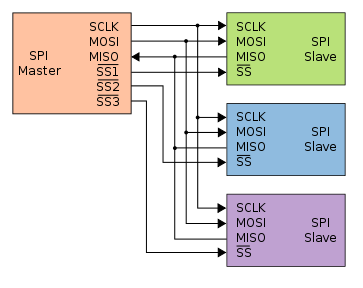

对于SPI总线而言,有两种拓扑:

- 独立片选拓扑:总线拓扑需要更多片选引脚,但通信效率高。信息直接在主从间传递

- 菊花链拓扑:节省引脚,但效率较低,数据信息传递需要级联传递。

独立片选拓扑

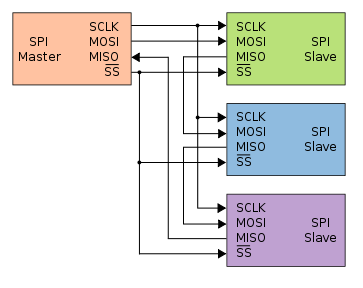

如上图:

- 每个从设备都有独立的片选引脚,主机同一时间段内,与一个从设备进行通信,也即选中一个从设备。

- MOSI/MISO/SCLK并联在一起

- MISO须是三态门,当从设备未选中时,该脚须设置为高阻态,而不能是输出态,否则会影响总线,这句话对于多从设备应用而言,请重点理解。尤其当用GPIO模拟SPI应用而言,须特别注意这一点!

- 对于MOSI/SCLK,虽然并联在一起,但是由于仅一个输出,多输入。输入引脚的阻抗本来就是高阻,所以不会有问题。

菊花链拓扑

有的芯片支持菊花链拓扑连接,这是何意呢?啥是菊花链呢?在电气和电子工程中,雏菊链是一种布线方案,其中多个设备按顺序或按环连接在一起,类似于雏菊的花环。其信息传递在链中流转。

那么对于SPI总线而言,具体是如何连接的呢?

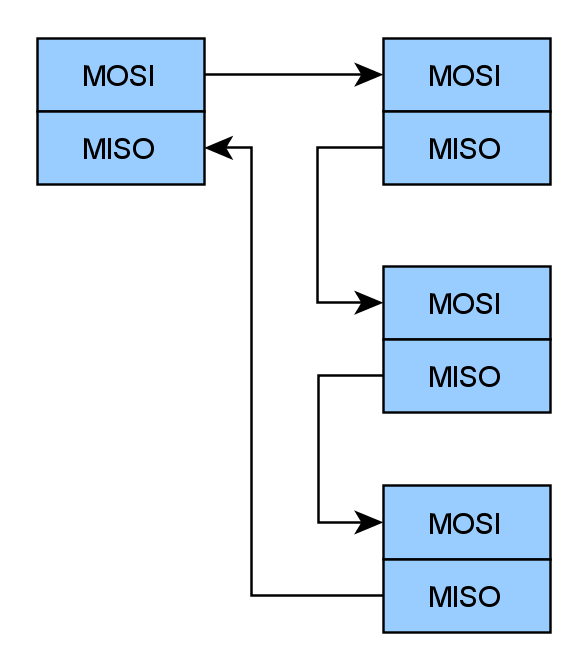

其本质就是主从级联:

- 主MOSI连次级MOSI,次级MISO连次次级的MOSI....,然后由最后一级的MISO再送回到主设备的MISO。

- 某级从设备在第N组时钟周期用MISO发送第N-1组时钟周期接收到位给下级设备,同时把本组时钟周期期间前级设备通过MISO移位进来的数据保存按位序保存进接收寄存器中。其实在底层是按照位进行流转的。这个传递过程当变为高电平时则停止,各从设备当前寄存器中内容锁定了。具体应用时,如果要将某一字节传递到某个设备,则需要组织好传递的码流,以及时钟控制。

- 对于菊花链数据传递过程,其实类似于击鼓传花游戏。鼓点的作用就是同步时钟,花则是要传递的信息数据,鼓点的起停则类似于片选控制,唯一不同的是,击鼓传花传的是一朵花,而菊花链总线传递的是二进制流,至于从设备究竟要怎么应用这些数据流,则具体实现各异。

其实熟悉数据结构的同学可能会想,这个拓扑咋很像首尾相连的环形链表呢?确实很像,虽然没啥直接关系。

引脚的别名

对于SPI的引脚,不同的芯片厂商在DATASHEET上定义的引脚名字可能不同,这里将常见的别名整理一下:

- MOSI主出从入:

- SIMO, MTSR

- SDI, DI, DIN, SI

- SDO, DO, DOUT, SO

- MISO主入从出

- SOMI, MRST

- SDO, DO, DOUT, SO

- SDI, DI, DIN, SI

很多功能芯片可能没有MISO引脚,也即无法支持读操作,仅仅支持写入操作。

SPI优缺点

优势:

- 传输速度高,SPI并未限定最高速度。有的应用甚至高达10Mbps。

- 全双工,但有的芯片没有MISO,则不支持。

- 相较于I2C而言,SPI简单一些,编程容易,控制简单

- 信号为单向信号,易于电隔离。尤其在工业产品中电气隔离在抗干扰方面、以及本质安全方面要求比较高。

- 没有复杂的总线仲裁机制,相对健壮。

劣势:

- 无寻址机制,需要额外的片选信号

- SPI总线对于多从模式支持不好,两种拓扑都无法支持很多从设备,而且系统中也仅有一个主设备

- 没有定义错误检测机制

- 事实上的标准,但无正式标准

- 与I2C一样也只是芯片间总线,无法长距离通信

总结一下

或许有人会说I2C比SPI更好更为优越,SPI则相对简单粗暴。事实上做这样的对比,个人认为是没什么意义。

这两种协议在鲁棒性方面都比较好。I²C之所以优雅,是因为它在极简的基础架构(两线SDA/SCL)上提供了非常先进的功能,例如自动多主机冲突处理和内置地址管理。但是它相对却非常复杂,在性能上或许有所欠缺。

另一方面,SPI非常易于理解和实施,并且为扩展提供了很大的灵活性。SPI的优雅之处在于简单性。SPI应该被视为构建用于IC之间通信的自定义协议栈的良好接口。因此,尽管使用SPI可能需要做更多的工作,但可以提供更高的数据传输性能和灵活的自由度。

如果一定要比较,则SPI和I2C都为低速设备的通信提供了良好的接口支持,但是SPI更适合点对点传输数据流的应用,而I²C则更适合于多主机“寄存器访问”应用。

正确使用这两种协议可提供相同级别的鲁棒性,芯片厂商对两种接口都广泛支持。市面上提供了大量的外围芯片,比如 EEPROM,ADC,DAC,RTC,微控制器,传感器,LCD控制器,这些芯片主要提供I²C,SPI或同时支持这2个接口。

本文辛苦原创总结,如果觉得有价值也请帮忙点赞/转发支持,不胜感激!