来源:知乎

作者: Trustintruth

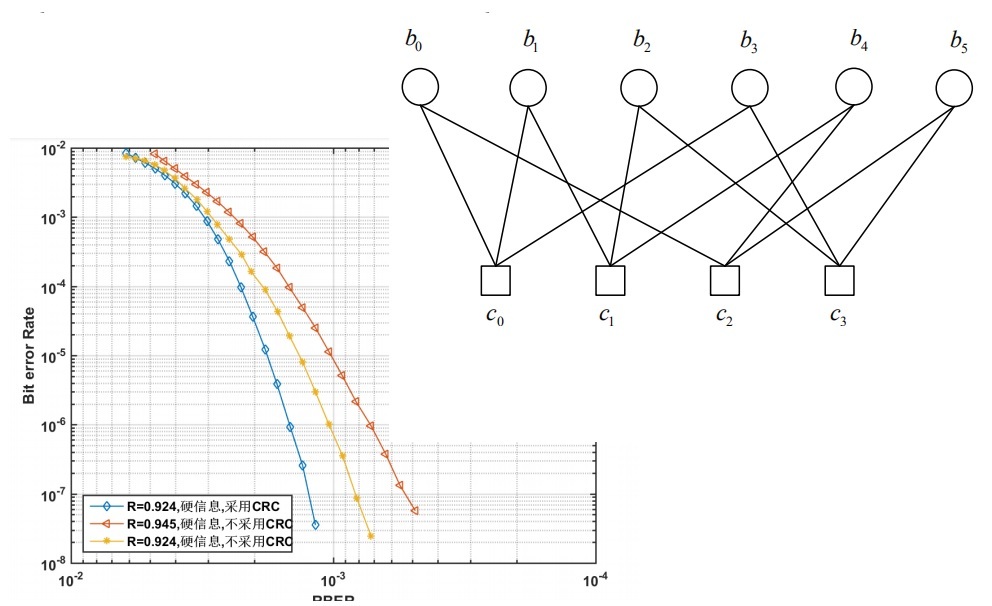

LDPC编码包括编码、RU算法编码、准循环码快速编码等算法。QC-LDPC码结构规律,便于硬件实现。我们根据上回书写到使用基于循环迭代消环的码字构造方法,构造的QC-LDPC码来研究设计ECC模块。

如果生成具有循环形式,编码器硬件上就可以采用简单移位寄存器来实现。我们采用的QC-LDPC码校验矩阵H、生成矩阵G都有循环性。

1.大白话解释

首先我们的选取的校验矩阵和生成矩阵都是循环的,所以在同一矩阵的相邻的两行就可以用移位来解决。在采取分块的方法,将要编码的信息位按照循环矩阵的步长来截成段,对应相乘更加容易。这样讲不清晰,还是来看专业论证。

2.理论论证

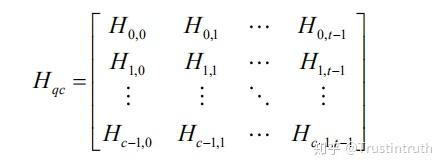

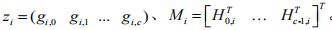

设 QC-LDPC 码的校验矩阵H如公式所示。其中, Hij为零矩阵或者循环矩阵,大小为 L*L。QC-LDPC 的基矩阵大小为 c*t。

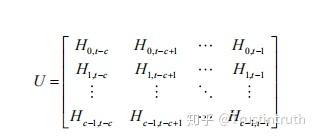

假设矩阵 U表示校验矩阵H中(t-c)列到 _c *L *c *L_列的 矩阵,如公式所示

假设生成矩阵G的第1列到第(t-c)*L列对应信息位,那么生成矩阵具有的形式如下

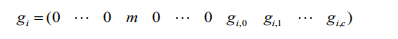

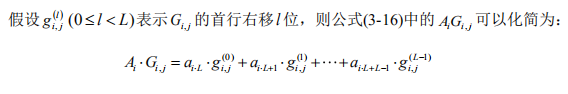

就是矩阵的左半部分是一个单位矩阵,而单位矩阵的大小是信息位的长度。如果我们使用m作为长度为L的第一位为1,其他都是0的元组,即m=(1,0,0,0,0,0,……),那么Gi的第一行为

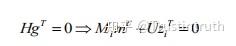

令

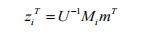

那么

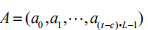

Zi是生成矩阵G中的Gi校验信息部分的第一行。由于G具有循环特性,我们将带编码的信息A

拆分为长度为L的信息段,分为a1,a2......

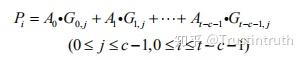

首先我们的编码公式是

X是前面是A也就是信息位,后面连接上的是检验位P,也就是X=(A,P)将P同样分成长度为L的小块,

这样我们的理论论证结束了。

引用文献

周观太. (0)._基于LDPC新型FEC的NAND Flash控制器研究_. (Doctoral dissertation).

相关文章

更多IC设计相关技术干货请关注IC设计专栏。