硅片

硅片:半导体大厦的基石

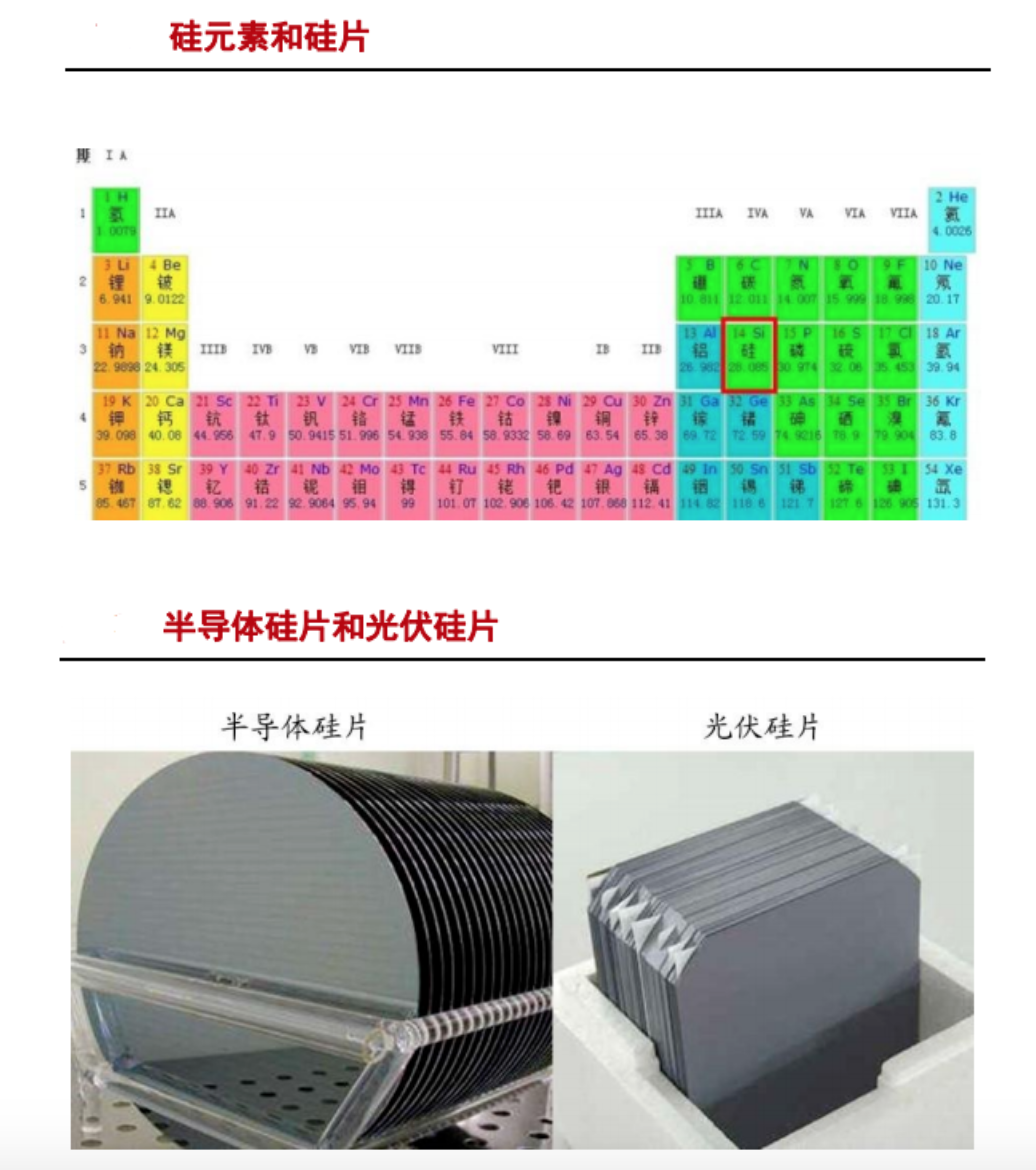

硅片是以硅作为原材料,通过拉单晶制作成硅棒,然后切割而成的硅片。由于硅原子的最外层电子数是4,原子序数适中,所以硅元素具有特殊的化学特性。正是因为硅的这种特性,硅片主要应用在化学,光伏,电子等领域。特别是在电子领域,正是利用硅材料介于导体与绝缘体中间的元素属性,制造了现代工业的“石油”-芯片。在光伏领域,利用光电效应原理,光子可以改变硅原子之间的共价键,从而衍生了太阳能发电的应用。另外地球的地壳中硅元素占比达到25.8%,而且开采较为方便,可回收性强,所以价格比其他材料要低,这样的特点更加增强了硅的应用范围。

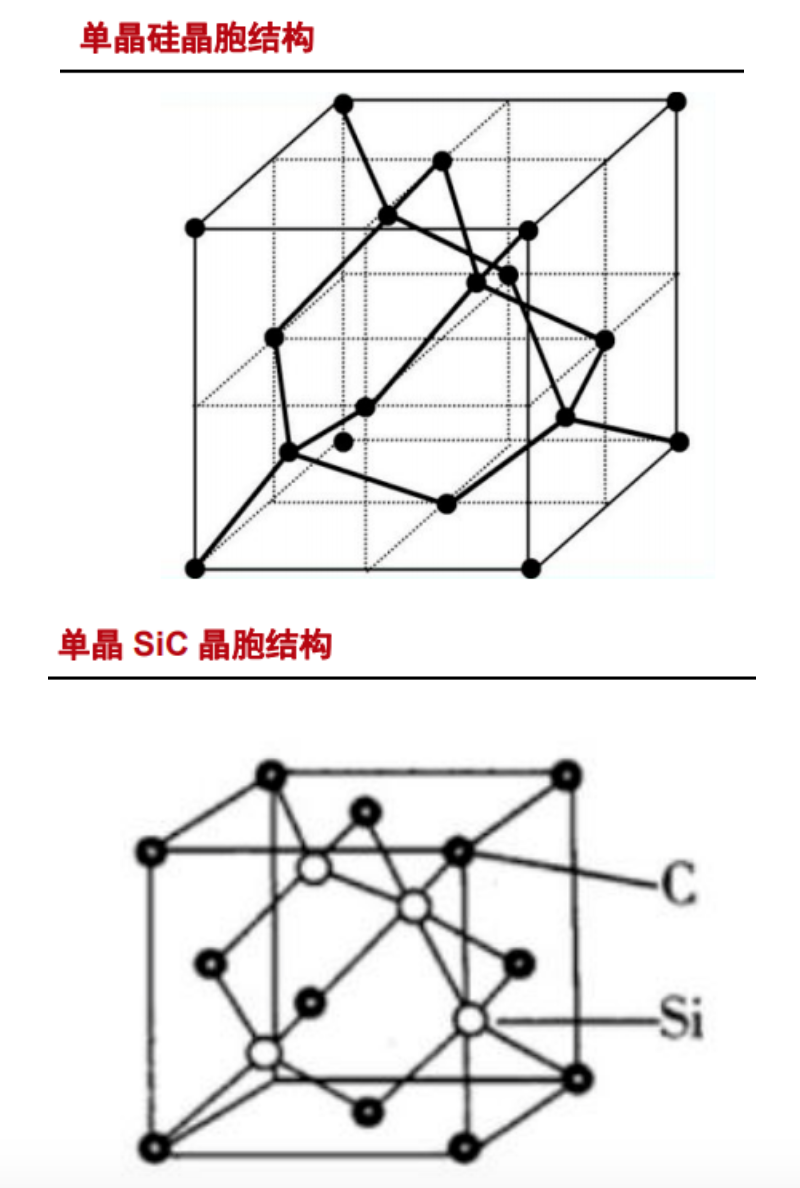

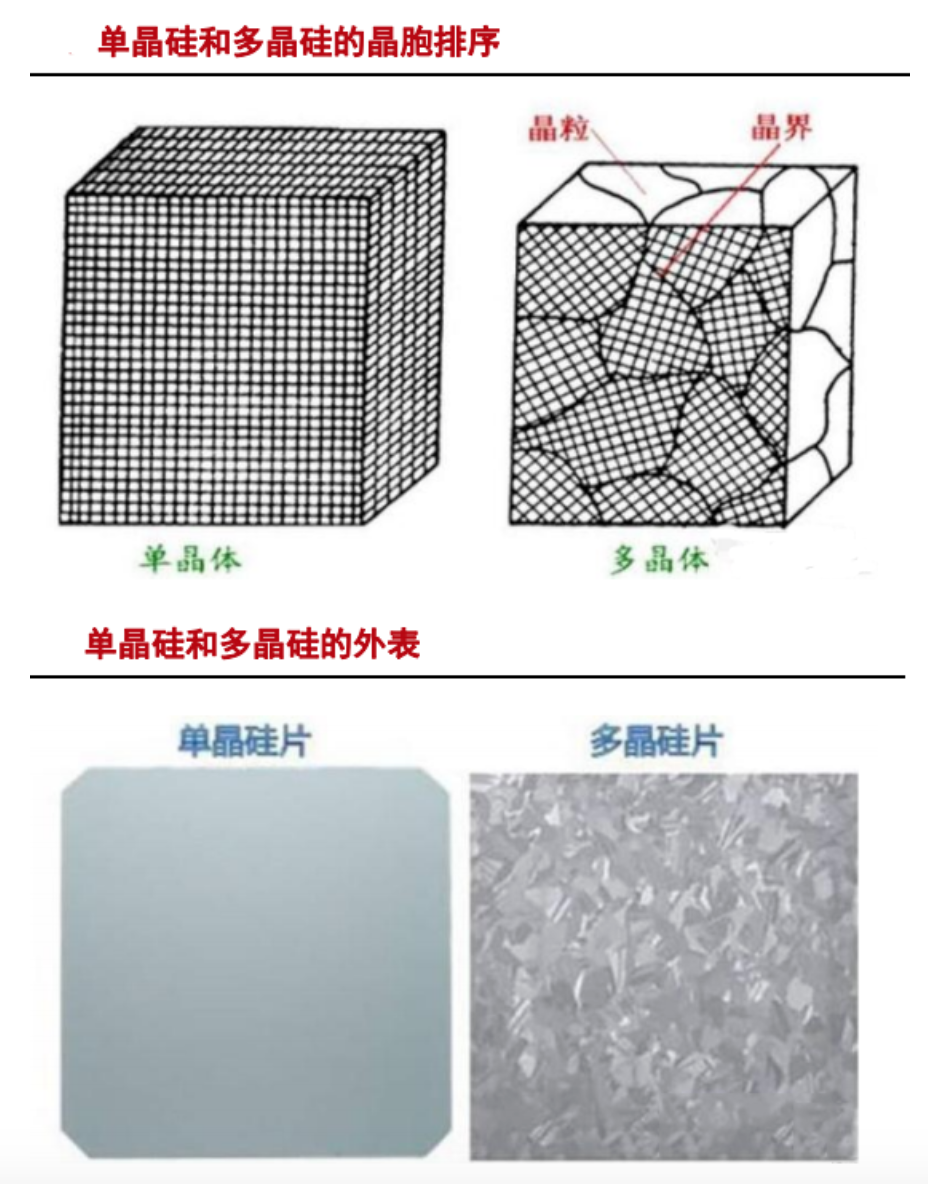

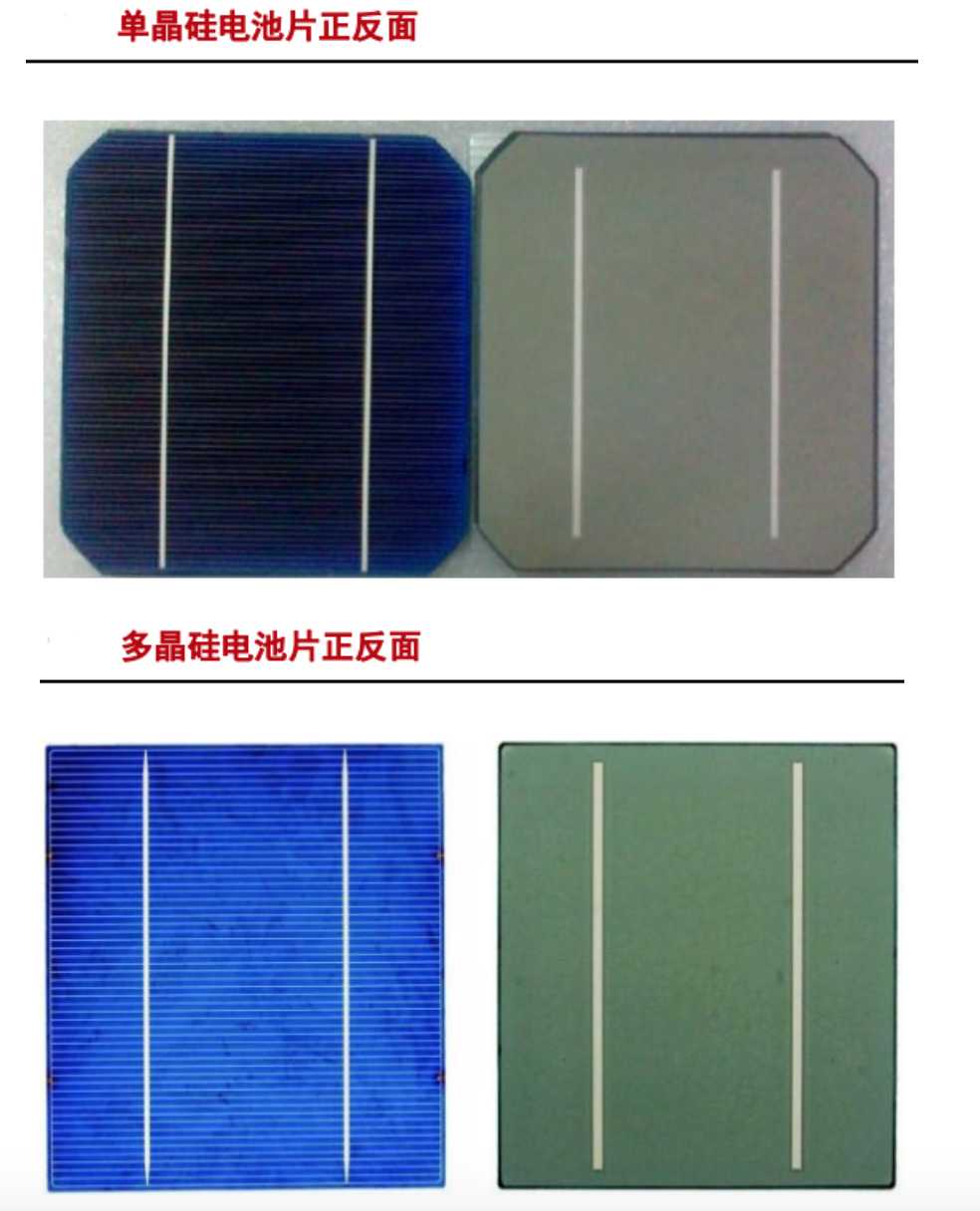

通过晶胞的排列方式不同,可以分为单晶硅和多晶硅。晶胞是自然界构成晶体的最基本单元,一般是由几个原子或几十个原子构成的三维结构。晶胞的形状、大小与空间格子的平行六面体单位相同,保留了整个晶格的所有特征。

单晶硅的晶胞排序方式是有序,有规律的排序。但是多晶硅的晶胞排序是无序,无规律的。在制造方法方面,多晶硅是通过浇筑法形成的,直接把硅料倒入坩埚中融化,然后再冷却定性,这种制作方法形成的晶胞是无序的。单晶硅是通过拉单晶的方式形成晶棒(直拉法),将硅料倒入坩埚中融化,然后利用籽晶缓慢旋转上拉(拉单晶)。拉单晶的过程就是将原子结构重组的过程,最终形成单晶硅棒。在物理性质方面,两种硅的特性相差较大。在导电性质上,单晶硅由于晶胞排序规则有序,导电能力较强;多晶硅导电性很差,甚至有时不导电。在光电转换方面,单晶硅的转换效率高于多晶硅的转换效率,单晶硅光电转换效率一般在17%~25%左右,多晶硅效率在15%以下。

光伏硅片vs半导体硅片

光伏硅片,由于硅元素具有光电效应,所以在光伏领域,大多使用硅片完成太阳能到电能的转换。在光伏领域的硅片,单晶硅电池片一般为圆角方形,颜色为深蓝色,略接近黑色。多晶硅电池片一般为方形,以蓝色和灰色为主,且略带花纹。电池片分为单晶硅片和多晶硅片,单晶硅电池片价格较高,光电转换效率也比较高。

由于光伏硅片相对于半导体硅片在纯度和翘曲度等等方面要求较低,所以光伏硅片制造过程相对简单。以单晶硅电池片为例,第一步是切方磨圆,在晶片厂通过直拉法拉出单晶棒后,先按照晶片尺寸要求,将单晶硅棒切割成方棒,然后将方棒的四角通过滚磨机磨圆。第二步是酸洗,主要是为了将单晶方棒的表面杂质除去。第三步是切片,先将清洗完毕后的方棒与工板粘贴。然后将工板放在切片机上,按照已经设定好的工艺参数进行切割,切割完成后成为单晶硅片。最后将单晶硅片清洗干净(通常用超声波清洗),最后进行监测,比如表面光滑度,电阻率等等参数。

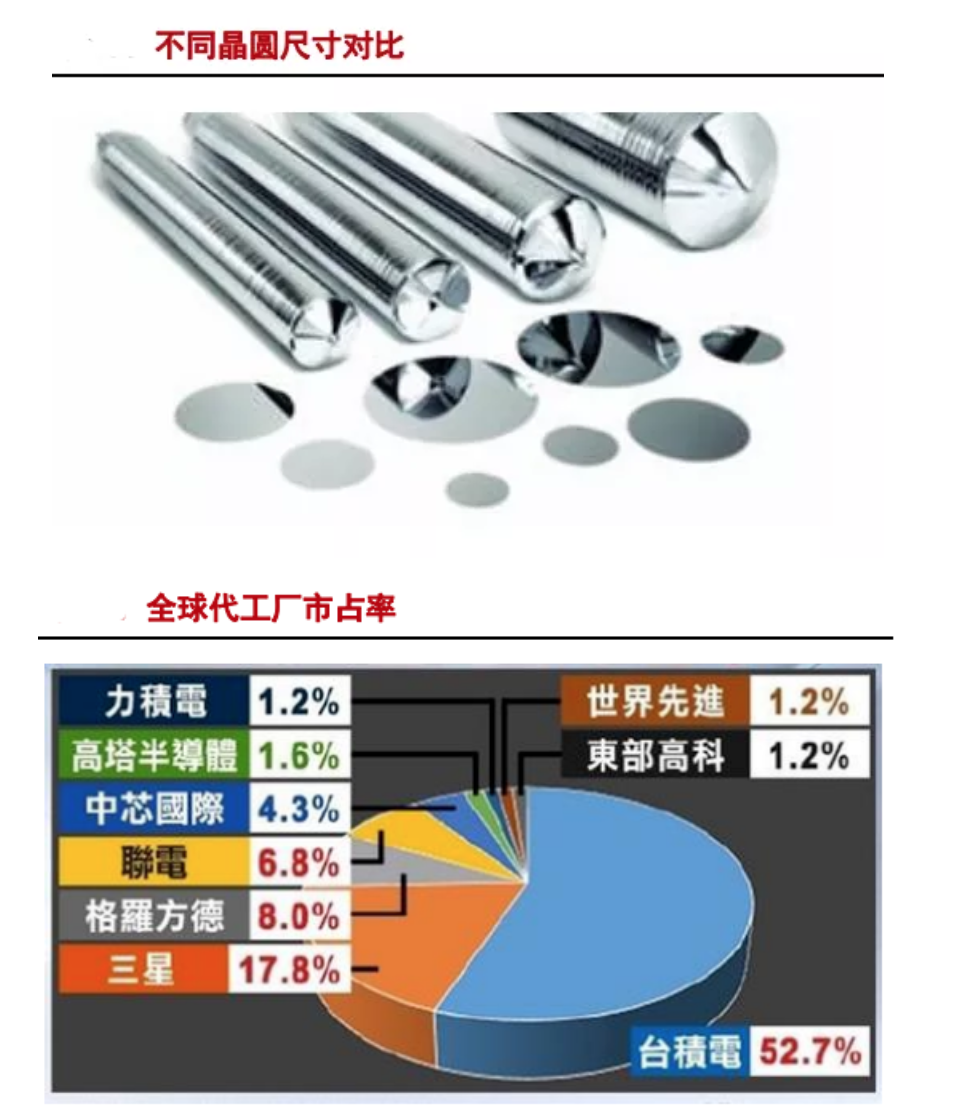

半导体硅片:半导体硅片比光伏硅片的要求更高,通常表现在晶体,形状,尺寸大小,纯度等等方面。光伏单晶硅片是分单晶硅和多晶硅两种类型,其中多晶硅约占60%。但是半导体用单晶硅片,为了硅片每个位臵的相同电学特性,全部使用单晶硅。在形状和尺寸上,光伏用单晶硅片是正方形,边长有125mm,150mm,156mm不同尺寸。但是半导体用单晶硅片是圆型,硅片直径有150mm(6寸晶圆),200mm(8寸晶圆)和300mm(12寸晶圆)尺寸,比单晶硅要大。

在纯度方面,光伏用单晶硅片的纯度要求硅含量为4N-6N之间(99.99%-99.9999%),但是半导体用单晶硅片在9N(99.9999999%)-11N(99.999999999%)左右,纯度要求最低是光伏单晶硅片的1000倍。在外观方面,半导体用硅片在表面的平整度,光滑度和洁净程度要比光伏用硅片的要求高。纯度壁垒是光伏用单晶硅片和半导体用单晶硅片的主要壁垒。

半导体硅片技术发展路径

常用半导体硅片

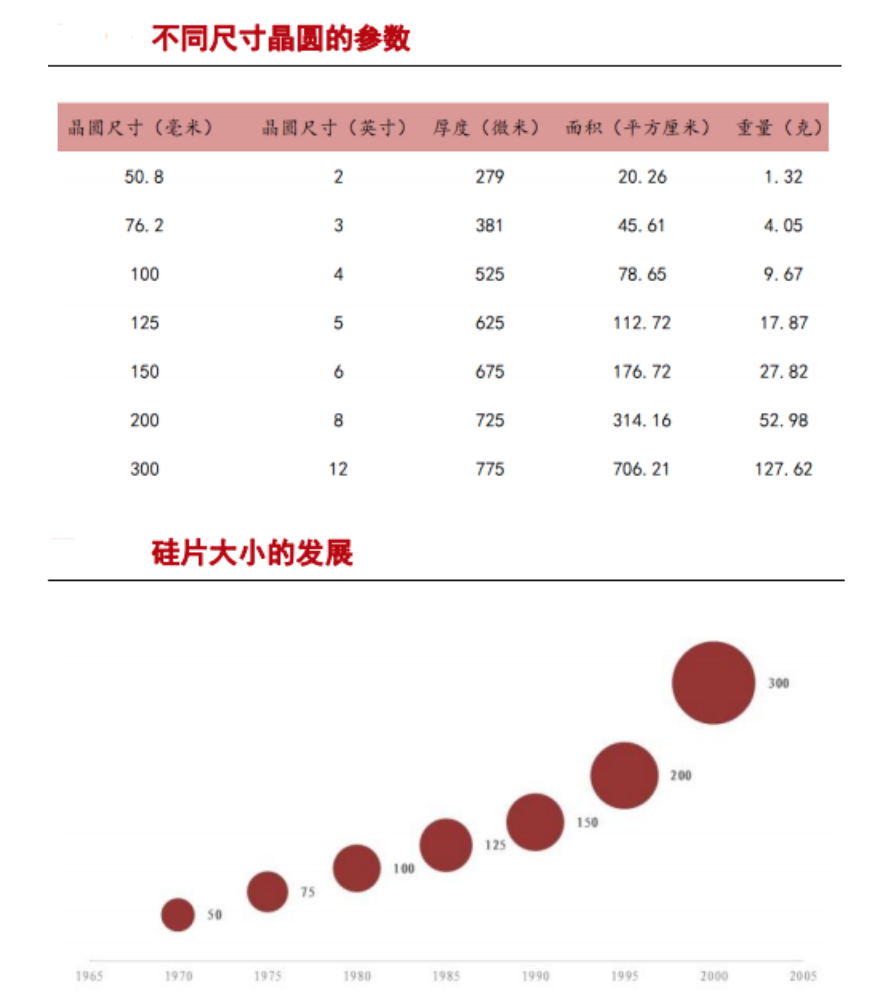

硅片的发展可以归结为摩尔定律的发展。由于半导体用硅片是圆形,所以半导体硅片也叫“硅晶圆”或者“晶圆”。晶圆是芯片制造的“基底”,所有的芯片都是在这个“基底”上制造,并在制造完成后,将基底切割成单个芯片,然后进行封装测试。在半导体用硅片的发展中,是按照尺寸和结构两个方向发展。

在尺寸方面,硅片的发展路径是从小到大;在集成电路发展初期,使用的是0.75英寸晶圆。后来为了降低单个芯片成本,不断增加晶圆面积,增加单片晶圆上的芯片个数。1965年左右,随着摩尔定律的提出,集成电路技术和硅片迎来快速发展期。硅片的制造技术越来越先进,逐渐发展到4寸,6寸,8寸和12寸晶圆。2001年,英特尔和IBM联合开发了12寸晶圆芯片制造生产线,目前全球半导体用硅片以12寸硅片为主,占比约为70%,往后还要发展到18寸(450mm)晶圆。

在结构方面,硅片的发展路径是由简到繁;集成电路发展初期是只有逻辑芯片一种用途,但是后来应用场景不断扩大,逻辑芯片,功率器件,模拟芯片,数模混合芯片,flash/Dram存储芯片,射频芯片等等。不同的应用场景导致了硅片在结构上出现了不同的形态。

PW(Polish Wafer):就是常用的抛光片。硅片厂拉单晶得到硅锭之后,直接切割后得到的硅片由于在光滑度或者翘曲度方面有一些瑕疵,所以首先是经过抛光处理。这种方式也是最原始硅片的处理方式。

AW(Anneal Wafer):后来随着制程技术的不断发展,工艺线宽不断缩小,抛光片的缺点也暴露出来了,比如硅片表面由于抛光会引起局部的原子晶格缺陷,硅片表面含氧量较高等等。为了解决这个问题,发展了退火晶圆,在抛光后,将硅片放在充满惰性气体的炉管中(一般为氩气),进行高温退火。这样可以修复由于抛光引起的硅片表面晶格缺陷,同时也可以减少硅表面含氧量。

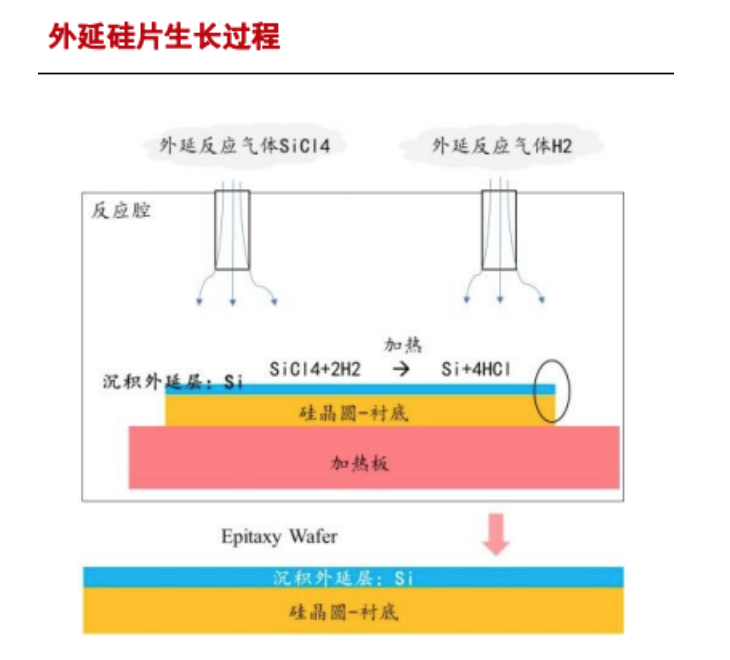

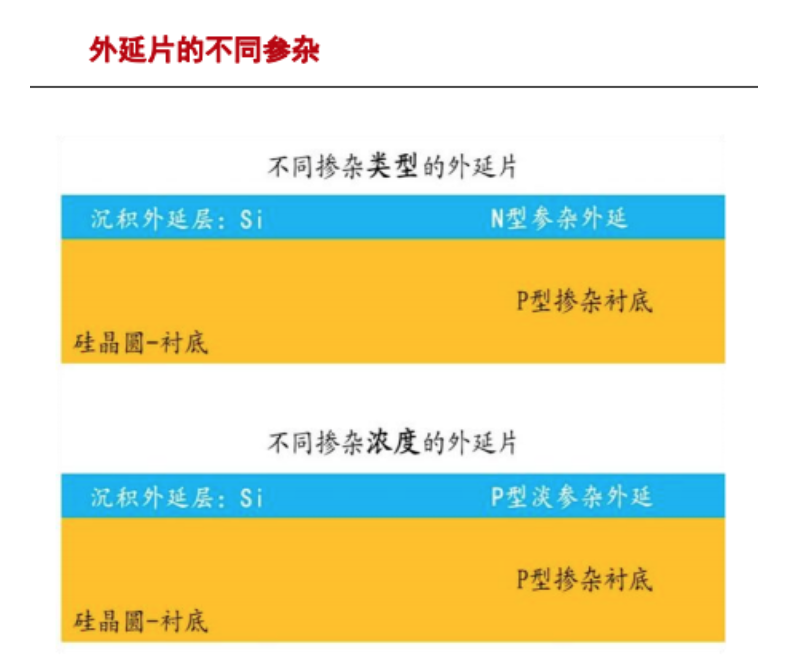

EW(Epitaxy Wafer):随着集成电路的应用场景不断增加,由硅片厂制造的标准硅片在电学特性上已经不能满足某些产品的要求。同时,通过热退火减少的晶格缺陷也不能满足越来越小的线宽需求。这就衍生出了外延层硅片(Epitaxy wafer或者叫做EPI Wafer)。通常的外延层就是硅薄膜。是在原始硅片的基础上,利用薄膜沉积技术,生长一层硅薄膜。由于在硅外延中,硅基片是作为籽晶的模式存在,所以新的外延层会复制硅片的晶体结构。由于衬底硅片是单晶,所以外延层也是单晶。但是由于没有被抛光,所以生长完成后的硅片表面的晶格缺陷可以降到最低。

外延技术的重点包括外延层厚度及其均匀性、电阻率均匀性、体金属控制、颗粒控制、层错、位错等缺陷控制。公司通过优化外延的反应温度、外延气体的流速、中心及边缘的温度梯度,实现了最优的外延层质量。因产品不同和技术升级的需要,公司通过不断优化外延工艺,实现外延层厚度和衬底几何形貌的有效匹配,获得外延层最优的平坦度、最低的外延层金属杂质、最好的厚度和电阻率均匀性,达到不同规格产品的需求。

另外,外延片可以生成电阻率,掺杂元素、掺杂浓度与原始硅片不同的外延层,这样更容易控制硅片的电学特性。比如可以通过在P型硅片上生成一层N型外延层,这样就形成了一个低浓度参杂的PN结,为后续芯片制造中起到优化击穿电压,降低闩锁效应等等目的。外延层厚度一般根据使用场景不同而不同,一般逻辑芯片的厚度为0.5微米到5微米左右,功率器件由于需要承受高电压,所以厚度为50微米到100微米左右。

绝缘体上硅硅片

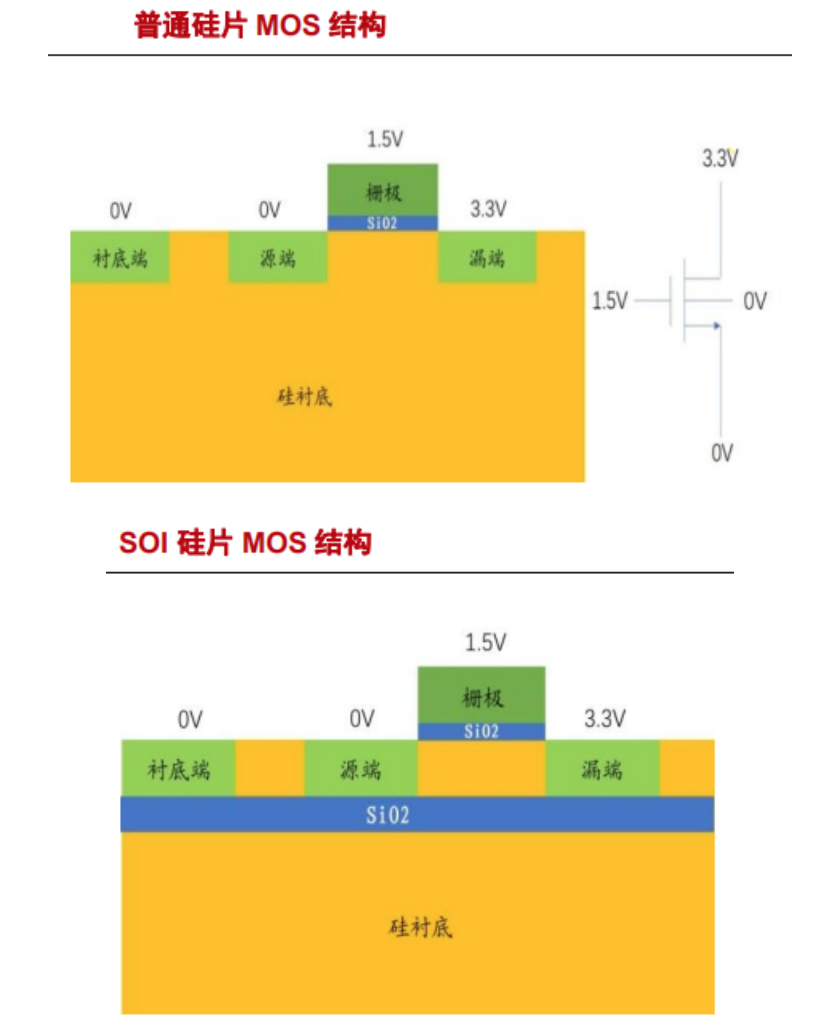

SW(SOI Wafer):SOI 全称是Silicon-On-Insulator(绝缘体上硅)。由于SOI硅片具有寄生电容小,短沟道效应小,继承密度高,速度快,功耗低等有点,特别是在衬底噪声低这向参数中,由于非SOI硅片,所以SOI硅片常常用在射频前端芯片中。

在常用的普通抛光硅片或者是外延层硅片中,都不能解决硅片的噪电流干扰。由于集成电路是四端器件,必须在衬底上结电压,所以就构成了芯片与衬底之间的电流通路,就会产生噪电流,从而影响集成电路特性。特别是在射频 芯片领域中,开关速度较快,衬底产生的噪电流会严重影响开关性能。为了解决衬底噪声问题,发明了SOI硅片技术。

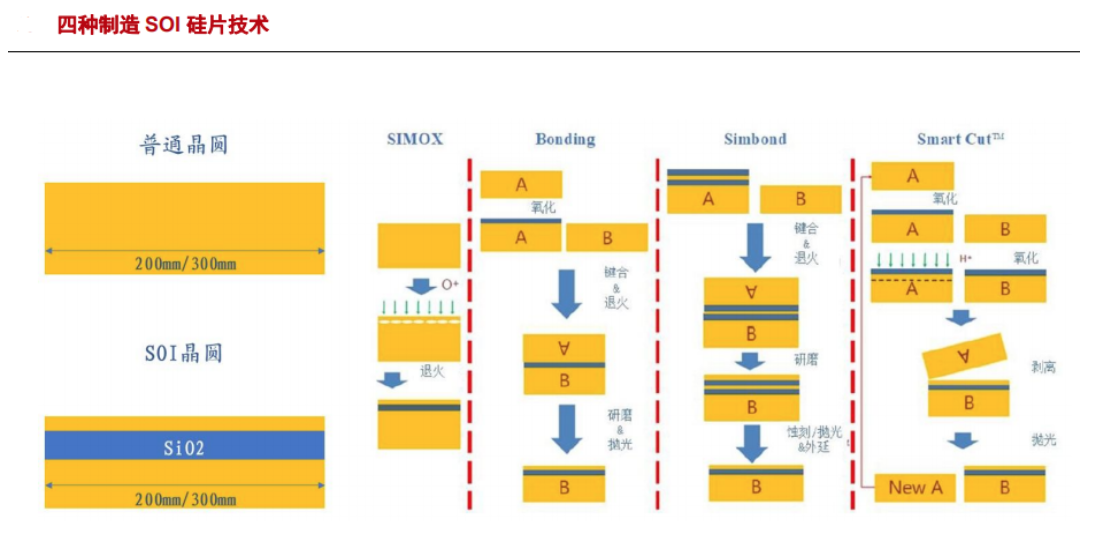

制造SOI硅片的方法主要有四种:SIMOX技术,Bonding技术,Sim-bond技术和Smart-CutTM技术;SOI硅片的原理比较简单,核心目标就是在衬底中间加入一层绝缘层(一般以二氧化硅SiO2为主)。

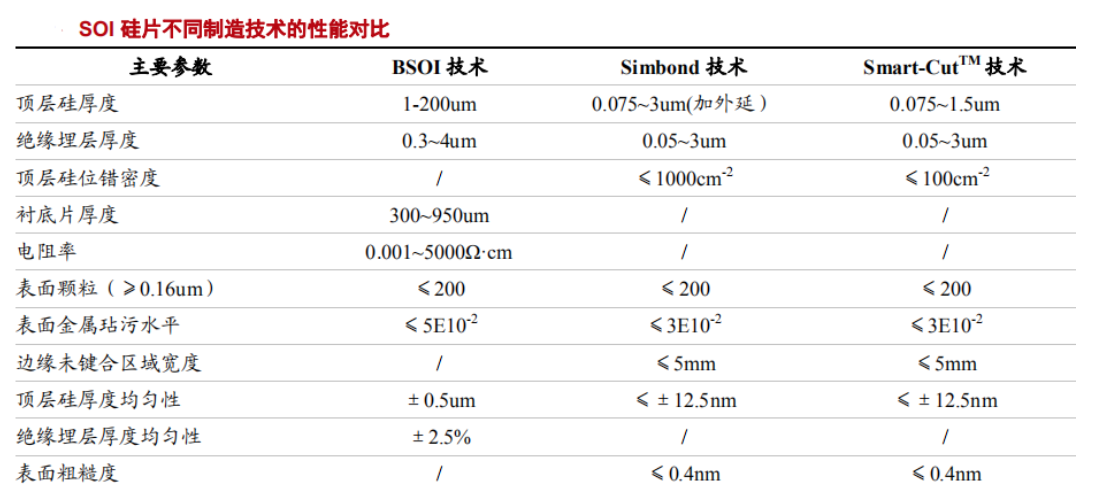

从性能参数上来看,Smart-CutTM技术是现在SOI硅片技术中性能最优异的。Simbond技术性能和Smart-Cut技术性能相差不大,但是在顶层硅厚度方面,Smart-Cut技术生产的SOI硅片更薄,而且从生产成本来说,Smart-Cut技术可以重复利用硅片,对于未来的大批量生产情况,Smart-Cut技术更有优势,所以现在业界公认以Smart-Cut技术为未来SOI硅片发展方向。

SIMOX技术:SIMOX全称Separation by Implanted Oxygen(注氧隔离技术)。向晶圆中注入氧原子,然后经过高温退火,使氧原子与周围的硅原子发生反应,生成一层二氧化硅。此项技术的难点是控制氧离子注入的深度与厚度。对于离子注入技术有较深刻的掌握。

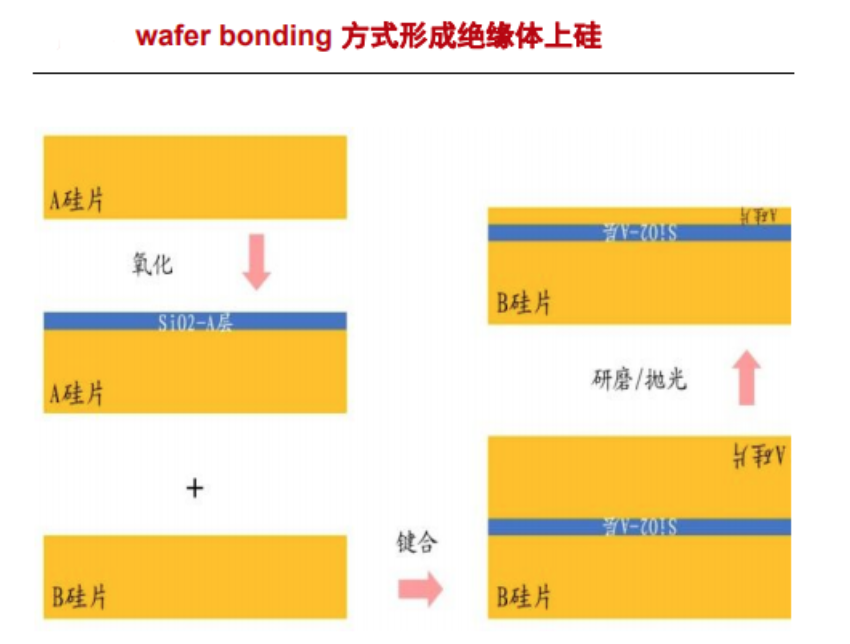

Bonding技术:Bonding技术又称键合技术,用bonding制造的SOI硅片又叫Bonded SOI,简称BSOI。Bonding技术需要两片普通硅晶圆,在其中一片上生长一层氧化层(SiO2),然后与另外一片硅源键合,连接处就是氧化层。最后再进行研磨和抛光到想要的填埋层(SiO2)深度。由于键合技术比离子技术更容易掌握,所以目前SOI硅片大都采用bonding技术制作。

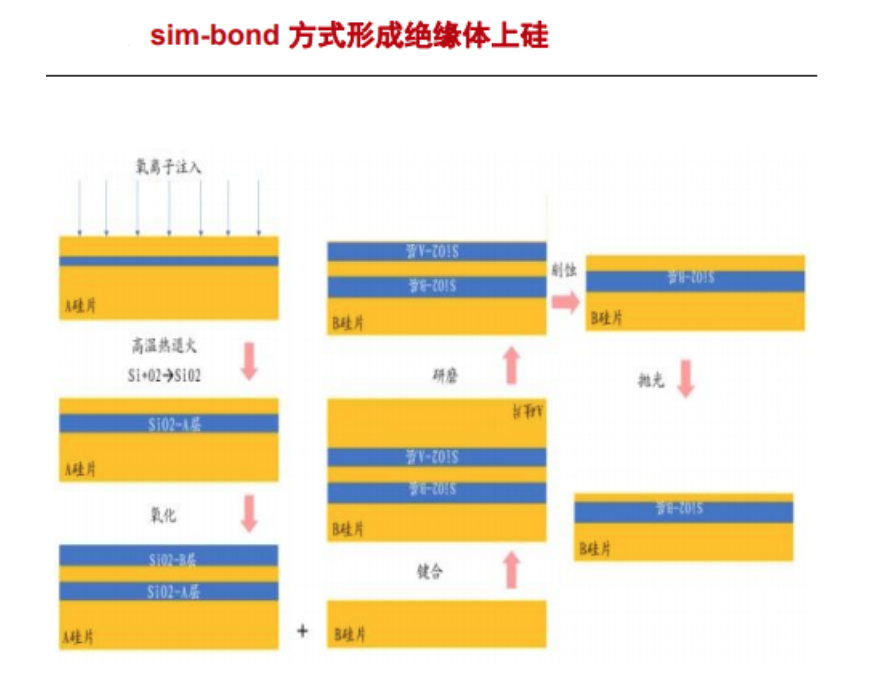

Sim-bond技术:注氧键合技术。Sim-bond技术是SIMOX与bond技术的结合。优点是可以高精度控制埋氧层厚度。第一步是向一片硅晶圆注入氧离子,然后高温热退火形成氧化层,然后在该硅片表面形成一层SiO2氧化层。第二步是将该硅片与另外一片晶圆键合。然后进行高温退火形成完好的键合界面。第三步,减薄工艺。利用CMP技术减薄,但是与bond技术不同的是,sim-bond有自停止层,当研磨到SiO2层时,会自动停止。然后经过腐蚀去掉SiO2层。第四步是抛光。

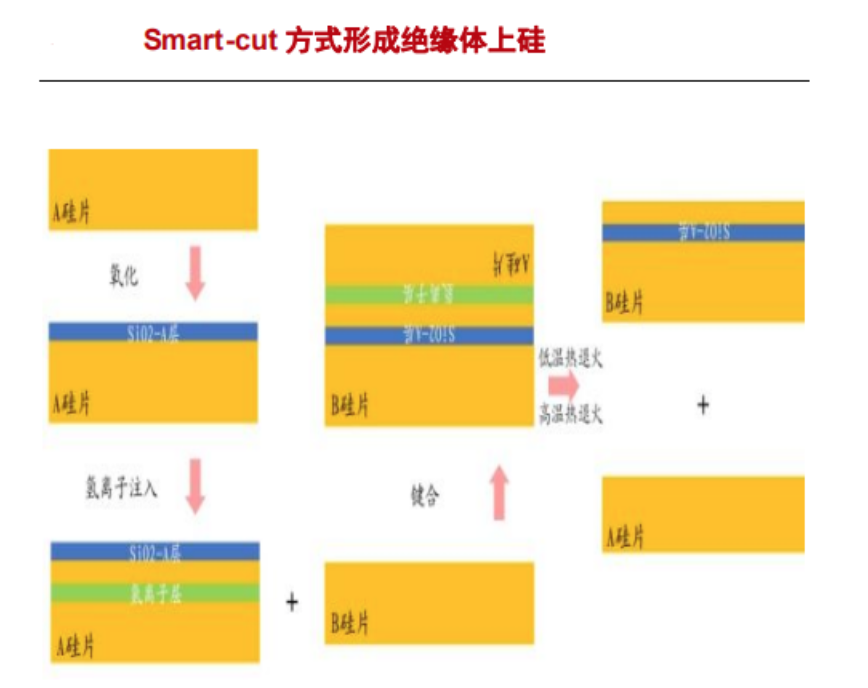

Smart-cut技术:智能剥离技术。Smart-cut技术是键合技术的一种延伸。第一步是将一片晶圆氧化,在晶圆表面生成固定厚度的SiO2。第二步是利用离子注入技术,向晶圆的固定深度注入氢离子。第三步是将另外一片晶圆与氧化晶圆键合。第四步是利用低温热退火技术,氢离子形成气泡,令一部分硅片剥离。然后利用高温热退火技术增加键合强度。第五步是将硅表面平坦化。这项技术是国际公认的SOI技术发展方向,埋氧层厚度完全由氢离子注入深度决定,更加准确。而且被剥离出的晶圆可以重复利用,大大降低了成本。

硅片:制造难度大且壁垒高

硅片制造技术过程

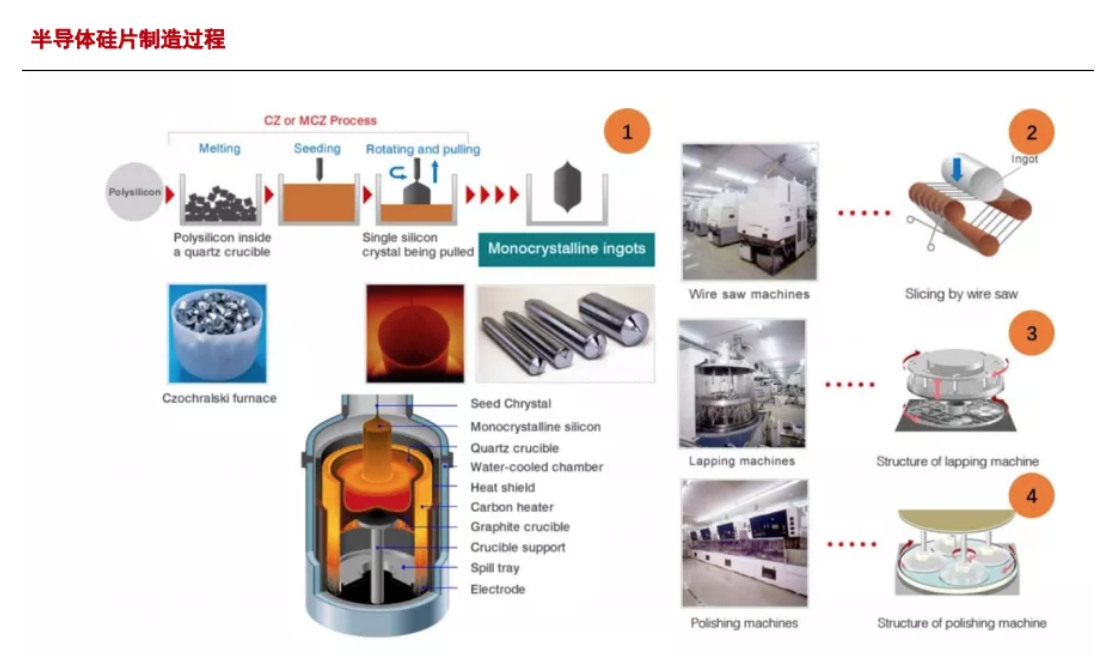

硅片的原材料是石英,也就是通常说的沙子,可以直接在自然界开采。晶圆制造的过程可以通过几步来完成。脱氧提纯,提炼多晶硅,单晶硅锭(硅棒),滚磨,晶片切割,晶圆抛光,退火,测试,包装等等步骤。

脱氧提纯:硅片制造厂的原料是石英矿石,石英矿石的主要原料是二氧化硅(SiO2)。首先将石英矿石进行脱氧提纯,主要工艺有分选,磁选,浮选,高温脱气等等。主要将矿石中的主要杂质去除掉,比如铁、铝等杂质。

提炼多晶硅:在得到相对较纯的SiO2后,经过化学反应,生成单晶硅。主要反应为SiO2+CSi+CO,一氧化碳(CO)为气体,反应完成后直接挥发掉。所以只剩下硅晶体。此时的硅为多晶体硅,并且为粗硅,存在一些杂质比如铁,铝,碳,硼,磷,铜等等元素。为了过滤掉多余杂质,必须将得到的粗硅进行酸洗,常用的酸是盐酸(HCl),硫酸(H2SO4)等等,用酸浸泡后的硅含量一般在99.7%以上。在酸洗的过程中,虽然将铁,铝等等元素也溶于酸且过滤掉。但是硅也和酸反应生成SiHCl3(三氯氢硅)或SiCl4(四氯化硅)。但是这两种物质都是气态,所以酸洗过后,原来的铁、铝等杂质已经溶于酸,但是硅已经变为气态。最后将高纯的气态SiHCl3或者SiCl4用氢气还原得到高纯多晶硅,SiHCl3+H2Si+3HCl,SICl4+2H2Si+4HCl。此时得到生产用的多晶硅。

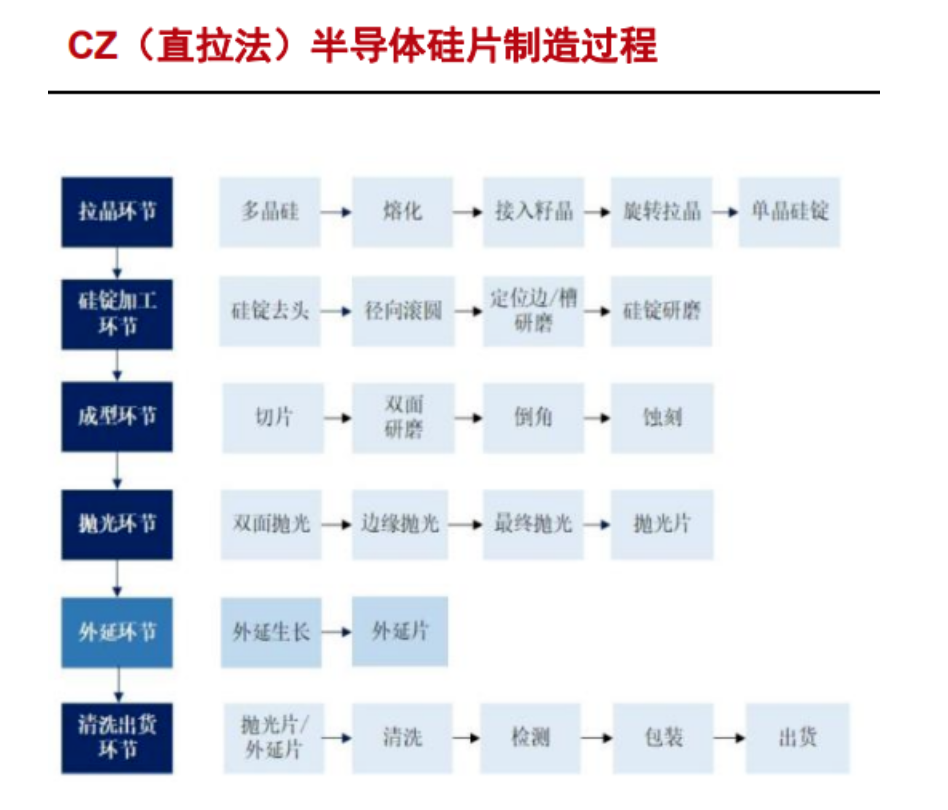

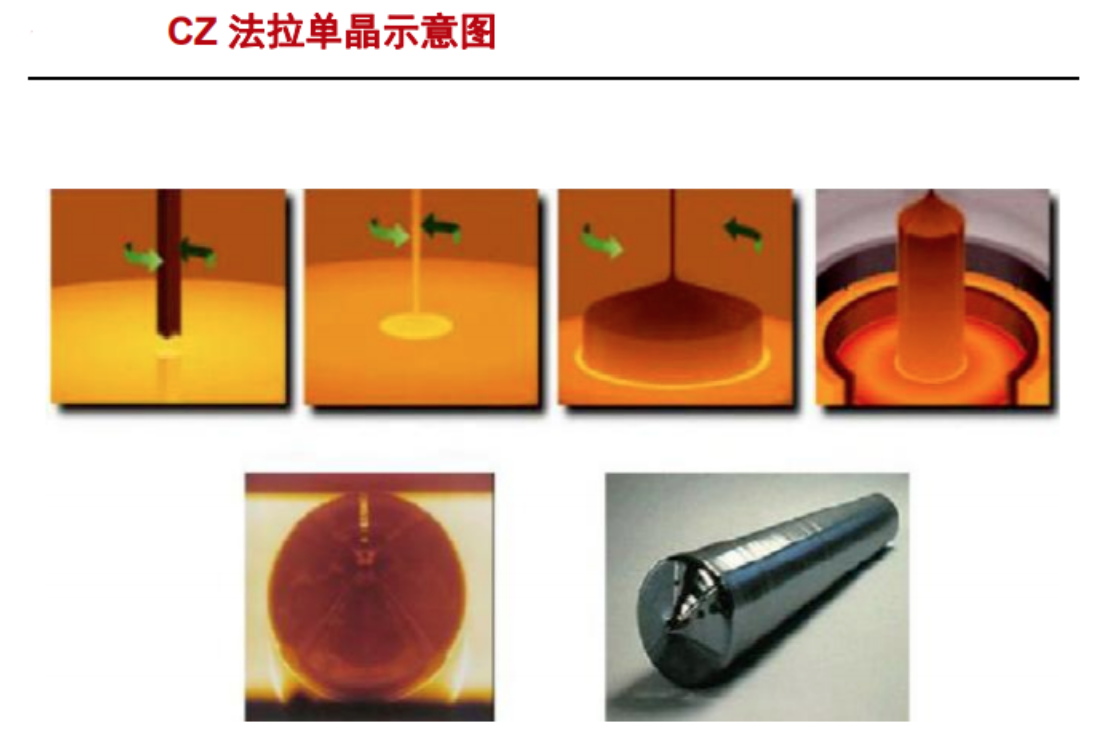

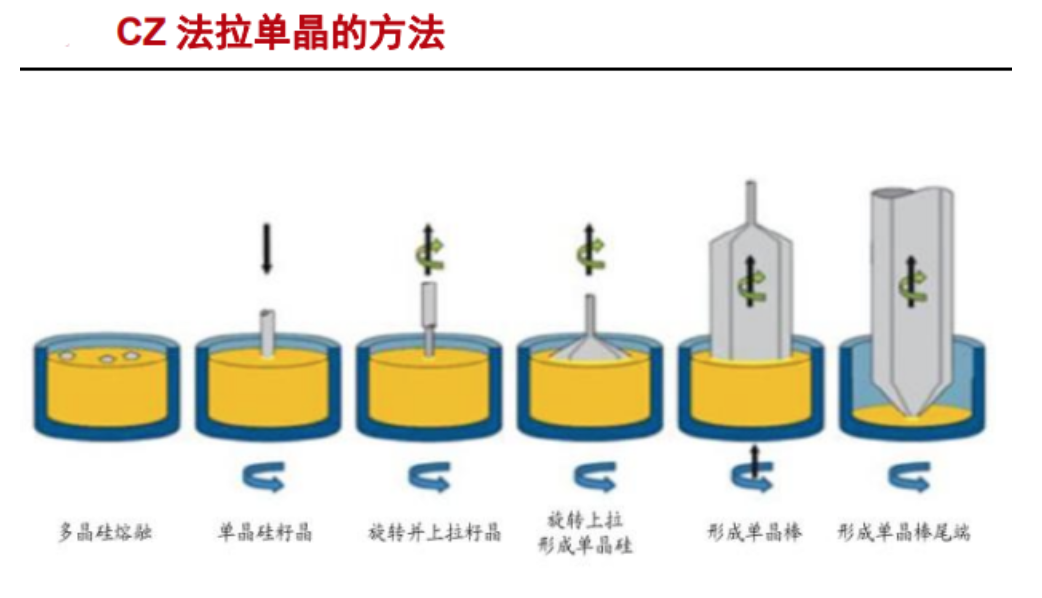

CZ(直拉法)

直拉法(CZ)法硅片主要用在逻辑,存储器芯片中,市场占比约为95%;直拉法最早起源于1918年Czochralski从熔融金属中拉制细灯丝,所以又叫CZ法。这是当今生长单晶硅的主流技术。主要流程是在坩埚中放入多晶硅,加热使之熔融,然后夹住一块单晶硅的籽晶,将它悬浮在坩埚之上,直拉时,一端插入熔体直到融化,然后再缓慢旋转并向上提拉。这样在液体与固体的界面就会经过逐渐冷凝形成单晶。由于整个过程可以看作是复制籽晶的过程,所以生成的硅晶体是单晶硅。另外,晶圆的掺杂也是在拉单晶的过程中进行的,通常有液相掺杂和气相掺杂两种。液相掺杂就是指在坩埚中参杂P型或者N型元素,在拉单晶的过程中,可以直接将这些元素拉到硅棒中。

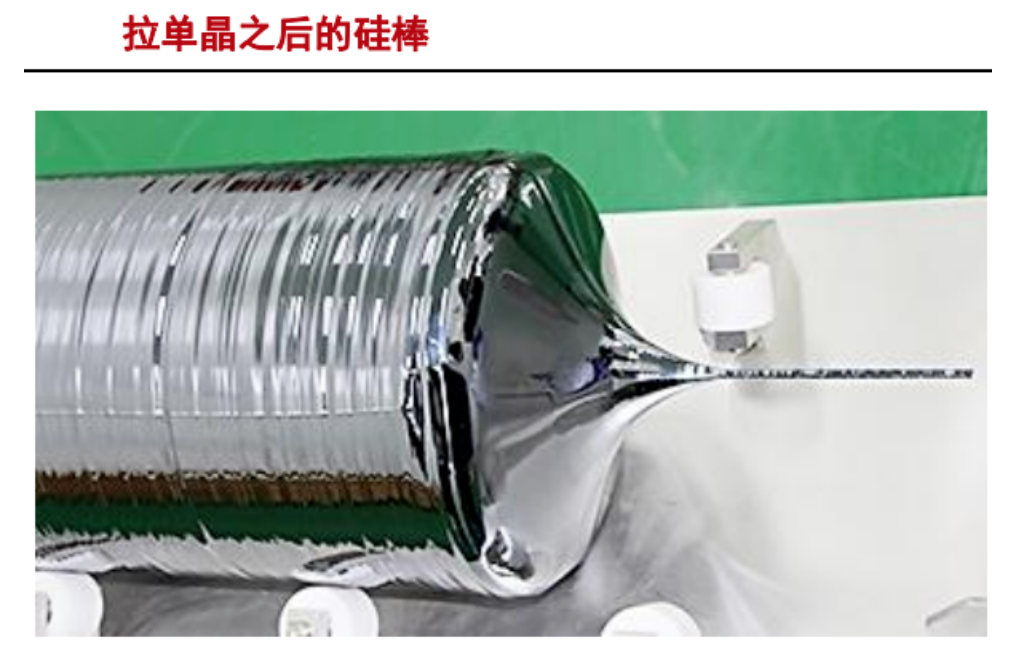

直径滚磨:由于在拉单晶的过程中,对于单晶硅棒的直径控制较难,所以为了得到标准直径的硅棒,比如6寸,8寸,12寸等等。在拉单晶后会将硅锭直径滚磨,滚磨后的硅棒表面光滑,并且在尺寸误差上更小。

切割倒角:在得到硅锭之后,就进行晶圆切割,将硅锭放臵在固定切割机上,按照已经设定好的切割程式进行切割。由于硅片的厚度较小,所以切割后的硅片边缘非常锋利。倒角的目的就是形成光滑的边缘。倒角后的硅片有较低的中心应力,因而使之更牢固,并且在以后的芯片制造中不容易碎片。

抛光:抛光的主要目的是将晶圆的表面变得更加平滑,平整无损伤,并且保证每片晶圆的厚度一致性。

测试包装:在得到抛光好的硅片后,需要对硅片的电学特性进行测试,比如电阻率等等参数。大部分硅片厂都有外延片服务,如果需要外延片,再进行外延片生长。如果不需要外延片就会打包包装,运往其他外延片厂或者晶圆厂。

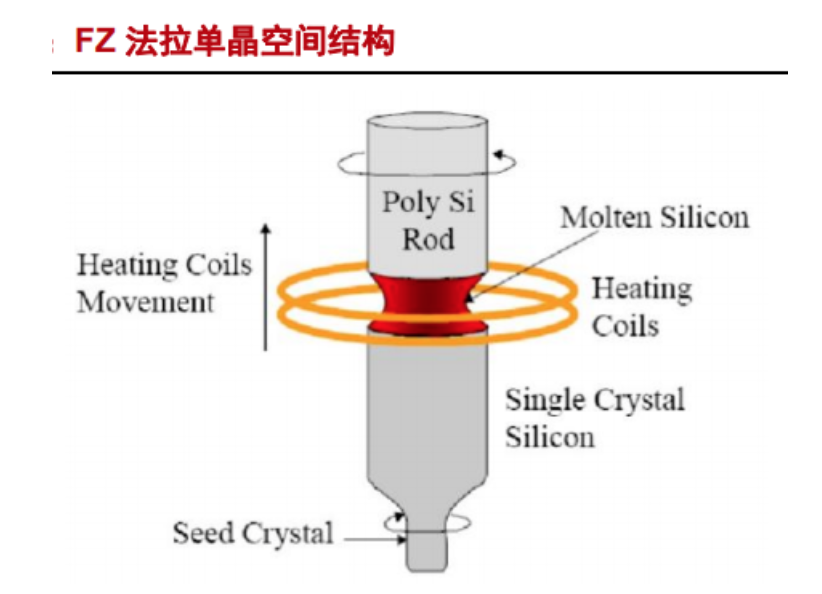

FZ(区熔法)

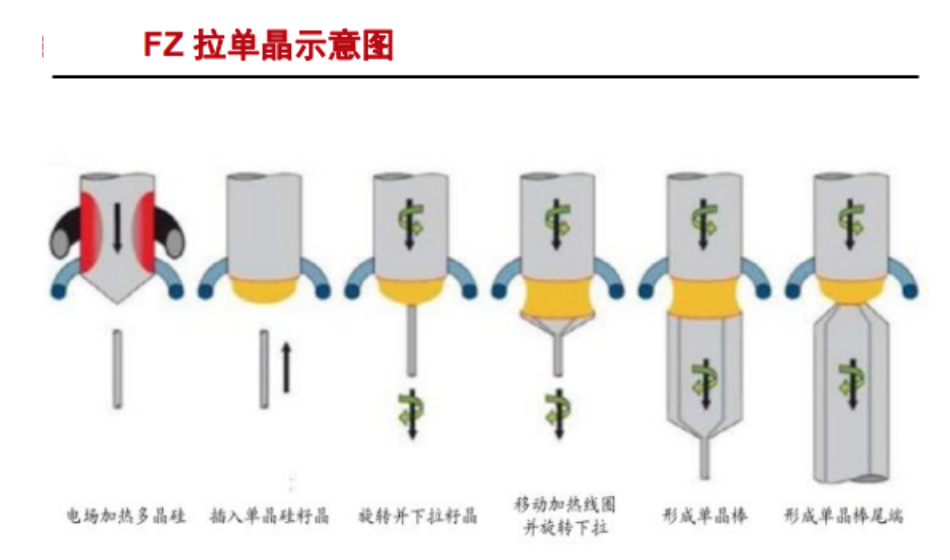

区熔法(FZ)硅片主要用在部分功率芯片中,市场占比约为4%;用FZ(区熔法)制作的硅片主要用作功率器件。并且硅片尺寸以8英寸,6英寸为主,目前约有15%的硅片使用区熔法制作。与CZ法制作的硅片相比,FZ方法最大的特点就是电阻率相对较高,纯度更高,能够耐高压,但是制作大尺寸晶圆较难,而且机械性质较差,所以常常用于功率器件硅片,在集成电路中使用较少。

区熔法制作单晶硅棒总共分为三步:加热多晶硅,籽晶接触,向下旋转拉单晶。在真空或者惰性气体环境下的炉室中,利用电场给多晶硅棒加热,直到被加热区域的多晶硅融化,形成熔融区。然后用籽晶接触熔融区,并融化。最后通过移动电场加热位臵,使多晶硅上的熔融区不断上移,同时籽晶缓慢旋转并向下拉伸,逐渐形成单晶硅棒。因为在区熔法中不适用坩埚,所以避免了很多污染源,用区熔法拉的单晶具有纯度高的特点。

硅片制造成本分析

新能源硅片制造成本

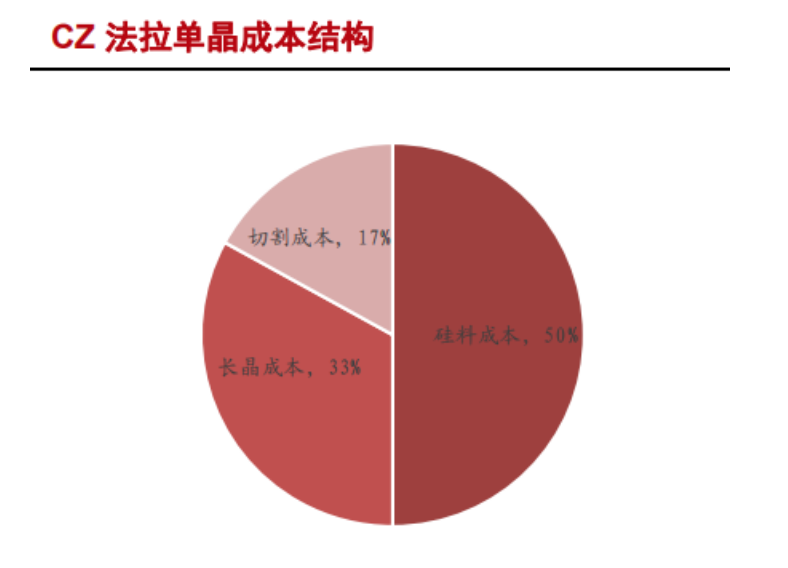

光伏硅片成本大概可以分为硅料成本,长晶成本和切割成本。其中硅料成本是主要的成本消耗部分,约占总成本的50%。由于单晶硅和多晶硅对于长晶过程的要求不同,所以在长晶过程是单晶硅片和多晶硅片的主要成本差别。在切片环节,硅片制造商可以提高硅片的切割出片量来分摊成本。在长晶过程中的设备、电费、特气以及人工费用等等。

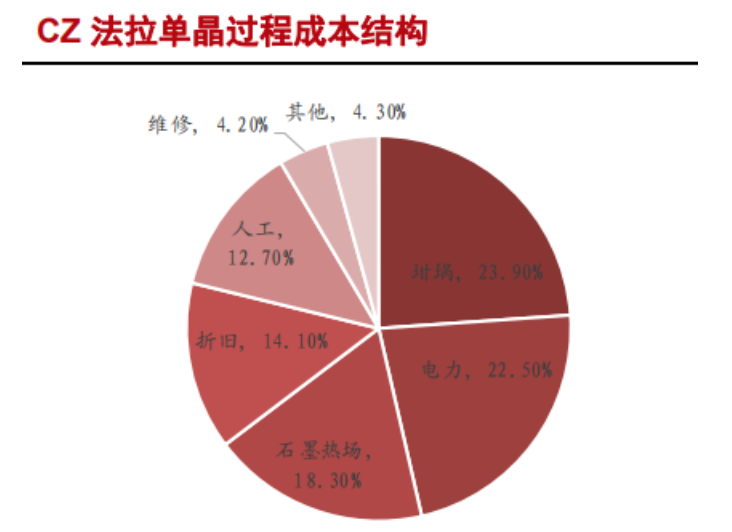

单晶硅制造成本:在硅成本和切片方面,单晶硅和多晶硅的差别不是很大。长晶环节是主要的成本差异。从单晶硅片的成本结构来看,硅料成本约占50%,拉单晶硅棒的成本约占整个成本的33%,切割成本约占17%。在拉单晶过程中的成本结构中,以坩埚费用和电费为主要成本来源,两者总共占比约为45%。剩余成本由石墨热场和折旧费用为主。

在坩埚成本方面,拉单晶的石英坩埚在经过高温、冷却等等步骤之后,会产生裂纹或者破裂,导致无法再次使用。并且,由于拉单晶对于坩埚的洁净度要求很高,所以使用过的坩埚无法保证洁净度,同时单晶硅对于坩埚的品质要求较高。所以拉单晶的坩埚价格较高,且无法重复使用。在电力成本方面,国内半导体硅片厂商或者光伏硅片厂商都在内蒙古,云南,贵州等电力成本相对较低的区域建厂,有利于成本降低。单晶硅片的成本降低主要来源于三个方面。第一,提高单炉产出摊薄坩埚等一次性耗材和设备折旧。第二,电力成本降低。第三,批量采购硅料的价格优势。

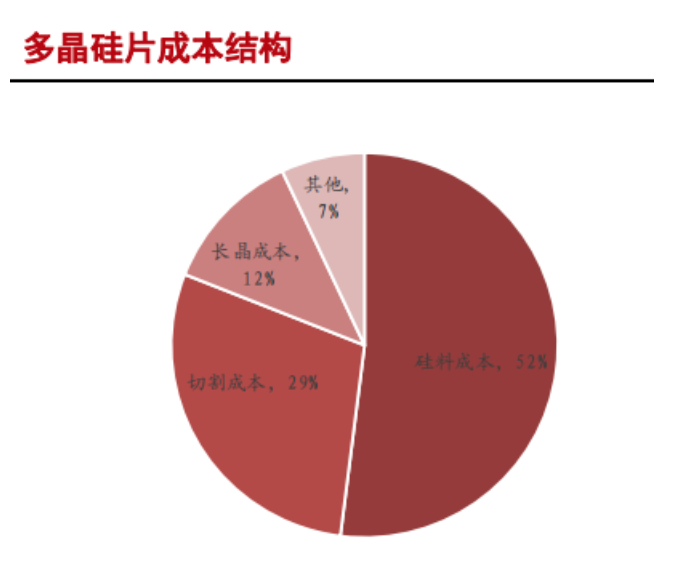

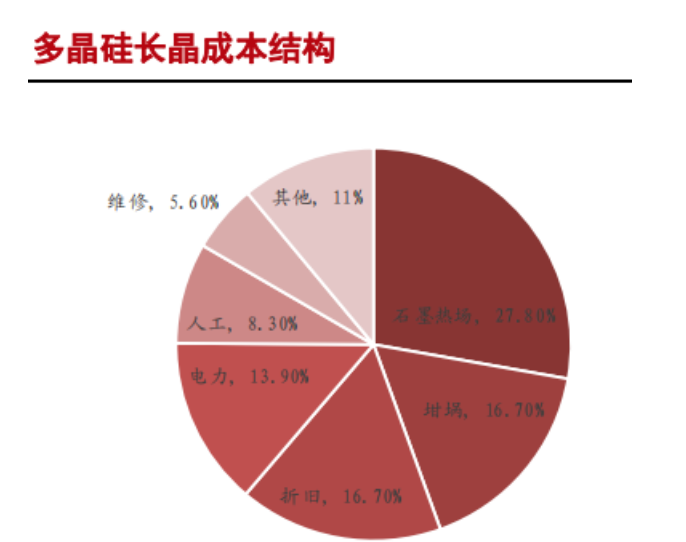

多晶硅制造成本:多晶硅的生产制造过程中不需要拉单晶环节,所以长晶环节的成本占比较低。长晶成本只占总成本的12%。成本的主要来源是硅料成本,约占总成本的52%。其次是切割成本,约占总成本的29%。在多晶硅长晶成本中,石墨热场占比最高,达到28%。其次是坩埚、折旧和电力成本,分别占比为16.7%、16.7%和13.9%。由于多晶硅硅片主要用在光伏产品中,而且有逐渐被单晶硅片代替的趋势,所以多晶硅片的成本下降空间不大。

半导体硅片制造成本

半导体硅片成本构成更复杂:半导体硅片在纯度和电学特性方面较新能源硅片有更高要求,所以在制造过程中需要更多的纯化步骤和供应原料,造成制造原料的种类更加多样化。所以硅料成本占比相对减少,但是制造费用占比会相对增加。

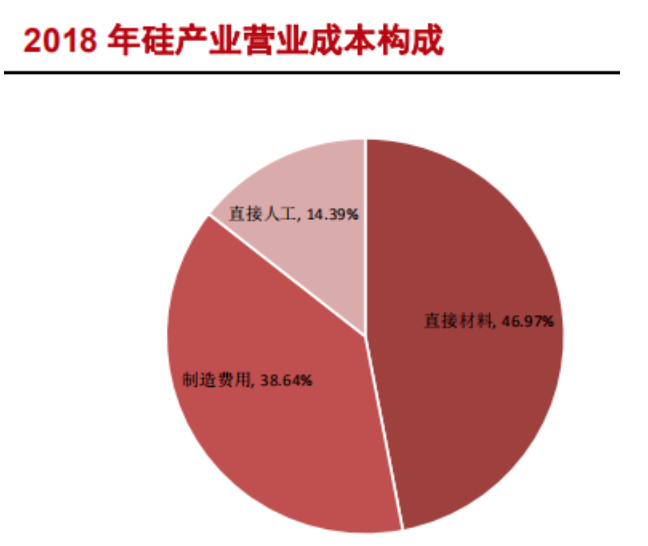

直接材料是主要营业成本构成:对于半导体硅片来说,原材料成本是主要成本,约占主营业务成本的47%。其次是制造费用,约占38.6%,与半导体制造业类似,硅片行业属于资本密集型行业,对固定资产投资需求较高,会因机器设备等固定资产折旧产生较高的制造费用。最后是直接人工费用,占比约为14.4%。

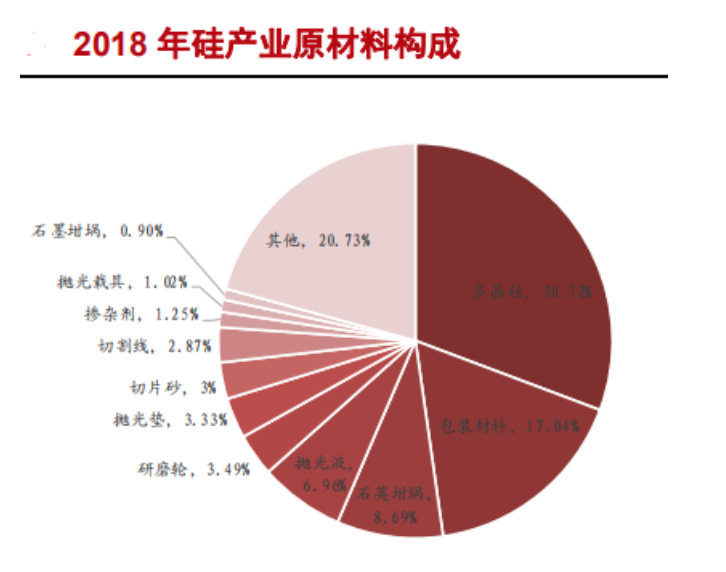

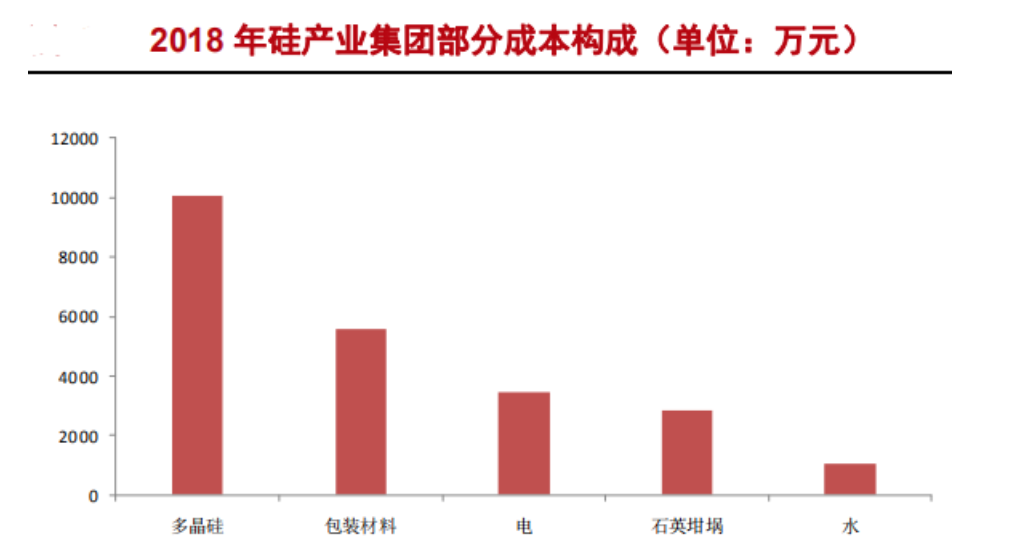

多晶硅是原材料主要成本构成:在硅片制造的原材料成本中,多晶硅是主要原材料,占比约为30.7%。其次是包装材料,占比约为17.0%。由于半导体硅片对于洁净度和真空要求较高,特别是对于硅片这种极易氧化的物质,对包装的要求会比新能源硅片要求要高很多。因此在成本构成中,包装材料占比较高。石英坩埚占比约为原材料成本的8.7%。半导体硅片制造所用的石英坩埚也是一次性坩埚,但是对于坩埚的物理特性,热学特性等等要求更高。抛光液,研磨轮,抛光垫总共占比13.8%,主要用在硅片抛光过程中。

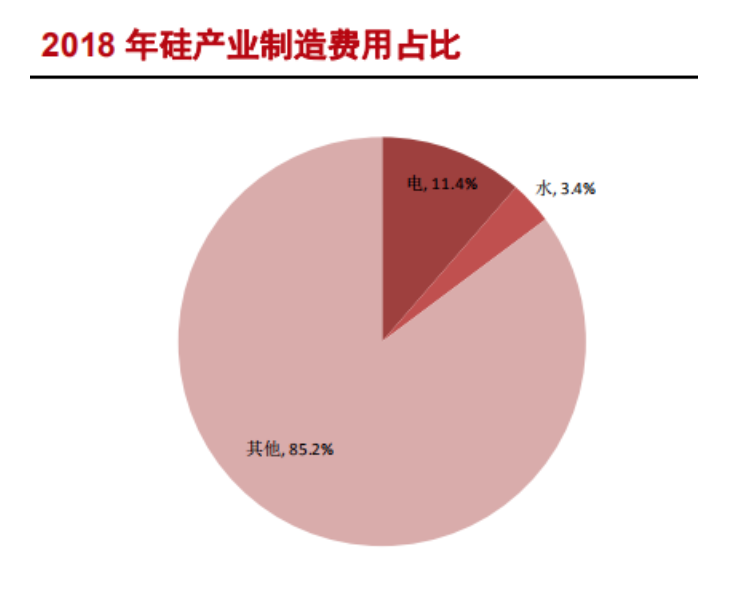

水电费用约占制造成本的15%:在制造成本费用中,水电费用总和约占整个制造费用的15%,其中电费约占11.4%,水费约占3.4%。在对应金额方面,根据硅产业集团的2018年财务数据,电费和水费的总成本和包装材料成本相当,约占多晶硅材料的一半。电费比石英坩埚略高20%左右。

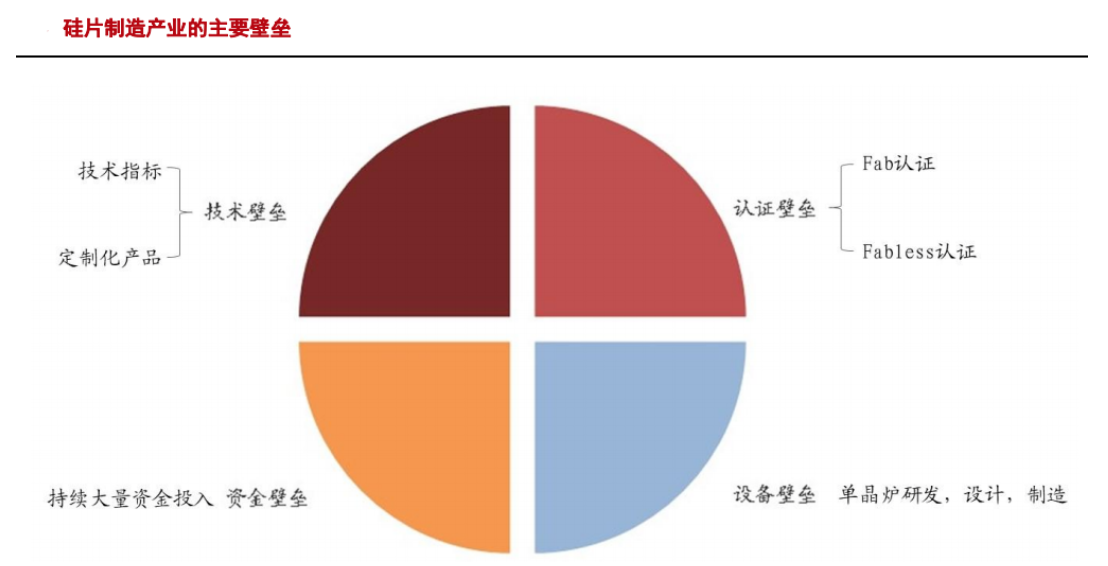

硅片的壁垒较高,特别是对于半导体硅片而言,主要壁垒有四个:技术壁垒,认证壁垒,设备壁垒和资金壁垒。

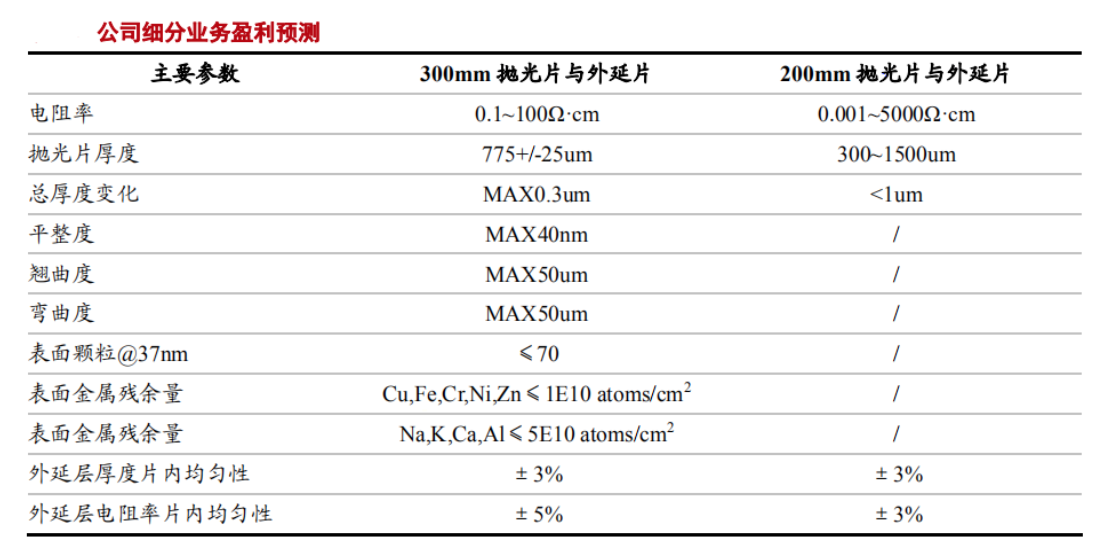

技术壁垒:硅片的技术指标比较大,除去常见的尺寸大小,抛光片厚度等等外,还有硅片的翘曲度,电阻率,弯 曲度等等。在主流的300mm硅片方面,由于先进制程对于硅片的均匀性要求较高,所以相对于200mm晶圆,增加了平整度,翘曲度,弯曲度,表面金属残余量等等参数来监测300mm硅片的质量要求。在纯度方面,先进制程的硅片要求在 9N(99.9999999%)-11N(99.999999999%)左右,是硅片供应商的主要技术壁垒。

硅片是高度定制产品:纯度是硅片的最基本参数,也是主要技术壁垒。除此之外,硅片不是通用型产品,无法复 制。大硅片在各个晶圆代工厂的规格完全不同,各个终端产品的用途不同也会导致硅片的要求规格完全不同。这就要求硅片厂商要根据不同的终端客户产品来设计和制造不同的硅片,这就更大增加了硅片供应难度。

认证壁垒:芯片制造企业对于各类原材料的质量有着严苛的要求,对供应商的选择也非常谨慎。进入芯片制造企业的供应商名单具有较高的壁垒。通常,芯片制造企业会要求硅片供应商提供一些硅片进行试生产,并且大多数用在测试片,而不是晶圆量产片。通过测试片后,会小批量试生产量产片,待通过内部认证后,芯片制造企业会将产品送至下游客户处,获得其客户认证后,才会对硅片供应商进行最终认证,最后签订采购合同。半导体硅片企业的产品进入芯片制造企业的供应链需要经历较长的时间,对于新供应商的认证周期最短也需要12-18个月。

此外,测试片到量产片的认证壁垒:目前国内的12寸晶圆大多停留在测试片的供应上,但是测试片的认证程序和量产片的认证程序完全不同,量产硅片的认证标准更加严格。测试硅片由于不制造芯片,所以只需要晶圆代工厂自己认证,并且只需要在当前制造站点得到认证就可以。但是对于量产硅片来说,必须得到终端fabless客户的认证,并且要得到整个制造流程各个步骤的监测才可以批量供应。一般情况下,为了保持硅片供应和芯片良率的稳定。晶圆制造商与硅片供应商一旦建立供应关系后,不会轻易更换供应商,且双方建立反馈机制,满足个性化需求,硅片供应商与客户的粘性不断增加。新硅片厂商如果加入到供应商行列,必须提供比原有供应商更加紧密的合作关系和更高的硅片质量。所以在硅片行业,硅片供应商和晶圆制造商的粘性较大,新晋供应商打破粘性的难度较大。

设备壁垒:制造硅片的核心设备是单晶炉,可谓是硅片中的“光刻机”。国际主流硅片厂商的单晶炉都是自己制造。比如信越和SUMCO的单晶炉是公司独立设计制造或者通过控股子公司设计制造,其他硅片厂商无法购买。其他主要的硅片厂商都有自己的独立单晶炉供货商,并且签订严格的保密协定,导致外界硅片厂商无法购买,或者只能购买到普通单晶炉,而对于高规格单晶炉无法供货。所以设备壁垒也是国内厂商无法进入全球硅片主流供应商的原因。

资金壁垒:半导体硅片制造工艺复杂,需要购买先进,昂贵的生产设备,也需要根据客户的不同需求不断进行修改和调试。由于设备折旧等固定成本较高,下游需求的变化对硅片企业的产能利用率影响较大,从而对硅片制造公司的利润影响较大。特别是新进入硅片行业的公司,在没有达到规模出货之前,几乎一直处于亏损状态,对资金壁垒要求较高。另外,由于晶圆厂对于硅片的认证周期较长,这期间需要硅片制造商持续投入,也需要大量资金

硅材:仍将是未来主流材料

目前:硅是主要半导体材料

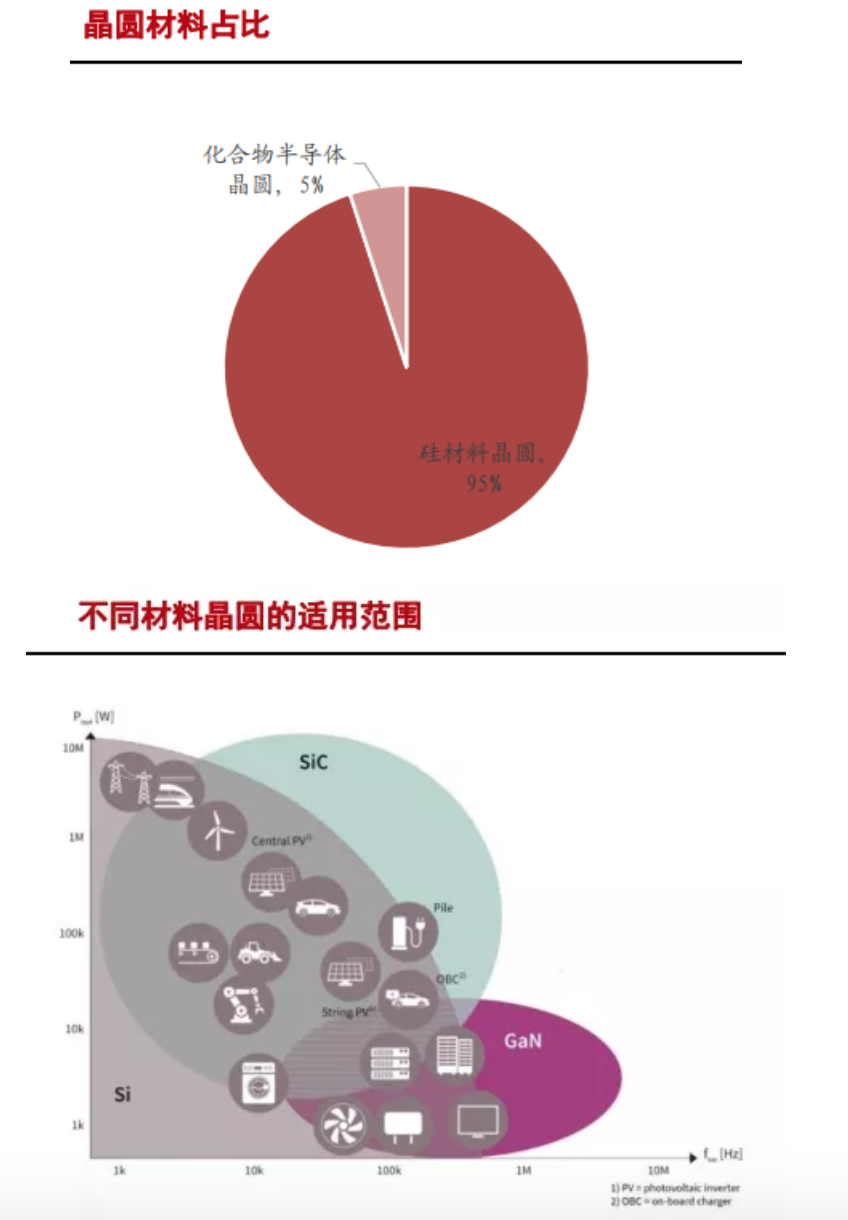

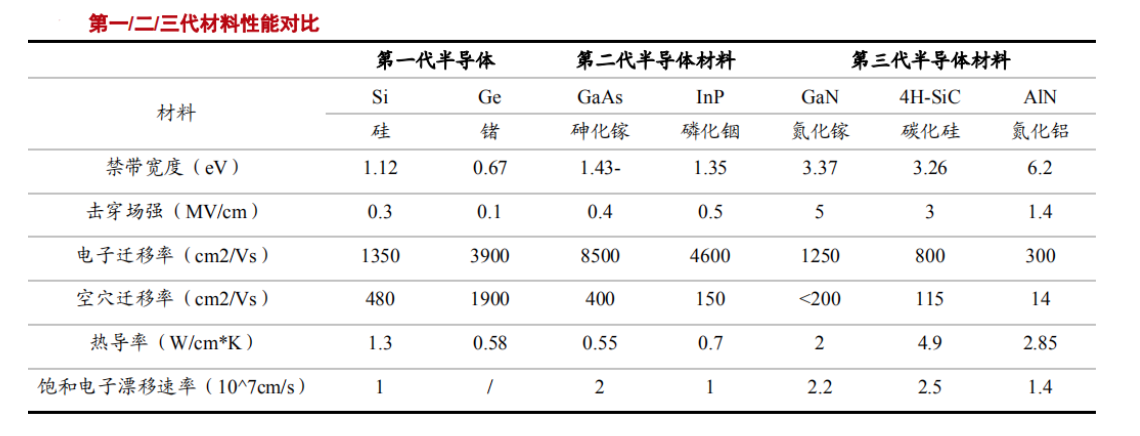

目前,半导体晶圆市场是以硅材料为主。硅材料占比约为整个半导体市场的95%。其他材料主要是化合物半导体材料,以第二代半导体材料GaAs晶圆和第三代半导体材料 SiC,GaN晶圆为主。其中,硅晶圆以逻辑芯片,存储芯 片等等为主,是应用最广泛的半导体晶圆材料。GaAs晶圆以射频芯片为主,主要应用场景是低压,高频率;第三代半导体材料以高功率,高频率芯片为主,主要应用场景是大频率,高功率。

化合物半导体和硅材料不是竞争关系,而是互补关系;半导体材料(特指晶圆,衬底和外延片材料)的发展规律包含三个路线,分别是尺寸,速度和功率,三种路线对应的是第一代,第二代和第三代半导体材料。

第一代半导体材料:大尺寸路线:第一代半导体材料是指硅材料。硅材料是发展最早的晶圆材料,也是现阶段技术最成熟,成本最低,产业链最完善的材料。同时,由于硅片的尺寸变大,导致单个芯片成本减小。主要应用领域是 逻辑芯片和低压,低功耗领域。硅晶圆尺寸从 2 寸,4 寸,6 寸,8 寸,再到当今主流的 12 寸晶圆技术。典型的硅片公司如日本的信越化学,sumco 等等。目前国际主流晶圆厂中,都是以硅材料作为主要生产材料。

第二代半导体材料:高速度路线。由于在射频电路中需要芯片可以承受高频率开关,所以发明了第二代半导体晶圆。主要应用领域是射频电路,典型终端领域是手机等移动终端的射频芯片。第二代半导体主要是以GaAs(砷化镓),InP(磷化铟)为代表的半导体材料,其中GaAs是当今常用的移动终端射频芯片材料。典型代工企业有台湾稳懋,宏捷,美国Skyworks,qorvo等等是射频芯片IDM公司。目前主流是在4寸和6寸晶圆为主。

第三代半导体材料:高功率路线:几乎在相同起点,最有机会。第三条路线是功率变大,从而促使在高功率电路领域广泛应用,主要材料是SiC和GaN。主要终端是工业,汽车等领域。功率路线在硅材料上发展了IGBT芯片,而比IGBT拥有更高性能的是SiC(碳化硅)和GaN(氮化镓)材料。目前SiC晶圆以4寸和6寸为主,GaN材料以6寸和8寸为主。世界主要代工厂如美国的Cree,wolfspeed和德国的X-Fab。但是在此领域,国际巨头的发展也比较缓慢,国内诸如三安光电等企业,虽然在技术水平上还有一定差距,但是处于整个行业起步阶段,是最有可能打破国外垄断,在国际功率代工版图上占据一席之地。

未来:化合物无法代替硅材

化合物材料需要硅衬底:目前虽然有SiC,GaN晶圆的芯片大量使用,比如小米,oppo,realme发布的GaN充电器,特斯拉发布的model3使用SiC MOSFET代替IGBT。但是对于晶圆来讲,目前大多消费类化合物半导体芯片是以硅片为衬底,然后再做化合物外延片,在外延片上再制作芯片。

化合物半导体晶圆成本较高:目前由于化合物半导体产业链不够完整,所以化合物半导体产能较低,化合物半导体晶圆价格较高。导致终端用户接受度较低,消费电子方面还是以“硅衬底+化合物外延片”作为主流解决方案。在汽车领域,目前还是以硅基IGBT作为主流解决方案。硅基IGBT芯片成本较低,而且可选电压范围较大。

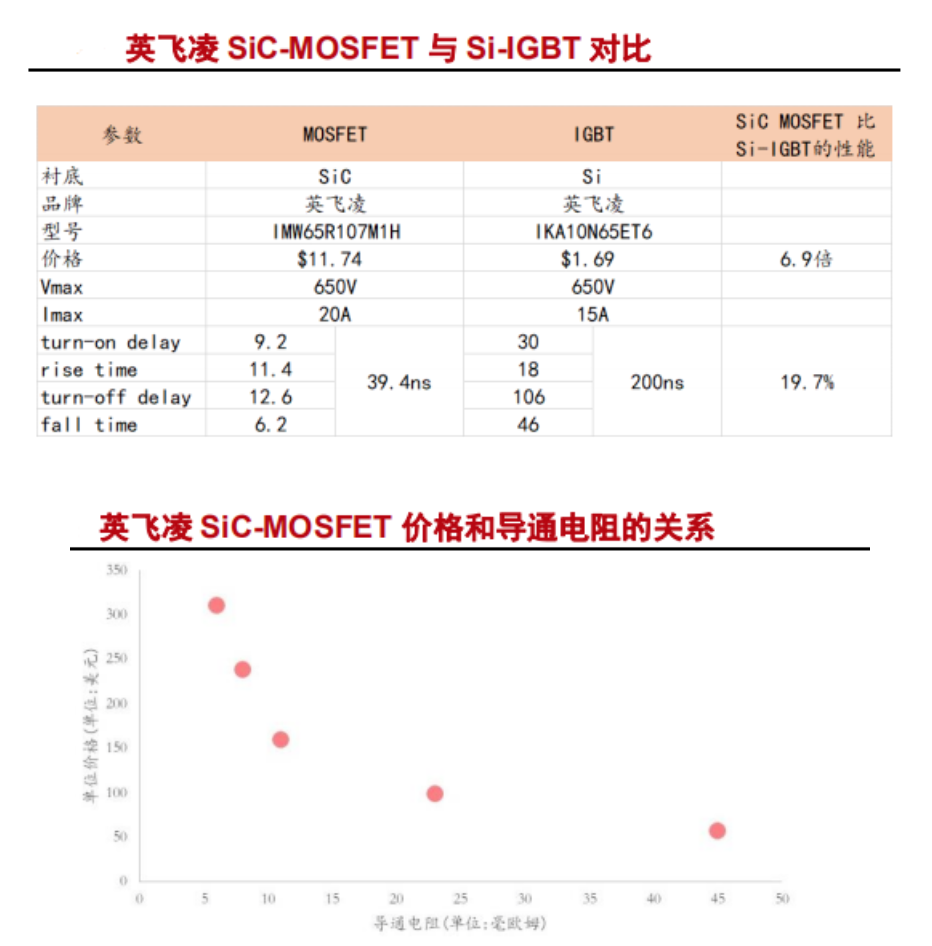

而SiC MOSFET器件的价格是硅基IGBT的6至10倍。对比英飞凌650V/20A的技术参数下,SiC-MOSFET和Si-IGBT的性能参数,SiC-MOSFET依然在性能参数方面优于Si-IGBT,但是在价格方面SiC-MOSFET是Si-IGBT的7倍。而且SiC器件随着导通电阻的减小,SiC-MOSFET价格呈指数级增长,比如导通电阻在45毫欧姆时,SiC-MOSFET只有57.6美元,导通电阻在11毫欧姆时,价格为159.11美元,在导通电阻等于6毫欧姆时,价格已经达到310.98美元。

参考资料来自:浙商证券研究所

END

驭势资本是一家以研究驱动的硬科技精品投资银行,深耕集成电路、5G、物联网、数据智能和汽车科技领域,为顶尖的科技创业者提供专业资本服务。核心团队在硬科技领域拥有丰富的投融资经验,先后投资及服务的项目包括翱捷科技、臻驱科技、微众银行、微医集团、宏晶科技、晟矽微电子、地大信息、曼荼罗、美林数据、事成股份.

原文链接:https://mp.weixin.qq.com/s/Hf...

微信号

更多硬科技领域的技术和市场分析请关注驭势资本专栏。