本文首发于“全国大学生集成电路创新创业大赛”官方公众号,非常感谢集创赛组委会提供参赛心得分享。个人共指导本科生参加三届集创赛,获三等奖1次,一等奖2次,其中2020年获赛题企业大奖(仅颁发给一等奖第一名)。本人研究方向为数字集成电路设计、EDA算法,因此,三次参赛的选题均为数字芯片、FPGA相关方向。本文主要分享一些集创赛的参赛经验,抛砖引玉,希望各支参赛队在第五届集创赛中取得好成绩。

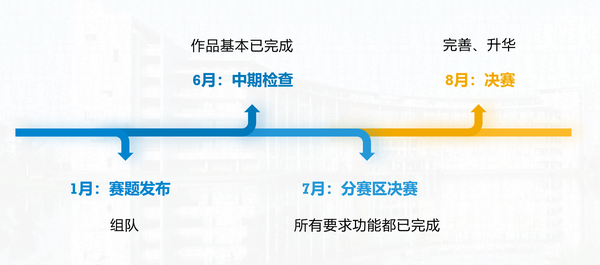

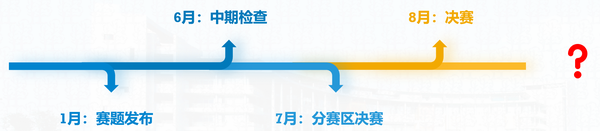

1、集创赛重要时间节点:

把握时间节点与其对应的作品完成度是指导教师和参赛学生的首要任务。集创赛每年大约在1月份发布赛题,3月中旬完成报名。整个比赛的进程中,有三个节点非常重要:

- 6月,中期检查:作品基本完成初步的FPGA系统调试。如果此时尚未搭建FPGA平台,有很大可能会被淘汰。

- 7月,分区决赛:完成FPGA原型系统,完成题目要求的所有功能。注意:此时必须完成FPGA系统的演示,否则很难晋级下一阶段。

- 8月,总决赛:充分利用总决赛之前的20天左右的时间,须在分区决赛成果的基础之上修bug,提升系统指标书,尤其是根据分区决赛评审的建议,思考PPT如何更好地展现作品的优点与特色,这些将会对冲击杯赛大奖有很大帮助。

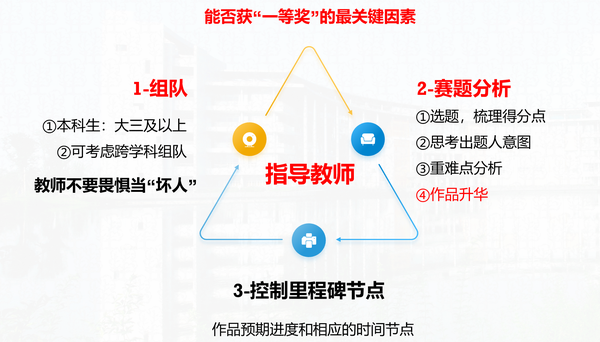

2、指导老师需要做哪些工作?

如果想角逐一等奖和“企业大奖”,仅在FPGA上完成所有规定功能是远远不够的。须把“企业大奖”看做一篇学术论文,针对具体题目进行详细的文献分析、提出创新的解决方案、呈现全面而严谨的实验结果与优劣分析,因此,指导老师在比赛中有着举足轻重的作用。

(1)组队

高质量的学生团队是获奖最为重要的先决条件,本文重点讨论本科生组队。如果需要本科生参加,建议选择大三、大四的学生参加,尤其是有扎实FPGA、嵌入式功底的大三本科生。集创赛于2020年被列入国家级赛事中,获奖对本科生推免、考研面试等有着非常重要的影响。集创赛每年于8月中旬结束,学生在9月份即可使用获奖证书申请教育部研究生推免加分,因此,大三本科生的参赛积极性、对获奖的重视程度是所有学生中最强的。

指导教师在组队过程中可根据题目情况适当考虑跨学科组队。在组队过程中,教师不要畏惧当“坏人”。学生自发组队时,大部分都会选择室友、同学来做队友,教师需对团队成员做灵活调整,确保学生之间强强联合、优势互补。

集创赛很多赛道不区分参赛学生的学历,即本科生与硕士、博士在同一个赛题中角逐奖项。看似本科生有较大的劣势,但是历年的参赛情况证明大部分参赛的本科生能力极强,在竞赛中丝毫不落下风,因此,教师在做赛前动员之前要打消本科生的参赛疑虑,只要本科生具备扎实的能力,积极备赛,都能收获一个好的结果。

(2)赛题分析

重要性仅次于组队,是体现指导老师价值的最重要环节,是能否获得“一等奖”的一个极为重要的环节。指导老师需根据自身研究方向、学生的能力特点来选择获奖可能性最大的题目,并能够帮助学生梳理得分点、赛题重难点。

特别重要的是:(1)思考出题人意图,发掘赛题本质,确保学生在做题过程中不会出现方向性的错误。(2)拔高作品的技术性和学术性,引导学生提出具有原创性、优越性的方案,将比赛技术指标对比的层次拉高到更为普适的学术前沿探讨。

此外,指导教师需要清晰地控制作品的里程碑节点,包括作品预期进度和相应的时间节点。确保学生在近半年的备赛中,不仅仅有总体目标,还有清晰的节点小目标。尤其是本科生,指导教师还需审阅参赛队的技术文档和答辩演示PPT。

3、学生需要具备哪些能力?

- FPGA与嵌入式软硬件开发能力。对比集创赛过去四届的数字芯片与FPGA赛道,可以发现SoC与系统开发能力要求越来越高,几乎每道赛题都要求完成一个软硬件协同计算的SoC系统和可演示的FPGA Demo,掌握verilog代码编写能力仅仅是基本要求。

- 领域算法。如AI、图像视频处理算法、LDPC编解码算法等等,与学生的研究方向、赛题关系紧密。

- 芯片设计的知识体系。学生是否适合参赛的准入门槛。

- 文献查找与分析能力。本科生尤其欠缺这一点,需要老师指导、点拨。

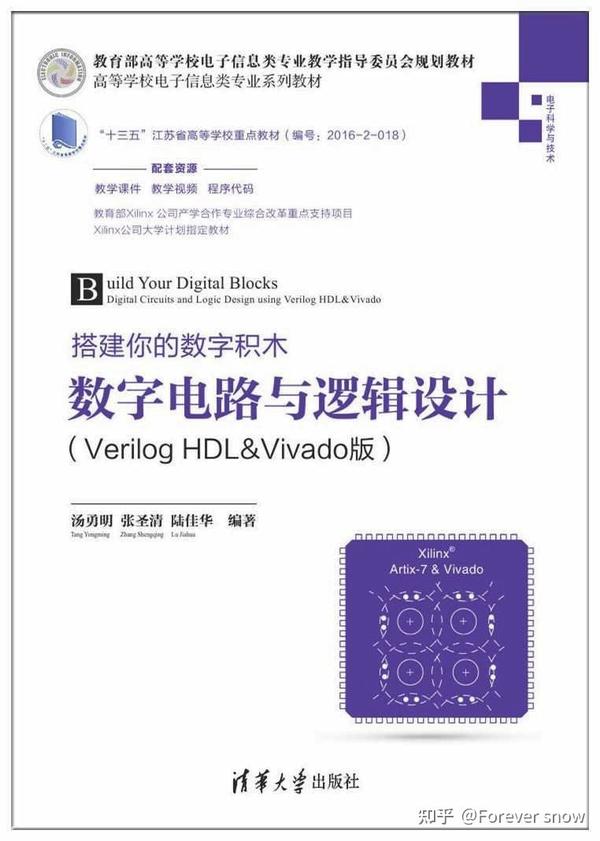

4、学生如何储备参赛需要知识?

以数字芯片、FPGA类赛题为例,本科生需要在大二认真学习数字逻辑与数字系统,掌握Verilog语言,熟悉vivado等FPGA开发流程。目前大部分学校的数电课程还是以74系列芯片为主要内容,已经远远落后于工业界数字电路设计的主流技术,数电学完之后也很难具备参加集创赛的基本能力要求。此处推荐东南大学汤勇明老师编写的《搭建你的数字积木——数字电路与逻辑设计》。这本书将Xilinx Vivado集成设计开发环境在第1章中就呈现给读者,让读者从一开始就能利用该开发工具学习具体逻辑设计。这本书的优点是采用了电路设计加VerilogHDL编写的方法,重点突出模块化编程思想并详细介绍了IP设计、封装和调用方法,并在书中给出了VGA控制器、数字图像处理设计等实际案例。

在Verilog与FPGA的学习过程中,强烈建议学生自己有一块FPGA开发板实物练手。推荐先从纯逻辑的开发板学起,强化VerilogHDL与FPGA工具开发能力。此处推荐两款价格比较便宜的开发板:(1)Spartan Edge Accelerator(SEA),采用了Xilinx Spartan7器件,价格<400元,适合入门的初学者完成一些轻量级的系统加速。(2)Digilent Arty A7(Artix-7),硬件逻辑资源和接口相对丰富,开源的案例比较多,有利于入门的时候做一些较为复杂的案例。

掌握纯硬件逻辑开发之后,就可以选择一些集成处理器硬核的SoC类型FPGA开发板,如Xilinx PYNQ、ZYNQ等。这两种开发板资源丰富,可作为AI处理器的实现平台。如果对数字信号处理的FPGA实现感兴趣,也可以学习HLS编程,推荐参考书《Parallel Programming for FPGAs》,本书有中文版和英文版,书和案例都可以在github下载。

建议同学们关注集创赛官方公众号“芯人类”、“智前沿”,持续推出了很多精品课程和技术讲座!同学们也可以学习我的两门MOOC课程《芯动力——硬件加速设计方法》、《数字集成电路静态时序分析基础》,课程网址可在我的个人主页上查到(http://www.dizhixiong.cn)。

芯动力--硬件加速设计方法\_西南交通大学\_中国大学MOOC(慕课)www.icourse163.org 数字集成电路静态时序分析基础-南京集成电路大学-集成电路创新学院-IC学院-南京集成电路产业服务中心有限公司www.iccollege.cn

数字集成电路静态时序分析基础-南京集成电路大学-集成电路创新学院-IC学院-南京集成电路产业服务中心有限公司www.iccollege.cn

5、大赛外延

决赛不是终点,希望更多同学在决赛之后依然能优化算法与电路,进而产生专利、paper等,能够对同学们的学术道路和未来发展有更长远的帮助

问题讨论区

大家可以在集创赛 Arm 杯讨论区进行提问及讨论,讲师会来给大家解答相关技术问题。

集创赛培训系列