【嘉勤点评】复旦微电子的时钟布局方法专利,通过对存在时钟资源溢出的时钟域内的全局时钟进行时钟约束,直至FPGA器件上各个时钟域内均没有时钟资源溢出,缩短了时钟布局所需的时间,并且提高了布局整体质量。

集微网消息,复旦微电子的亿门级FPGA产品填补了国产高端FPGA空白,并处于领先地位。近日,复旦微电子拟在科创板上市,其募集的一半资金将用于研发FPGA。

随着现场可编程门阵列(FPGA)器件规模的扩大,其结构变得更复杂,设计流程中愈发依赖对电子设计自动化(EDA)工具的使用。其中,使用EDA工具设计FPGA器件时,布局是最重要且最耗时的一项工作。目前,对FPGA器件进行时钟布局时,通常基于全局布局后的结果,对存在时钟资源溢出的时钟域内的全局时钟做进一步的时钟域约束,并指导下一次迭代过程中全局时钟的可摆放时钟域。然而,采用上述方法进行时钟布局时,所需时间较长。

为此,复旦微电子于2019年7月2日申请了一项名为“时钟布局方法、装置、EDA工具及计算机可读存储介质”的发明专利(申请号: 201910590166.6),申请人为上海复旦微电子集团股份有限公司。

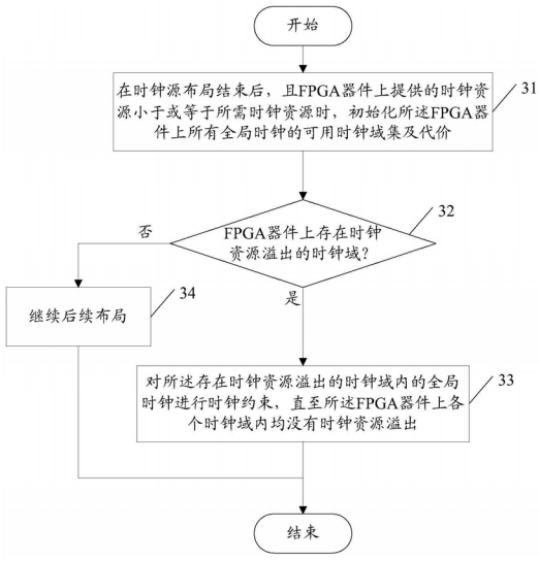

图1 时钟布局方法流程图

图1为本发明提出的时钟布局方法流程图,包括以下步骤:

首先,在时钟源布局结束后,且FPGA器件上提供的时钟资源小于或等于所需时钟资源时,初始化所述FPGA器件上所有全局时钟的可用时钟域集及代价(31)。若FPGA器件上提供的时钟资源大于所需时钟资源,则可直接进行后续布局。而若小于或等于所需时钟资源,即FPGA器件上存在时钟资源溢出。此时可以先初始化FPGA器件上所有全局时钟的可用时钟域集及代价。其方法存在多种,比如部分或全部全局时钟的可用时钟域集为FPGA器件上所有时钟域集合的子集。为了便于时钟布局,降低时钟布局复杂度,初始化器件上所有全局时钟的可用时钟域集均为FPGA器件上所有时钟域的集合。

然后,基于初始化的结果,判断所述FPGA器件上是否存在时钟资源溢出的时钟域(32)。初始化FPGA器件上所有全局时钟的可用时钟域集及代价后,判断FPGA器件上是否存在时钟资源溢出的时钟域,也就是判断FPGA器件上任意时钟域内全局时钟的数量,是否存在超过该时钟域内的时钟资源所支持的全局时钟的数量的情况。其中,时钟资源包括FPGA器件上的走线等。

接下来,当FPGA器件上存在时钟资源溢出的时钟域时,对所述存在时钟资源溢出的时钟域内的全局时钟进行时钟约束,直至所述FPGA器件上各个时钟域内均没有时钟资源溢出(33)。

而如果FPGA器件上不存在时钟资源溢出的时钟域时,继续后续布局(34)。初始化FPGA器件上所有全局时钟的可用时钟域集及代价后,若时钟资源没有溢出,则继续后续布局即可。所谓后续布局,可能仅包含整体布局及细节布局,还可能同时包含全局布局。

简而言之,复旦微电子的时钟布局方法专利,通过对存在时钟资源溢出的时钟域内的全局时钟进行时钟约束,直至FPGA器件上各个时钟域内均没有时钟资源溢出,缩短了时钟布局所需的时间,并且提高了布局整体质量。

复旦微电子作为集成电路的龙头企业,在国内集成电路设计行业中举足轻重,具有非常成熟的产品线和系统解决方案,一直致力于为全球用户的智能品质生活提供“芯”保障。复旦微电子将继续不断创新,与合作伙伴和用户一起“专芯成就未来”。

关于嘉勤

深圳市嘉勤知识产权代理有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)