作者注:本文最初发表于2017年7月17日

深恐有人看到“架构”就想到“枯燥”,首先给大家讲个糅合了《大话西游》人设与《灌篮高手》题材的魔幻现实主义故事——对篮球和段子都没什么兴趣的读者可以自行跳过,直接从第一个黑体小标题处开始阅读。

6月底、7月初,正是美职篮(NBA)每年一度的自由球员签约期。今年是自由球员大年,超级明星们纷纷逃离母队,寻找有实力或潜力的下家,组成三巨头乃至四巨头,抱团之风盛行,意在对抗西域五魁首。

变局缘起6月上旬举办的东西部篮球挑战赛。由孙悟空、猪悟能、沙悟净、白龙马、唐三藏组成的东土大唐队,一路西行,基本没有遭遇像样的抵抗,志在卫冕。西部联盟胜出的代表队去年惨遭逆转之后,立即招募强力外援牛魔王,与春三十娘、白晶晶、紫霞、青霞组成五魁首阵容,誓要雪耻。

论纸面战力,孙悟空乃此十人(乃至整个联盟)之中的最强者,牛魔王尚且略逊一筹。悟空亲自招募来的猪悟能和沙悟净,也是业内成名已久的宿将,联手组成三巨头,可谓当世无双。由于两队实力太强,之前的东西联盟内部选拔赛只是走个过场,甚是无聊,钓鱼群众们只能寄希望于最终的挑战赛。

比赛开打,大家才发现,东土大唐队竟也不是西域五魁首的对手。悟空仍然罕有其匹,但在大部分时间里,都被五魁的车轮战所困,切断了与悟能、悟净的联系,三巨头只能各自为战。若不是天庭为了收视率和联盟招牌,授意太白金星带领的裁判组帮助东土大唐队拿下第四场,怕是难逃被西域五魁首横扫的命运。

震惊之余,各路砖家们不得不承认,去年的惊险逆转,掩盖了东土大唐队的架构缺陷。悟能、悟净虽也曾为帅为将,但在投身东土大唐之后就基本丧失了领兵的积极性和主动性。球权交由悟空做主,悟能尚且偶尔可与悟空各砍41分、甚至投中决定冠军归属的致命三分,悟净却每每在关键时刻沦为只有三句台词的死龙套:

“三藏,对方中锋我扛不动!”

“大圣,这空位三分我投不进!”

“八戒,对方小个我防不住!”

来自网络,图文无关

另外二位,白龙马功能单一,唐三藏也就能在高僧联谊赛里仗着御弟的名头拿个MVP,挑战赛中不论与谁对位都会被完爆。用西域的流行语形容,东土大唐队是典型的Scale-up(纵向扩展)架构,全队的上限取决于悟空一人;西域五魁首则基于更为灵活的Scale-out(横向扩展)架构,牛魔王的加入使全队多了一个极具威胁的持球点,阵容上不再有明显的短板。纵然单挑无人能全面压制悟空,但毕竟双拳难敌四手,五魁的总天赋更具优势,加之配合默契,运转流畅,自然占尽上风。

西域强队当然不想继续被五魁首按在西决地板上随意摩擦,纷纷效仿五魁的组队模式——囤积巨星,增加持球点。然而,巨星组队绝不是简单的累加,教练和总经理首先要考虑以下两个问题:

球权:篮球是5个人的,篮球只有一个。有多个持球点可以发起进攻,对手更加难以防范,但球权怎么分配?设想六耳猕猴和悟空一队(我说的不是CP3和另一位詹姆斯的“灯泡组合”),每位场均都要持球10分钟,这球不够分的啊!所以必定要有人做出牺牲,更多的打无球,场上形势需要时才接管球权,而这通常意味着数据的下降,不利于接下来拿大合同。

薪水:为了防止球星扎堆导致各队实力严重失衡,联盟早有工资帽制度,突破薪金上限的球队要付出成倍的奢侈税。想把多名巨星聚在一起打球,要么有人主动降薪,要么球队老板肯付巨额奢侈税。实际情况是,两种手段往往要联合使用,才能构建出一支具备足够战斗力的球队。

球权和薪金,对应到CPU与服务器的设计中,就是多核之间的组织架构,以及功耗上升引发的散热和供电挑战(后续将有专文另述)。

CPU的纵横扩展相对论

根据作用范围的不同,Scale-up和Scale-out可以是相对(而不是绝对)的概念。举一个范围逐级递减的例子:

服务器层面:一台有2个CPU(双路)的服务器,要得到4个CPU,在这台服务器内部增加2个CPU,变成四路的做法(不要纠结于具体实现),通常被称为Scale-up;而再增加一台同样的双路服务器,两者之间通过网络连接,也形成一套共4个CPU的系统,通常被称为Scale-out;

CPU层面:在这台双路服务器内部,要获得多一倍的内核数,把CPU升级到具有2倍内核数的型号,可以被称为Scale-up;CPU不变,但通过CPU之间的互连把数量增加到4个(四路),可以被称为Scale-out(在上一级属于Scale-up);

内核层面:要提升CPU的性能,增加单个内核的性能,可以被称为Scale-up;增加内核的数量,可以被称为Scale-out(在上一级属于Scale-up)……

讲到这一层,可以得到两个“显而易见”的结论:

一是“纯度越高”的Scale-up越难。近年来CPU单核性能的提升有多缓慢?华为在新一代服务器(FusionServer V5)发布时指出,通用处理器的单核性能,在上一个十年,还能以每年1.5倍多的幅度提升,现在只有每年1.1倍多。具体数字上可能会有出入,但大致状况英特尔也无法否认。所以,从至强E5到v4,再到至强可扩展处理器,每一代CPU推出时,如何增加内核数量,都比内核的微架构改进更吸引关注。既然内核数量的增长已成为性能提升的主要推动力,那么……

二是内核之间的互连方式越来越重要。服务器节点之间的互连叫网络(Network)或Fabric,CPU之间的互连有直接叫Interconnect(如QPI和UPI)的,CPU内核之间的互连……名字上的花样可就多了,这个后面会重点展开。但是,不论什么级别,不管怎么称呼,都可以从网络拓扑的角度去对比衡量之。

从环形总线到2D-mesh

今天的讨论要先追溯到贯穿整个至强E5时代的(双向)环形总线。“2012年,那是一个春天,有一款CPU在8个内核中间画了一个圈……”

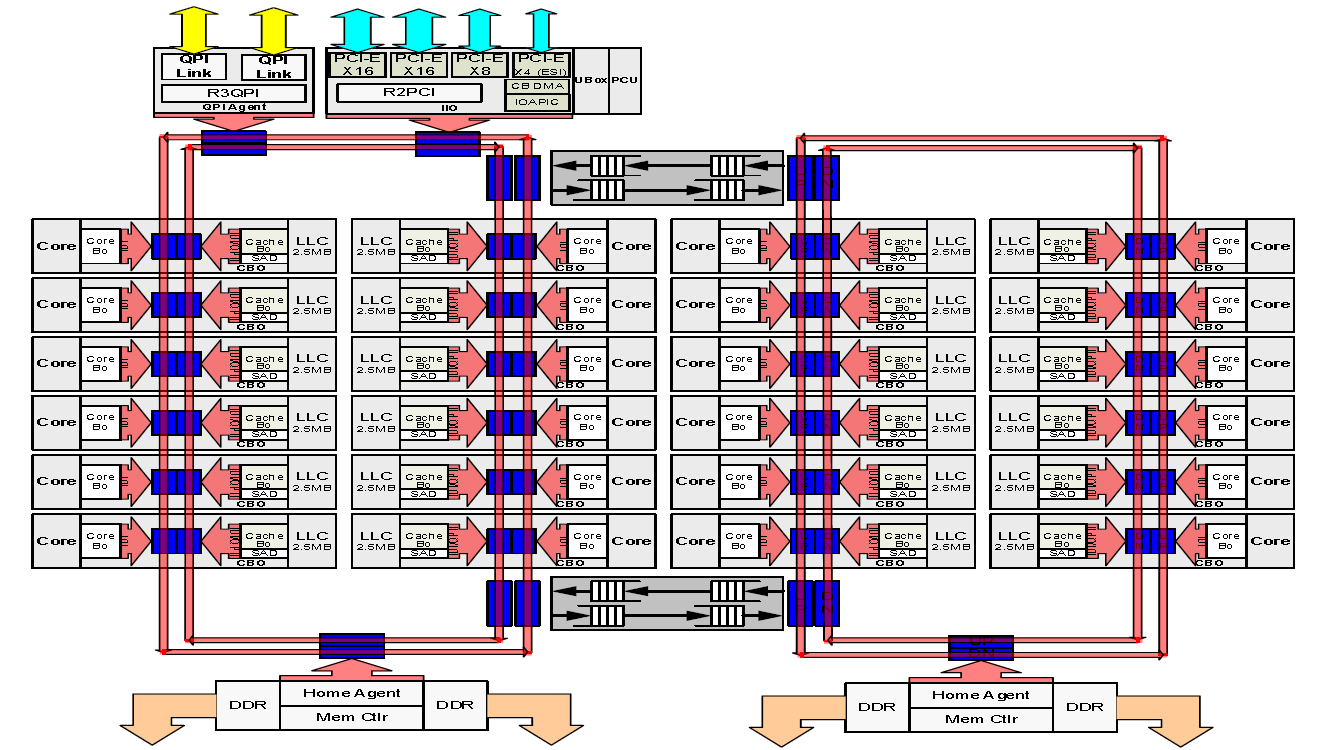

此图有真意,欲辨已……熏晕

没错,这就是初代E5-2600的双向环形总线(Bi-Directional Full Ring)。8个内核共用1组(双向)环形总线,套用球类运动的比喻,仍然有争用球权(环线)的问题,只不过队员的人数介于篮球和足球之间(5<8<11)。

初代至强E5的双向环形总线贯穿8个内核及其共享L3 Cache(LLC)。理论上,因为可以从两个方向中选择较短的路径,双向环形总线的平均时延只有单条环形总线的一半

就算内核(核心)比篮球明星能忍(1/8 vs. 1/5),内核数量再增加的话,环形总线的带宽等资源毕竟是有限的,过度争用也会导致阻塞,影响到所有内核性能的发挥,反过来限制内核数量的继续增长。好在CPU可以部分借鉴那个被安到山东军阀韩复榘头上的笑话(多发一个球)——再加一个环。在双(向)环形总线的加持下,E5/E7 v4的架构支持的CPU内核数量可达24个。

E5 v4家族的两条双向环形总线(共4个环)支持最多24个内核,但为了把风头让给E7 v4,“牺牲”掉2个内核,最多只有22个内核

至强E5/E7家族的双向环形总线(两个方向相反的同心环),优势是相对简单,利用率高,可以在两个方向中,选择路径较短的那条访问特定的内核及共享的L3 Cache(Last Level Cache,LLC)——想象一下乘坐环线地铁的场景就知道了;缺点是环不能太大,如果连接的节点(如内核、内存控制器、QPI、IIO等)过多,访问的平均路径会变长,节点能分到的平均带宽也会降低——北京已经证明越往外修环线越不灵。

E7 v2采用一个大的(单向)环嵌套两个独立的(单向)环,到E7 v3更改为两组通过缓冲交换机连接的双向环(两个方向相反的环),优势是每组环内的带宽和延迟更好。注意每个(组)环的L3 Cache被视为一体的画法(不考虑左侧的大单向环)

双环架构可以成倍增加内核数量,两组环之间设置两个缓冲交换机(buffered switch)作为“换乘”站解决跨环通信的需求。严格说来,这也属于一种“胶水”结构,两组环之间的两个数据交换电路就是把两部分内核粘在一起的“胶水”。

仅从环的数量上来看,左边至强E5 v4中等内核数(MCC)与E7 v2一样也是3个环——10个内核一侧为双向环,5个内核一侧为单向环,分为两组(仍然是双环架构),规模越大环数越多的原则不变,尽力保证每个核能获得的带宽和延迟水平。右边较少内核数(LCC)与初代至强E5一样是两个套在一起的双向环,本文中将其视为一组环(单环架构)

很显然,跨环的访问会增加延迟,并且要消耗两组环的带宽资源。所以,QPI(Quick Path Interconnect)、PCIe等相对低速的I/O设备仍在第一组环上,第二组环的I/O必然要跨环——慢点还可以接受。内存访问可不能这么搞,所以每组环都有自己的内存(DDR)控制器。

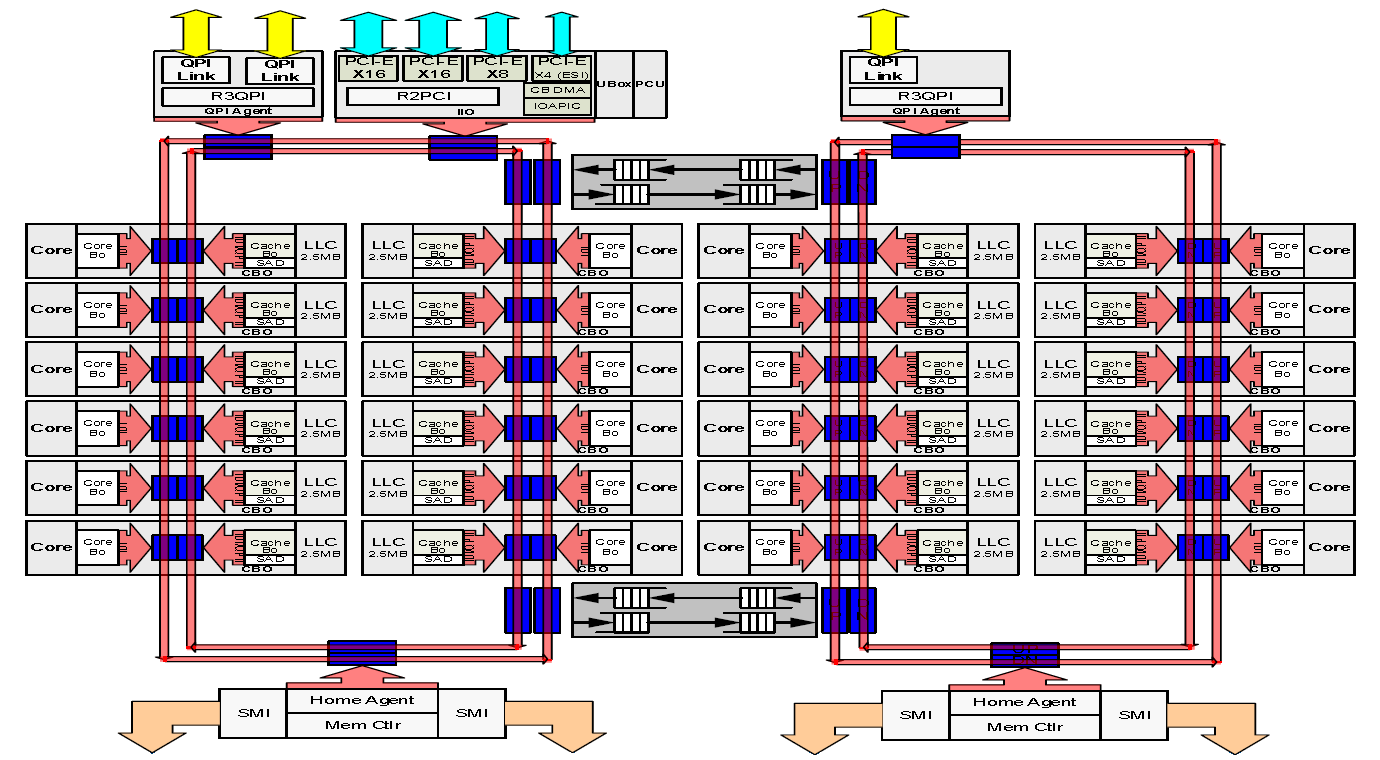

上面说的是E5 v4的情况,E7 v4稍有不同——增加的第3个QPI放在第二组环上,也没必要硬往已经很拥挤的第一组环上塞。

注意E7 v4第二组双向环形总线上方增加的第3个QPI

从双环发展到奥迪(两组双向环按4个环计算)已经要付出如此大的代价,就不要再开奥运会了……必须换一种扩展性更好的架构。

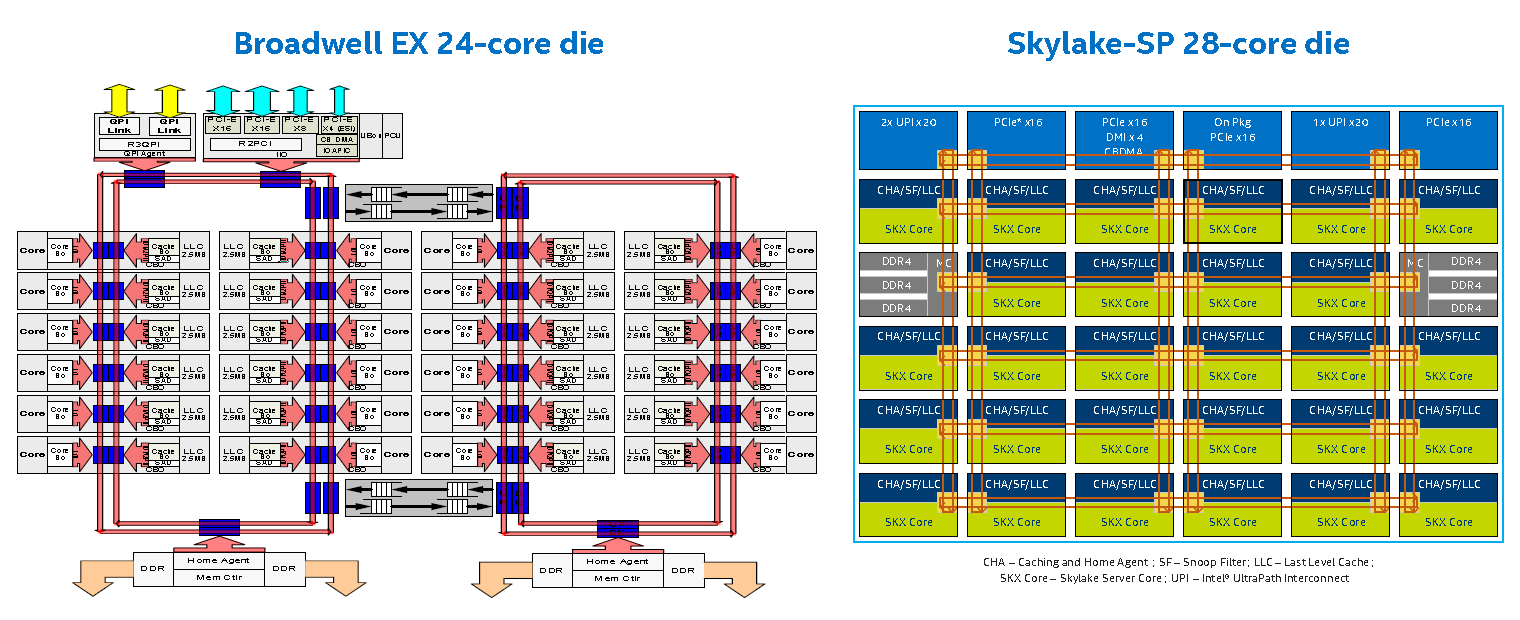

以代号Skylake的初代至强可扩展处理器(Xeon Scalable Processor,至强SP)为开端,英特尔启用了全新的Mesh架构,官方翻译为“网格”片上互联拓扑结构。这种架构的扩展性如何呢?

从至强E5/E7 v4的四环(2组双向环形总线)到至强SP的6×6 Mesh架构,是一维转为二维,有利于扩大互连规模

Mesh架构的历史也是相当的悠久,早已被广泛应用于高性能计算(High Performance Computing,HPC)领域。英特尔自身就有丰富的经验,90年代初推出的Intel Paragon大规模并行超算(当时的水平)采用mesh互连,能够从32个计算节点扩展到2048/4096个i860 RISC微处理器。1995年推出的曙光-1000计算机系统同样基于i860,采用6×6的2D-mesh连接,距今已有22年。

如同前面所说,就拓扑结构而言,CPU内核之间的互连与(HPC系统)各服务器节点之间的互连,本质上是相通的。Mesh架构服务器集群用得,CPU当然也用得,关键看互连规模的需求到没到那个地步。

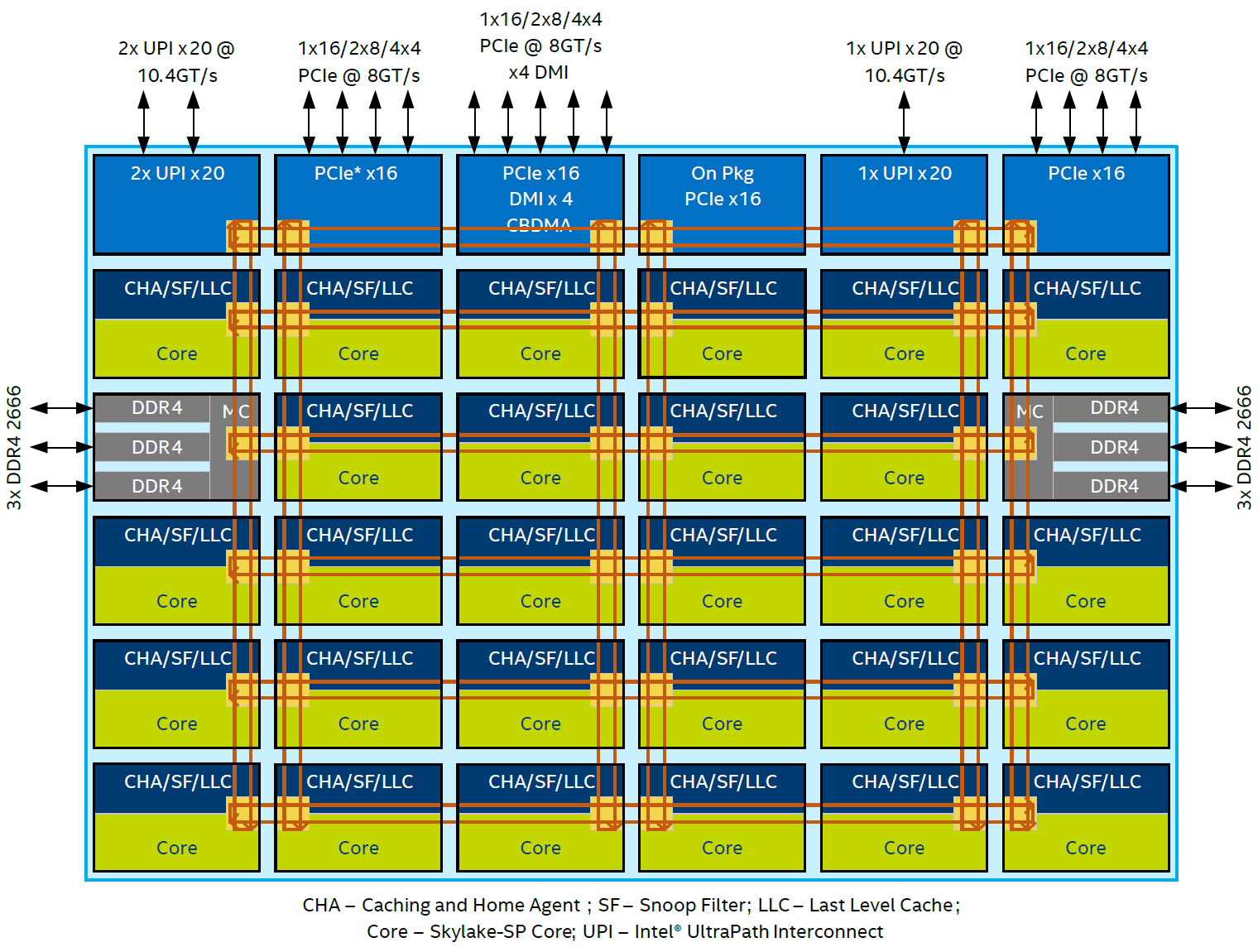

初代至强SP的Skylake-SP架构也采用6×6的mesh,这个互连规模于mesh而言,二十多年前就经过了考验,而今天的环形总线仍然难以达到。行列组织很规整,顶上一行6个全部留给I/O,包括替换QPI的UPI(Ultra Path Interconnect),和更多的PCIe 3.0;侧边两列的中间位置各有一个3通道的内存控制器,其他28(=36-6-2)个位置是内核及其Cache。

Mesh的每个节点上都有一个可以被称为交换机(或路由器)的组成部分,通过水平(X)和垂直(Y)方向的连线组成一个二维的交换矩阵。交换机将非本节点的访问或数据继续向下一节点转发,这个延迟很短,但跳(hop)数多了的累积效果亦不容忽视。Mesh的另一个优点是可以同时存在多条传输路径,但它也不是无阻塞的——假设位于角落上的节点要同时发送3个信息到3个不同的位置,只能先发出去2个,至少要阻塞住1个。

Skylake-SP Mesh架构上的内核、内存控制器和I/O分布,下篇文章还会进一步分析

所以在矩阵中的位置就很重要。Skylake-SP必须把内存控制器放置在边上(要对外),但不能像I/O一样(可以)居于角落,而是相对居中,这样内核最远只需要5跳就可以到达较近的内存控制器。另外,不同的内核到达I/O的距离也都是可以接受的,不会有太大的差异。

换言之,Skylake-SP的Mesh架构可以达到(单个)双向环形总线无法达到的规模,具有更好的连通性,而访问内存和I/O的延迟也基本没有劣化。

大有大的难处:L2 Cache上位

互连架构的变化,也在很大程度促成了Cache机制的转变。

至强E5/E7家族是以共享分布式L3 Cache(LLC,末级Cache)为主Cache的机制,通常每个内核配有2.5MiB L3 Cache,沿着环形总线分布。即使是双向环形总线,也只有两条访问路径可选,走哪条离目标近就选哪个:理论上,一条12个内核的双向环形总线,最远只需要6跳;E5/E7 v4的双向环形总线上还会有QPI、IIO(包括PCIe等)、内存控制器和2个缓冲交换机接口,增加了5个端点,最远的访问也只需要8跳就能到达。

由于访问路径固定,一个(单向或双向)环形总线上所包围的所有(最多12个)内核的L3 Cache,逻辑上可以视为一个整体,即由环形总线将分布式L3 Cache组织为一个共享的缓存池,总线上的每个内核都可以很方便的访问其中的数据。在这种情况下,每个内核私有的L2 Cache也不需要太大——只有256KiB(中间加入的 i 代表1024进制),全部拷贝到其L3 Cache中,反正只占后者十分之一的容量。换言之,一个内核访问L3 Cache池的时候,还可以读到其他内核L2 Cache中的数据。

上述共享L3 Cache层级架构被称为inclusive(包含的),通俗的说就是,L3拿出来一部分空间作为L2的缓存——听起来是不是有点怪怪的?

从至强E5/E7家族到至强SP的Cache架构转变

Skylake-SP的Mesh架构就不同了,在这个6×6的矩阵中,两个相距最远的内核间需要9跳(X方向5+Y方向4)才能到达。更重要的是,两个内核间的访问路径可以有数十上百种,其中一些路径还有可能被阻塞,一个内核访问其他内核的L3 Cache,要付出的代价明显增大。相比之下,Mesh架构的共享L3 Cache可以说是碎片化的,并不很利于共享。

事实上,Mesh架构必然要求尽量的利用locality(所在位置),避免时延劣化,而加大本地的数据存储无疑是一种最简单的优化方案——尽量从L2 Cache获得数据,减少二级缓存未命中(cache miss)的几率。Skylake-SP将L2 Cache的容量提高至1MiB,达到之前的4倍,与改用Mesh架构有很大的关系。

与之前的包含式L3架构(左)相比,Skylake-SP的非包含式L3架构(右):1. 从内存中读取的数据直接进入L2,而不是同时进入L2和L3;2. 当一个L2的行需要被移走,更改和未更改的行都被写回;3. 需要给其他内核共享的数据(才被)拷贝到L3

所以,Skylake-SP的Cache机制,由之前的共享分布式(Shared-distributed)L3为主Cache,转变为私有本地化(Private-local)L2为主Cache,共享L3 Cache主要用作溢出(overflow)Cache。既如此,共享L3 Cache容量就没必要太大,也愈发没有空间缓存已经暴涨的L2 Cache,于是Skylake-SP每个内核的共享L3 Cache骤降近一半,只有1.375MiB——此(L3)消彼(L2)长,对片上资源也是一种节省。

鉴于Skylake-SP每个内核L2 Cache中的数据可能不在L3 Cache中,这种层级架构被称为non-inclusive(非包含式),可以理解为一种类似分层存储的架构。

至强E5/E7 v4与至强SP的L2+L3 Cache(理想值)

| 至强 E7 v4 | 至强 SP | |

|---|---|---|

| L2 Cache | 256 KiB | 1 MiB |

| L3 Cache | 2.5 MiB | 1.375 MiB |

| L2+L3(物理) | 2.75 MiB | 2.375 MiB |

| L2+L3(数据) | 2.5 MiB | 2.375 MiB |

| 最多内核数 | 24 | 28 |

| 总L2+L3(物理) | 66 MiB | 66.5 MiB |

| 总L2+L3(数据) | 60 MiB | 66.5 MiB |

从上表的简单对比中可以看出,至强SP每个内核的L2+L3 Cache总容量比前代有所下降,整体也只是靠着内核数量的优势而稍稍胜出。但是,作为微架构的重要组成部分,更大的本地缓存(L2 Cache)对单核性能的提升还是很重要的。

四路配置的全连接与环形总线

前面已经说过,服务器之间的连接方式,与CPU内核之间的连接方式,原理上是相通的——CPU之间的连接方式,亦然。

提起Mesh架构,没有任何前缀的话,通常指2D Mesh(相关的还有3D Mesh和2D Torus,本文不展开),Skylake-SP的Mesh架构就是这种:相对容易实现,利于扩展,付出的成本代价也比较能接受。

2D Mesh架构能得到广泛的应用,很重要的一点是它比较现实,譬如说……并不是无阻塞的,因为无阻塞的实现代价比较大。

有两种比较常见的无阻塞架构:Crossbar和Full-mesh(全网状,或称全连接)。Crossbar架构猛一看和2D-mesh有点儿像,都是交换机组成的矩阵,但2D-mesh每个节点各有1个交换机,而Crossbar为了保证无阻塞,节点比交换机的数量要少得多,两者间是一个平方关系。

Crossbar(左)与2D mesh(右)示意:绿色圆圈为节点,橘黄色圆点或方框为交换机,可见左边的节点数比右边要少得多(来源:卡内基梅隆大学计算机科学学院)

Full-mesh不需要外部的交换或路由元件,而是任意两个节点间都有直接连接,故得名全连接。一个节点数为N的Full-mesh,连接(线路)总数为N×(N-1)÷2。

8个节点的Full-mesh,连接总数为28条

也就是说,Crossbar和Full-mesh在连接上付出的代价都是节点数的平方关系,随着节点数量增加而急剧上升,因而不太可扩展,甚至不可扩展。

左边是Sun UltraSPARC T2的显微照片,8个内核之间的CCX所在区域就是其8×9的Cache Crossbar,面积几乎与一个内核相当;右边是同为8个内核的初代至强E5-2600,可以对比下双向环形总线在芯片面积上的开销

十年前有一些产品,如EMC的高端存储系统Symmetrix-DMX和Sun的CPU UltraSPARC T2均有采用Crossbar,而3PAR的T系列高端存储则基于Full-mesh。Sun UltraSPARC T2和3PAR T系列都是(最多)8节点互连,不完全是巧合——当然,我举例的这三家公司都在接下来的十年里被收购了,纯属巧合。

最新一代的HPE 3PAR StoreServ 20000,中间是连接8个控制器节点的Full-mesh背板——仍然没有超过8个节点

Full-mesh较少做到8个节点以上,而在8个节点之内还是很划算的——譬如,4个节点之间的Full-mesh,只需要6条线路,便可以获得一个无阻塞的高效网络。

没错,说的就是至强E7的四路配置,每个CPU用3个QPI分别连接另外的3个CPU,构成全连接的网络(Full-mesh);至强E5-4600因为只有2个QPI,所以4个CPU只能构成一个双向环形网络,或者说是一个小型的双向环形总线,甚至(单从拓扑结构上)可以理解为一个2×2的2D-mesh。当然,以这么小规模的互连而言,环形总线的效能比全连接也差不到哪儿去,英特尔很难说服用户,优先考虑四路至强E7服务器,而不是相对廉价的四路至强E5服务器,只能尽量低调处理至强E5-4600系列了。

在四路配置中,至强SP家族中的金牌51系列通过2个UPI(至强E5-4600系列是2个QPI)组成双向环形总线,如图中4个红色实线箭头所示;铂金及金牌61系列通过3个UPI(至强E7家族是3个QPI)组成全连接网络,如图中4个红色实线箭头加上2个红色虚线箭头所示

前面的图说文章已经提到,这种尴尬的局面有望在至强SP这一代得到改变。下一篇文章将重点讨论至强SP家族中的部分特色产品并澄清相关误区,也会发表对新产品命名的一些粗浅看法——但肯定不是重点,因为咱……就不是那爱吐槽的人!