(集微网报道)近日,三星正式发布了新一代2.5D封装技术“I-Cube4”。该技术可以将逻辑芯片(Logic Chip)和4枚高带宽内存(HBM,High Bandwidth Memory)封装在一起。

无独有偶,英特尔也在近期发布了“IDM 2.0”战略,聚焦在下一代的逻辑芯片和半导体封装技术。

对于晶圆厂来说,封装已经从副业变成了主业,新一轮的军备竞赛已经拉开了帷幕。

押注先进封装

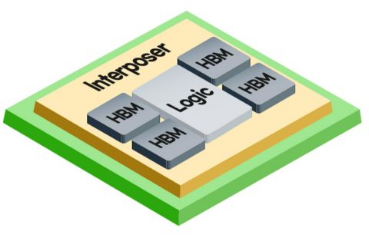

三星本次所推出的封装技术是2.5D封装,属于异构芯片封装,可以实现多个芯片的高密度线路连接。

图 三星I-Cube4封装

通常情况下, 2.5D封装中的芯片并排放置在中介层(interposer)顶部,通过芯片的微凸块(uBump)和中介层中的布线实现互连。中介层通过硅通孔(TSV)实现上下层的互连,再通过锡球(C4)焊接至传统2D的封装基板上。不同类型的芯片最后就完美集成在一起。

2.5D封装是异构集成技术中的一种。那什么是异构集成呢?

按照ITRS(国际半导体技术发展蓝图组织)的定义,就是把分开制造的元器件进行更高层级的组装,而这个集合将可以提供更强的功能性,同时也改善运作的品质。而这里所称的元件,应该要包含裸晶(die)、MEMS装置、被动元件等,或者是被整合至单一封装里的子系统。

ITRS在2014年成立了异构集成的聚焦团队,并在隔年于半导体产业联盟(SIA)的认可之下,与IEEE的电子封装社群(EPS)签属了合作备忘录(MOU),使得异构集成正式成为半导体产业的发展方针。

典型的异构集成案例是Intel的 Agilex系列FPGA,既拥有传统FPGA灵活的可编程性,又结合了现代FPGA基于异构架构的敏捷性。

异构集成是通过封装技术来实现的,除了2.5D封装,还有3D封装、SiP(System in a Package,系统级封装)、PiP(Package in Package)封装等。

2.5D与3D封装也被称作先进封装技术,是晶圆厂在重点发力的地方。据业内人士分析,2.5/3D封装可以提供传统的覆晶封装(Flip Chip)7~8倍以上的I/O数增量,以及更高密度的芯片/模组整合,大幅提升芯片的能效。

NVIDIA与AMD的CPU与GPU、Intel与Xilinx的FPGA等多为2.5D封装,而Intel的Lakefield CPU更是首个以3D封装的CPU。

引领潮流的台积电

在晶圆厂全面介入封装技术之前,整个封装产业已经许久没有重大技术突破,行业的关注点就是降低成本。像覆晶这种业界主流的高级技术,还是在50年前开发的。

转变的节点发生在台积电从三星手中夺下A11,连续吃下苹果A处理器的大单。这其中的关键就是台积电的整合链接与封装部门开创发明了InFO封装,大幅减少了手机AP的厚度,为其他部件腾出了宝贵的空间。

据当时的报道,当时手机AP的厚度曾达1.3、1.4厘米,使用第一代InFO工艺后,厚度直接降到1厘米之下,相当于减厚30%。

其实,在开发InFO封装之前,台积电已经开发了CoWoS(Chip-on-Wafer-on-Substrate)封装,这也是一种2.5D封装。2012年,台积电与Xilinx一起推出了当时最大的FPGA,它由4个相同的28 nm FPGA芯片并排安装在硅中介层上。他们还开发了硅通孔(TSV),微凸点和再分布层(re-distribution-layer:RDL),以将这些构件相互连接。这种封装后来被命名为CoWoS(Chip-on-Wafer-on-Substrate)。

InFO工艺大获成功之后,台积电就在先进封装的策马狂奔。2018年4月,台积电对外界公布了系统整合单芯片(SoIC)多芯片3D堆叠技术。SoIC是一种创新的多芯片堆叠技术,是一种晶圆对晶圆的键合技术。其基于台积电的CoWoS(Chip on wafer on Substrate)与多晶圆堆叠(WoW)封装技术开发而来,可以让台积电具备直接为客户生产3D IC的能力。

2020年4月,台积电宣布封装技术再升级,针对先进封装打造的晶圆级系统整合技术(WLSI)平台,透过导线互连间距密度和系统尺寸上持续升级,发展出创新的晶圆级封装技术系统整合芯片(TSMC-SoIC),除了延续及整合现有InFO及CoWoS技术来延续摩尔定律之外,还在SoC效能上取得进一步的突破。

以3D IC为架构的TSMC-SoIC先进晶圆级封装技术,可以将多个小芯片(Chiplet)整合成一个面积更小与轮廓更薄的SoC,透过此项技术,7纳米、5纳米、甚至3纳米的先进SoC能够与多阶层、多功能芯片整合,可实现高速、高频宽、低功耗、高间距密度、最小占用空间的异质3D IC产品。

晶圆厂争做封装

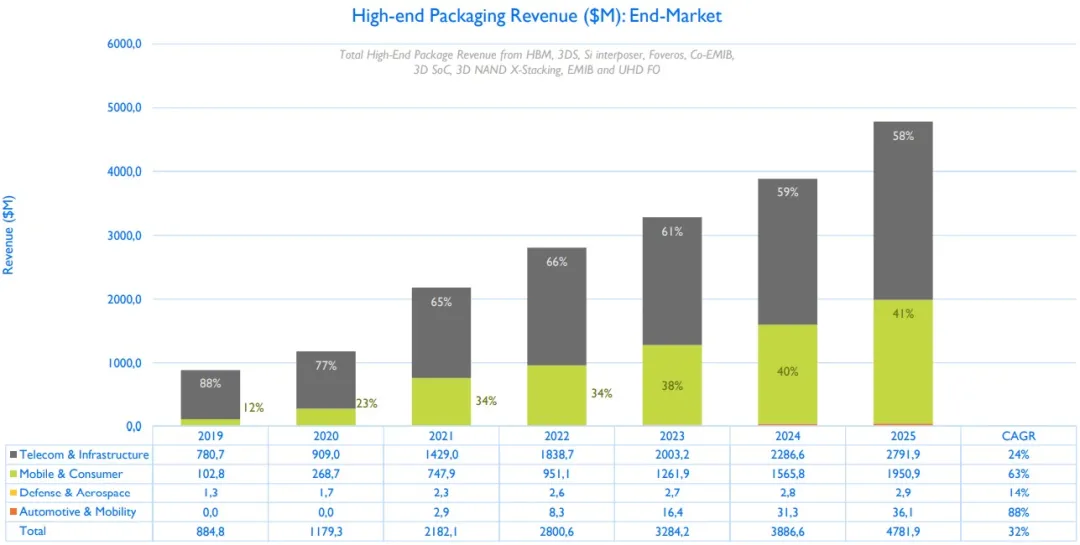

先进封装将有非常大的增长空间。根据Yole的预测,先进封装市场营收将从2019年8.84亿美元增长到2025年的47亿美元,年复合增长率达32%,主要在电信设备和移动消费领域,自动驾驶将是增长最快的领域。

图 先进封装市场增长(源自Yole)

晶圆厂、IDM和封装厂都在竞争先进封装这一高端市场,使得进入壁垒越来越高。而晶圆厂在目前处于非常有利的地位。对此,一位行业专家表示,这些新的芯片堆叠技术需要先进的芯片制造专业知识以及大量计算机模拟来实现精确的堆叠,因此传统芯片封装提供商很难介入。

在先进封装中竞争最激烈的就是台积电、三星与英特尔,而台积电也并非一直领先。曾几何时,英特尔跟三星在“扇出型晶圆级封装”的专利数分别名列全球第二、三,台积连前十名都排不进去。

2015年失去苹果订单之后,三星电子就开始研发先进封装FOPLP技术。2018年,FOPLP技术实现商用,应用于Galaxy Watch的处理器封装应用中。

2018年,三星电子的3D封装技术“X-Cube”开发完成。不同于以往多个芯片平行封装,全新的X-Cube3D封装允许多枚芯片堆叠封装,使得成品芯片结构更加紧凑。而芯片之间的通信连接采用了TSV技术,而不是传统的导线。据三星介绍,目前该技术已经可以将SRAM存储芯片堆叠到主芯片上方,以腾出更多的空间用于堆叠其他组件,目前该技术已经可以用于7nm甚至5nm制程工艺的产品线,也就是说离大规模投产已经十分接近。

英特尔目前也非常依仗先进封装。其曾在2014年首度发表了EMIB(嵌入式多管芯互连桥)封装,这是一种类2.5D的封装,但是不需要额外的工艺,设计也相对简单。

2018年12月,英特尔再推出Foveros 3D堆叠封装技术,可实现在逻辑芯片上堆叠逻辑芯片。数据显示,Foveros技术可以实现50微米左右的凸点间距,每平方毫米集成大约400个凸点,而应用新的混合结合技术,不但凸点间距能缩小到1/5,每平方毫米的凸点数量也能超过1万,增加足足25倍。

在2020年架构日中,英特尔又介绍了最新的封装技术——“混合结合(Hybrid bonding)”。英特尔的官方资料显示,当今大多数封装技术中使用的是传统的“热压结合(thermocompression bonding)”技术,混合结合是这一技术的替代品。这项新技术能够加速实现10微米及以下的凸点间距,提供更高的互连密度、带宽和更低的功率。

台积电也更新了自己的路线图,计划将CoWoS、InFO-R、Chip on Wafer、Wafer on Wafer等先进3D封装技术平台汇整,未来将统一命名为“TSMC 3DFabric”,未来此平台将持续提供介面连结解决方案,以达成客户整合逻辑芯片、高频宽存储器及特殊制程芯片的需求。

目前,市场对先进封装有着强烈的需求,如高性能计算方面,高性能计算机以及高频、高速、高可靠、低延迟、微系统集成等需求推动了FC、2.5D/3D、Fan-Out等先进封装技术的应用。

随着技术的演进,先进封装的发展对半导体产业结构也在产生新的影响。

在传统封装技术向先进封装演进的过程中,曾有人提出“中道工艺”的概念,使传统上前段晶圆制造工艺与后段封装工艺的界线逐渐模糊。而台积电将其封装平台“3DFabric”划分为 “前端”和“后端”封装技术之后,这种划分将进一步打破晶圆制造与封装的界线,对于原有设计、制造、封测的产业结构将产生新的影响。

(校对/Andrew)