【嘉勤点评】炬芯科技的SoC芯片专利,通过修复电路先获取ROM对应的修复信息,在数据错误导致芯片运行异常的情况下,CPU根据修复信息执行ROM中的软件代码,使得该SoC芯片可以正常运行,提高了芯片的生产效率。

集微网消息,近日在南京召开的2021世界半导体大会上,凭借行业领先的经验与技术,炬芯科技股份有限公司有幸再次荣获“IC独角兽”荣誉称号。炬芯的再次上榜,是对其在智能音频 SoC 芯片上取得的成绩的高度认可。

ROM是SoC(片上系统)芯片内部的只读存储器,能够存储代码或数据。目前,绝大多数的SoC芯片是从ROM开始启动,运行ROM中的启动代码,并结合芯片中的其它相关外设配置实现芯片的启动运行。但是由于ROM中的启动代码不能更改,在该启动代码对应的逻辑运算或执行步骤出现错误时,只能将该芯片作废,导致芯片的生产效率比较低。

为此,炬芯科技于2020年11月4日申请了一项名为“SoC芯片、获取修复信息的方法、存储介质及电子设备”的发明专利(申请号: 202011218074.4),申请人为炬芯科技股份有限公司。

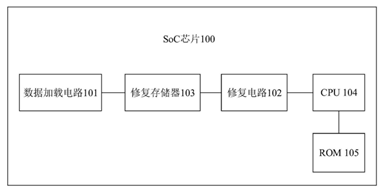

图1 SoC芯片结构示意图

图1为本发明提出的SoC芯片的结构示意图,该芯片100包括数据加载电路101、修复电路102、修复存储器103、CPU 104以及ROM 105。其中修复存储器分别与数据加载电路和修复电路连接,CPU分别与修复电路和ROM连接。数据加载电路的作用是在SoC芯片上电后,从预设存储器获取ROM对应的修复信息,并将该修复信息存储在修复存储器中,然后修复电路从中获取修复信息,最后CPU再从修复电路中获取修复信息,并根据该修复信息执行ROM中的软件代码。

预设存储器可以是ROM外部的存储介质,修复信息预先存储在预设存储器的预设位置,其中预设位置包括多个地址,根据修复信息中的待修复数据,确定需要的地址的个数,在对应的地址中写入该待修复数据。由于预设存储器包括多个地址存储ROM不同错误对应的待修复数据,因此在需要修复ROM中的指定错误时,可以将待修复数据写入该预设存储器中该指定错误对应的地址中,而针对其它未写入待修复数据的地址,可以置为空。这样,修复信息只包括ROM地址中的待修复地址和其对应的待修复数据。

在该SoC芯片上电后,数据加载电路可以从预设存储器获取待修复地址和对应的待修复数据,并将其存入修复存储器对应的地址中,以便修复电路从中获取待修复数据。基于此,数据加载电路还能够获取待修复地址在修复存储器中对应的第一目标地址,将待修复数据写入其中。然后修复电路从第一目标地址中读取待修复数据。最后CPU从修复电路中读取待修复数据,并执行ROM中的软件代码。

简而言之,炬芯科技的SoC芯片专利,通过修复电路获取ROM对应的修复信息,在数据错误导致芯片运行异常的情况下,CPU根据该修复信息执行ROM中的软件代码,使得该SoC芯片可以正常运行,提高了芯片的生产效率。

炬芯科技是中国知名的低功耗系统级芯片设计厂商,一直勇于挑战,热情洋溢,不断为智慧物联网领域提供专业集成芯片。未来,公司将持续发展高品质、高附加值国产智能音频 SoC 芯片,不断提升在国际主流品牌的市场占有率。

关于嘉勤

深圳市嘉勤知识产权代理有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)