本文撰写于2020年07月

【前言】这两年连续参加过两年的“全国大学生集成电路创新创业大赛”(简称“集创赛”),今年的初赛预选结果前几天刚刚公布,果不其然,不出所料,顺利晋级。

我们团队两次选择的赛题均为“基于 Arm 处理器核的SoC 设计”,要求利用利用 Arm Cortex-M3 DesignStart处理器在FPGA平台上构建片上系统(SOC,system on chip)。

报告内容由于大赛方的报告格式要求,省略了许多基础性的知识,许多操作没有详细说明。如果这个系列推文反映良好,计划推出一个系列内容,详细讲解下本次比赛的SOC设计的详细细节和步骤。

报告由 设计概述,基础设计介绍,最简SOC系统搭建,子模块设计,软件设计等部分组成。

下面是报告的正文。

第一部分 设计概述

1.1 设计要求

基于ARM官方提供的开源的M3内核的verilog源代码以及外围设备代码,用来构建简单的SOC系统,并在Arm SoC中实现专门的硬件加速器以提高和优化系统的性能,实现系统对信号的智能处理和分析。

1.2 初期完成目标

我们团队基于ARM Cortex DesignStart m3 内核及其附加代码包,搭建了自定义的SOC系统,并利用BNN(二值神经网络)智能算法,实现了图像的识别和分类的功能。

其次,搭建可以运行智能算法的硬件平台。包括图像数据的获取,存储,显示,预处理等等。以及SOC基础平台的搭建。

然后,将智能算法移植到硬件平台上。通过合理划分软硬件工作。将计算量密集的任务放置到硬件一侧,实现硬件加速。将流程控制类的任务放置到软件一侧,达到软硬件结合的目的。充分利用了异构计算的优势。

1.3 作品特点和优势

- 基于软硬件结合的设计方法,充分利用硬件的并行加速特性和软件的灵活控制特性,使得设计具有极大的灵活性和极快的运行速度。

- BNN(二值神经网络)是在CNN的基础上,对权值和激活值(特征值)做二值化处理,即取值是+1或-1。相比于CNN(卷积神经网络),其使用资源和占用的计算量极大减少。具有 1.加速训练 2.减小权重的值的尺度的影响 3.内存非常小 4.乘法优化等优点。

- 在本设计中,还充分利用EDA工具提供的优势,对SOC系统的搭建做了极大优化。采用块图模块和总线 的设计方法,只需要使用拖动和鼠标连线的方式,即可搭建出SOC系统,加快了SOC系统的搭建,极大方便了开发工作,减轻开发人员的工作。

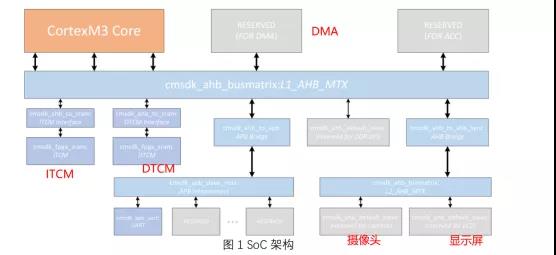

1.4 系统架构图

整个 SoC 基于 CMSDK 开发,从比赛官方提供的模板处修改,添加自定义的功能模块。系统架构图如下:

系统架构

1.5 作品特点

软硬件结合 简化SOC搭建 硬件加速

第二部分 基础设计介绍

1 ARM Cortex DesignStart介绍

ARM Cortex DesignStart 是arm 的一个开放计划,通过免费提供Coretex-M0,Coretex-M3处理器以及相关子系统,使得开发者可以以非常低的成本,更快速地实现定制化的SOC。

2 获得Cortex-M3 DesignStart Eval

Arm Cortex-M3 DesignStart Eval可以在Arm Developer网站上获得。

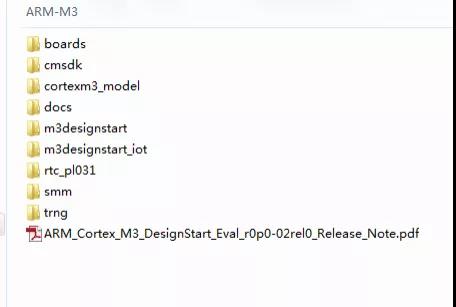

找到Cortex-M3 DesignStart Eval页面链接按钮并点击,注册账户或使用已经注册的账户登录,点击下载链接,将下载得到压缩包解压缩,可以得到我们需要的Cortex-M3 DesignStart Eval。

Cortex-M3 DesignStart

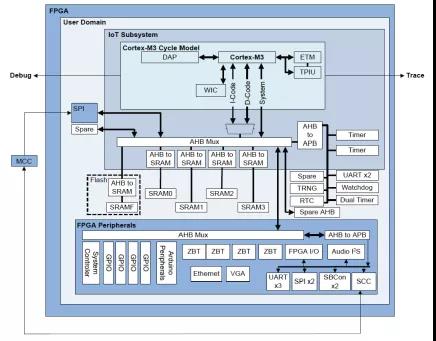

该开发包内包含有 经过混淆的arm-M3 CPU 内核的Verilog源码,常用的一些AHB,APB接口的外设模块,以及基于FPGA的示例工程设计等等。Cortex-M3DesignStartEval包含Cortex-M3CPU、AHB总线矩阵、存储器控制器及其他外设。

示例工程设计

3 AHB-lite总线

AMBA AHB-Lite是面向高性能的可综合设计,提供了一个总线接口来支持Master并提供高操作带宽。

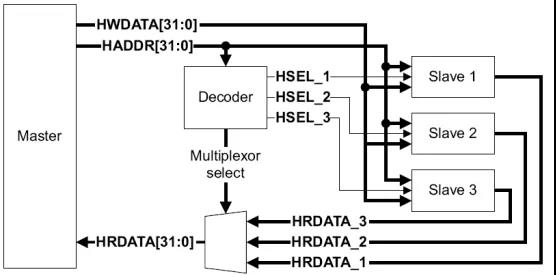

下图是一个具有一个Master的AHB-Lite的系统,包括一个Master和三个Slave。利用内部逻辑生成了一个地址解码器和一个Slave-to-Master多路转换器。

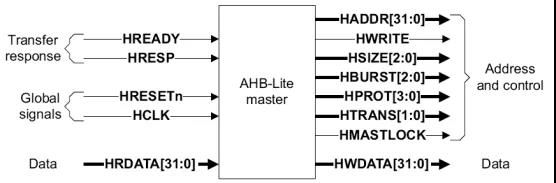

1,AHB-Lite Master

AHB-Lite Master提供地址和控制信息来标识读写操作。下图显示了一个AHB-Lite Master接口。

2,AHB-Lite Slave

AHB-Lite Slave响应系统中由Master发起的传输。Slave使用从解码器引出的选择信号HSELx来控制对总线传输的响应。Slave信号返回Master的信号包括:

- 成功

- 失败

- 等待数据传输

3, 解码器

该部件对地址进行解码,用来提供一个选择信号标识那个Slave进行传输,该部件也提供控制信号进行多路复用控制。

4, 多路转换器

Slave-to-Master多路转换器是Slave到Master的读数据总线和响应控制信号转换的必要部件。解码器提供控制多路转换器的控制信号。

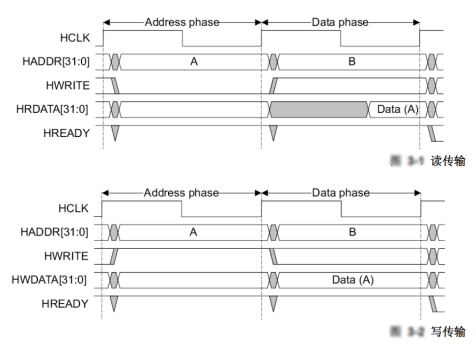

5,传输

AHB-Lite传输包含两个相位:

- Address 保持一个HCLK周期,除非被前一个总线传输进行了扩展

- Data 或许需要若干HCLK周期。使用HREADY s信号来控制完成传输所需要的时钟周期

HWRITE 用于控制数据传输的方向:

- HWRITE为高时,表示是一个写传输,Master向写数据总线HWDATA[31:0]发送数据。

- HWRITE为低时,表示是一个读传输,Slave必须向读数据总线HRDATA[31:0]发送数据。

最简单的传输包含一个地址周期和一个数据周期。如下图所示:

- 在HCLK上升沿后,Master驱动地址和控制信号到总线上;

- Slave在下一个HCLK上升沿采样到了地址和控制信息;

- 当Slave采样到了地址和控制后,便可以开始驱动HREADY做出响应,Master将在HCLK第三个上升沿采样到该响应。

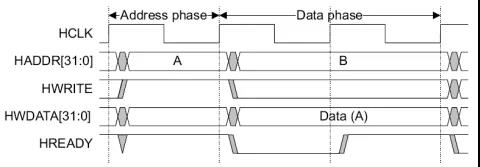

有等待的传输如下图所示:

有等待读传输:

有等待写传输:

等主机发出地址信号后,从机如果来不及接收主机发出的数据,先将HREADY信号置低,直到从机接收完成主机的写数据后,将HREADY信号拉高,通知主机本次传输完成,可以进行下一次传输。

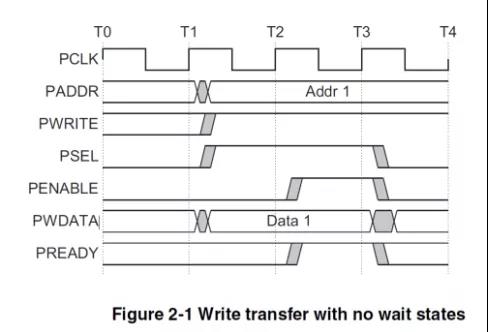

4,APB总线

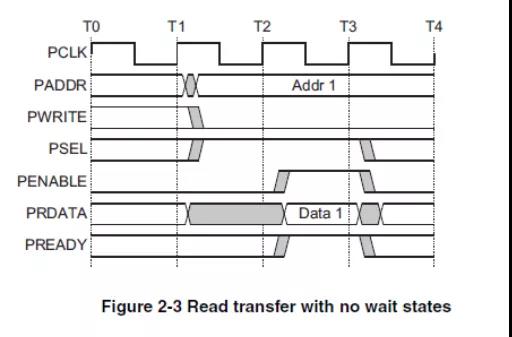

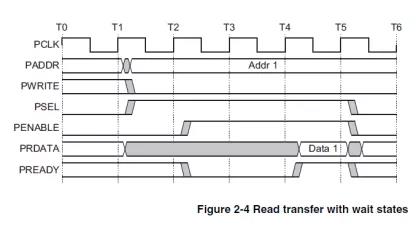

APB 属于AMBA3协议系列,提供了一个低功耗的接口,并降低了接口的复杂性。Apb接口用在低带宽和不需要高性能总线的外围设备上。Apb总线是非流水线结构,每个传输最少消耗两个时钟。同AHB-lite总线一样,apb总线传输时也有无等待和等待两种方式。下图为无等待传输时序图:

在无等待传输中:

- T1周期:写传输开始于地址。设置PADDR,写数据PWDATA,写信号PWEITE和选择信号PSEL。

- T2周期:设置写使能信号PENABLE,和写准备信号PREADY。

- T3周期:PCLK上升沿寄存检测到写准备信号PREADY,检测到为高后,表示传输完成。

- 结束:在传输结束后,使能信号PEABLE和选择信号PSEL信号无效,直到下一次传输开始。

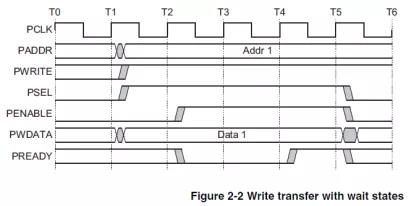

下图为有等待传输时序图:

在有等待传输中:

- T1周期:写传输开始于地址。设置PADDR,写数据PWDATA,写信号PWEITE和选择信号PSEL。

- T2周期:设置写使能信号PENABLE,和写准备信号PREADY。如果从设备还没有准备好,将写准备信号PREADY置低。

- T3周期:PCLK上升沿寄存检测到写准备信号PREADY,检测到为低后,传输等待。

- 延迟:PCLK上升沿寄存检测到写准备信号PREADY,检测到为高后,表示传输完成。

- 结束:在传输结束后,使能信号PEABLE和选择信号PSEL信号无效,直到下一次传输开始。

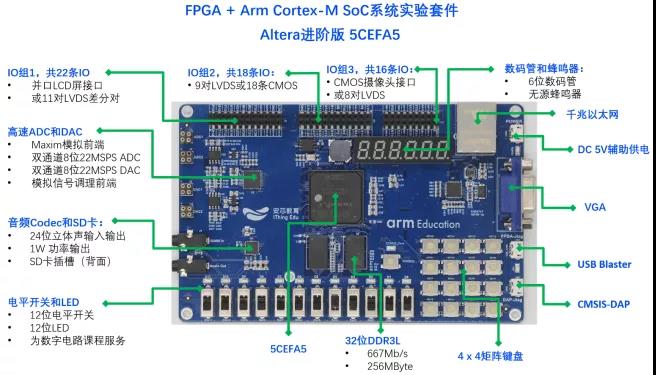

5,使用平台

在此次设计的标牌识别系统中,我们采用了“ARM”杯官方,为我们提供的 Intel - 5CEFA5 板卡进行相关的设计,构建了以板卡为基础的 Soc 系统。统采用的是 正点原子出品的 OV5640 进行图像的采集。

作者:巩文红

原文链接:https://mp.weixin.qq.com/s/C7N1gBNTn69-rwKD9fGSbw

微信公众号:<span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)">更多Arm杯竞赛作品请关注</span></span></span></span>Arm技术竞赛作品分享<span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)"><span class="colour" style="color:rgb(33, 37, 41)">专栏。</span></span></span></span>